Turn on suggestions

Auto-suggest helps you quickly narrow down your search results by suggesting possible matches as you type.

Showing results for

- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: Nucleo F746 ADC DMA noise on the second half t...

Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Nucleo F746 ADC DMA noise on the second half transfer!!!

Options

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-10-06 9:53 PM

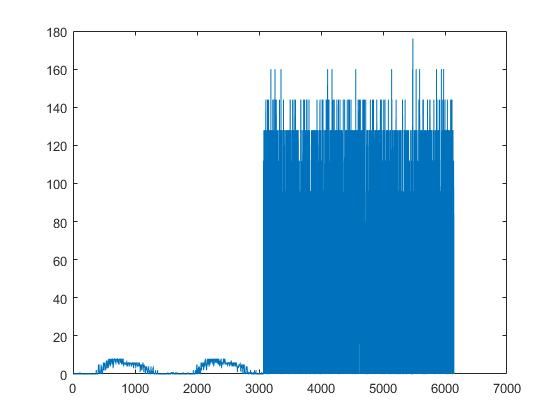

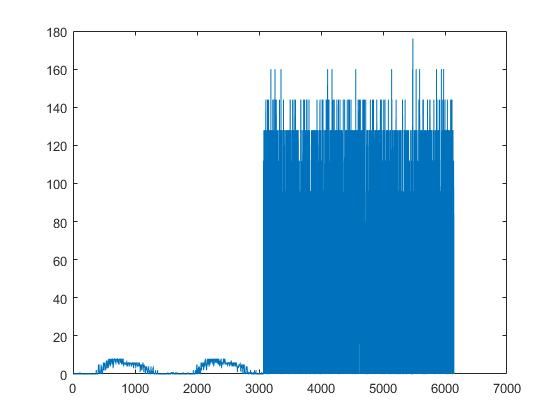

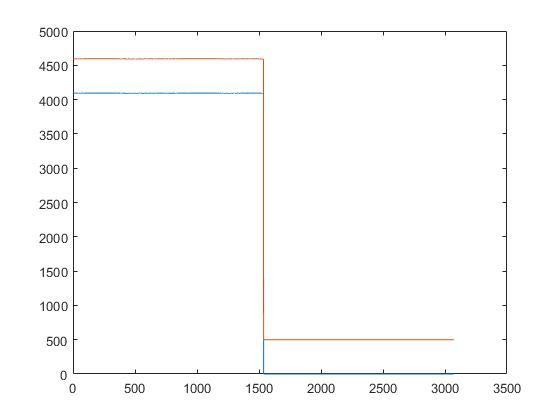

Posted on October 07, 2016 at 06:53 Data shows in the figure is 16bit AD1,AD2,AD1,AD2...../*ADC configed multi-mode*/ multimode.Mode = ADC_DUALMODE_REGSIMULT; multimode.DMAAccessMode = ADC_DMAACCESSMODE_2; multimode.TwoSamplingDelay = ADC_TWOSAMPLINGDELAY_5CYCLES; HAL_ADCEx_MultiModeConfigChannel(&Adc1Handle, &multimode); HAL_ADCEx_MultiModeConfigChannel(&Adc2Handle, &multimode);

Data shows in the figure is 16bit AD1,AD2,AD1,AD2...../*ADC configed multi-mode*/ multimode.Mode = ADC_DUALMODE_REGSIMULT; multimode.DMAAccessMode = ADC_DMAACCESSMODE_2; multimode.TwoSamplingDelay = ADC_TWOSAMPLINGDELAY_5CYCLES; HAL_ADCEx_MultiModeConfigChannel(&Adc1Handle, &multimode); HAL_ADCEx_MultiModeConfigChannel(&Adc2Handle, &multimode);

I tied the ADC in to GND, make the ADC DMA work normal mode, what ever I change the transfer size, the nois is big different just in the middle.

Crazzy!!! Data shows in the figure is 16bit AD1,AD2,AD1,AD2...../*ADC configed multi-mode*/ multimode.Mode = ADC_DUALMODE_REGSIMULT; multimode.DMAAccessMode = ADC_DMAACCESSMODE_2; multimode.TwoSamplingDelay = ADC_TWOSAMPLINGDELAY_5CYCLES; HAL_ADCEx_MultiModeConfigChannel(&Adc1Handle, &multimode); HAL_ADCEx_MultiModeConfigChannel(&Adc2Handle, &multimode);

Data shows in the figure is 16bit AD1,AD2,AD1,AD2...../*ADC configed multi-mode*/ multimode.Mode = ADC_DUALMODE_REGSIMULT; multimode.DMAAccessMode = ADC_DMAACCESSMODE_2; multimode.TwoSamplingDelay = ADC_TWOSAMPLINGDELAY_5CYCLES; HAL_ADCEx_MultiModeConfigChannel(&Adc1Handle, &multimode); HAL_ADCEx_MultiModeConfigChannel(&Adc2Handle, &multimode);

3 REPLIES 3

Options

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-10-06 10:17 PM

Posted on October 07, 2016 at 07:17

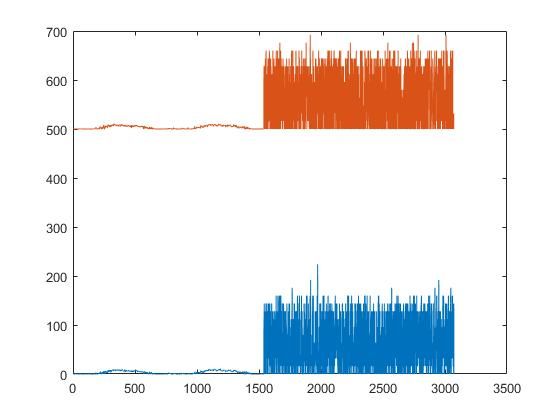

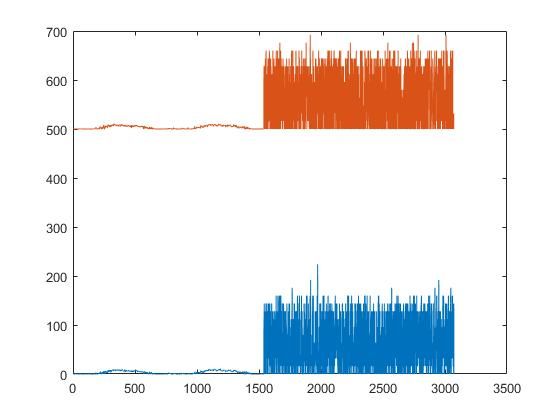

This is two ADC's sepreat display.

Options

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-10-06 10:34 PM

Posted on October 07, 2016 at 07:34

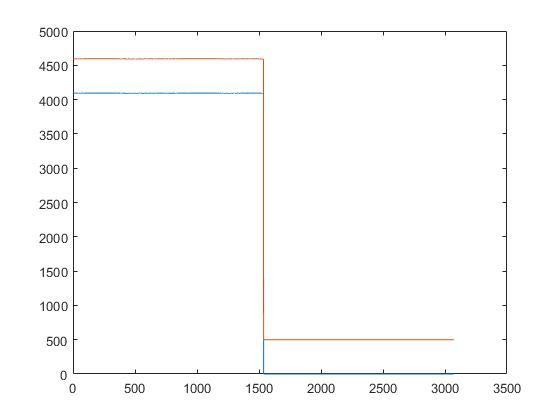

Samples at 1MHz, total ADC time was tested by a timer is 1024*3 uS, so the sample point is correct.

I think the problem reason is the DMA config, need some times to understand! Tie ADC1 to VCC, ADC2 to GND, and memset all data to 0, now the figure is:

Options

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-10-10 9:29 AM

Posted on October 10, 2016 at 18:29

Hi qiyong.mu.001,

The noise may come from spurious charge shots out of AD inputs. Try to eliminate that with the using of ''Averaging'' or ''Digital-signal filtering'' methods described in the application note ''How to get the best ADC accuracy in STM32Fx Series and STM32L1 Series devices'' (page 22 and page 32)-Hannibal-

Related Content

- X-NUCLEO-IHM08M1 Op-amp current calculation in STM32 MCUs Motor control

- I don't know what kind of STM NUCLEO THIS IS in STM32 MCUs Boards and hardware tools

- HAL_PCDEx_PMAConfig Calculation help for Stream of YUY2 Image format. in STM32 MCUs Embedded software

- Bluetooth communication - X-NUCLEO-WB05KN1 & NUCLEO-L476RG in STM32 MCUs Wireless

- How to limit Iq current? in STM32 MCUs Motor control