- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Is ADC sampling clock equal to system clock ?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Is ADC sampling clock equal to system clock ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-12-30 4:40 AM

hello dear forum,

I am trying to take 500 samples from STM32F103RC ADC with DMA

I wanna know if the ADC sampling clock equal to ADC clock or

system clock

for example ;

If I choose ADC clock = P2clock / 8 = 9 MHz

and I choose sampling time 239.5 clock

does this mean that 500 samples last ( 239 * 500 ) / 9000000 = 13 milisecond ?

thank you

#stm32f103-adc-clock- Labels:

-

STM32F1 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-12-30 5:48 AM

There is also the conversion time, which is dependent on the number of bits. The computation is in the reference manual as I recall.

For a specific 'sample rate', in the I want 1 KSps sense, you'd do better configuring a TIM based trigger rather than play games with the sample+conversion numbers and the limited subset of choices that provides.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-12-30 9:39 AM

hello thank you Clive ,

I have the following problem;

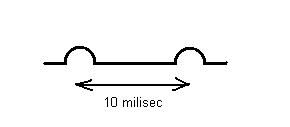

I want measure the peaks in the signal below picture

this is current signal from current transformer output of a power electronics device

the signal is line synchronized as you expect ( but I already have PCB printed and I havenot made an HW interrupt for line zero crossing so I cant synchronize my ADC with the signal )

one idea which came into my mind

is measuring more than 10 milisecond and finding the peak ( or 10 samples from both sides of peak and averaging the result ) with software

my first question ; if I select ADC clock 9 MHz and sampling time 240 clocks and taking 500 samples with DMA - do the 500 samples last about 13 milisecond ?

second ; what other suggestion do you make to me ? how can I measure peak current from above signal picture with only having ADC input in my hand?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-12-30 10:11 AM

The conversion is an additional 12.5 cycles, so 239.5 + 12.5 = 252 cycles

500 samples with a 9 MHz ADC clock would be 14 ms

You can benchmark/qualify these things yourself by toggling a pin in a 500 sample DMA TC interrupt, or timestamp with DWT_CYCCNT

You could shoot to have a 10ms sample buffer, or one split it two halves, that you could process at 100Hz. ie find the peak, should remain in roughly the same spot in the buffer. If you used a TIM trigger, you could advance or r.etard slightly the sample rate to keep it centred, or follow it

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-12-30 11:37 PM

How about filling up a SRAM buffer of ADC sample by DMA in circular mode (no interrupt) and activate the analog watchdog to capture by interrupt the DMA sampling area for analysis of peak value etc... ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-01-05 6:15 AM

hello Clive ,

please I have one more question

if I scan 2 different analog inputs each with 239 cycles sampling time ,

does the sampling times overlap ?

or , do every single channel wait 239 cycles sampling before ADC conversion ?

i.e. for 2 channels conversion 2 x 239 = 478 cycles sampling time in total ?

thank you

- Using VREFINT on STM32C071K8U6 for battery measurement with variable VDDA in STM32 MCUs Products

- LSM6DSO I3C SETDASA in STM32 MCUs Embedded software

- STM32u585 RNG working without enabling HSI48. How? in STM32 MCUs Products

- STM32N6: How to minimize RTC current consumption in VBAT mode? in STM32 MCUs Products

- STM32L476RCT6 – HAL_Delay and UART Blocking Issue on Custom Board in STM32 MCUs Embedded software