- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Generating the desired MCLK frequency in SAI1 for ...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Generating the desired MCLK frequency in SAI1 for 44100 Hz?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-04-18 7:19 AM

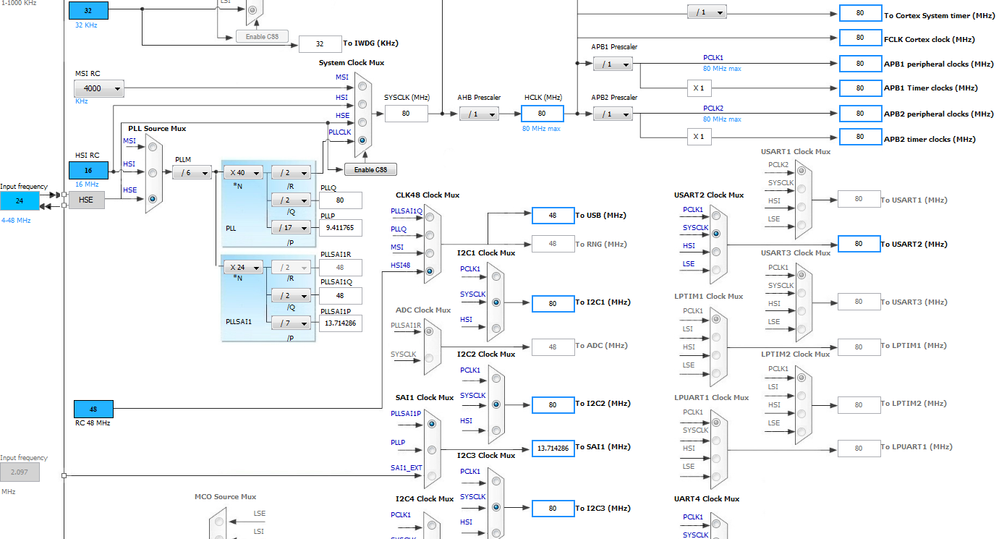

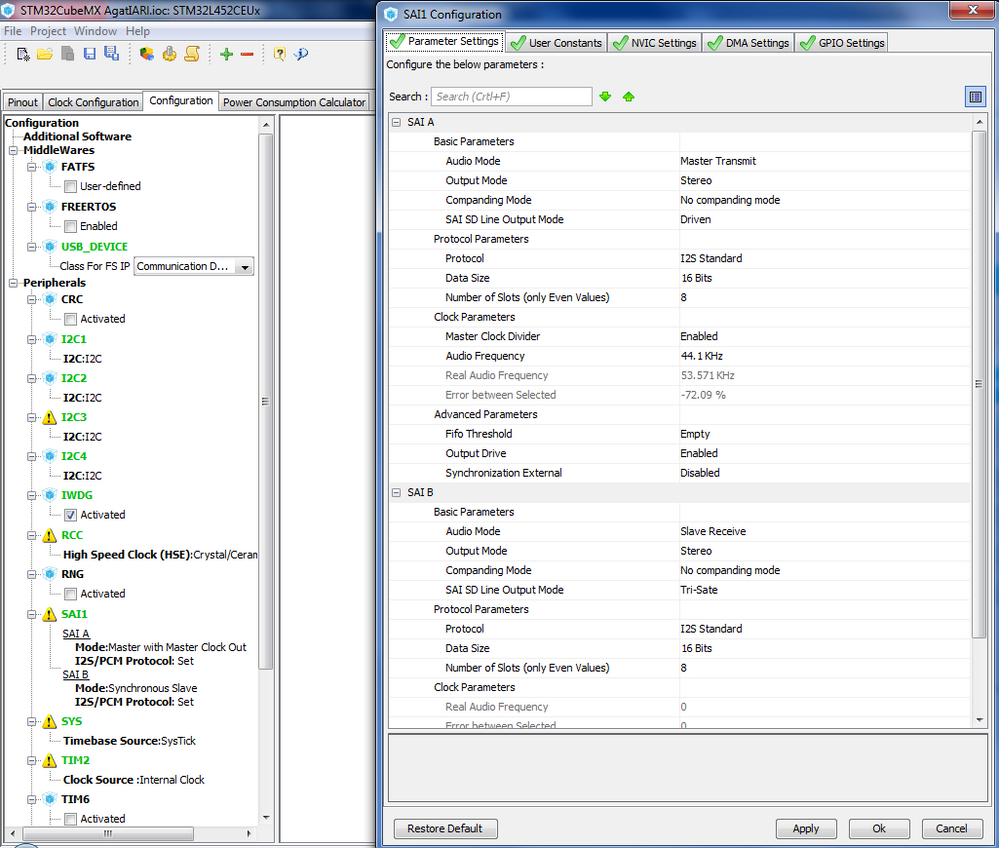

Hello! I'm doing the first project in stm32 and processing audio data is also doing it for the first time. I use stm32L452, clocked by quartz at 24 MHz, and the audio codec TLV320AIC3111. Sampling frequency 44100 Hz, data capacity 16, slots 8. With such initial data, MCLK signal frequency should be 11.2896 MHz, but in CubeMX for SAI1 it is not possible to generate an acceptable frequency with a small error in frequency. The nearest frequency is 13.714286 MHz, then FS will be 53 kHz.

Is it possible to use such a frequency and will this affect the real signal if the TLV320AIC3111 audio codec generates its frequencies from the MCLK for ADC operation? To form 11.2896 MHz, you have to replace the quartz, or is there still a way to form the right frequency? Is it possible to generate only the MCLK signal in the wizard mode, and take the remaining signals (SCK and FS) from TLV320AIC3111, he knows how to make them from MCLK? By the way about the convenience of usingС

ubе

MX. If you change the coefficients of the frequency divider (multiplier), then the automatic recalculation of data inС

ubе

MX by the value of the real frequency and the percentage deviation from the required frequency does not occur. A constant switching of the audio frequency value is required. This is not entirely convenient.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-04-18 4:28 PM

A quick skimming of the TLV320AIC3111 reveals that it has a fractional PLL, i.e. it's easier to generate the required clocks there; the STM32 will then supply 'any' reasonable frequency into the codec's MCLK->PLL_CLKIN, e.g. from MCO or a timer output. The simplest is then to set the codec to master mode (i.e it will then source the bit- and word-clock), and STM32's SAI or I2S use as slave.

Nonetheless, I personally would opt for an 'audio frequency' crystal even if the fractional PLL can source the required frequency, unless there's another frequency-dependent interface on the system. But your preferences may be different from mine.

It's up to you to work out the details, though.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-07-12 6:27 PM

Not sure if OP still needs this but you can generate the PLL you need or very close to it. Change your M divider to 24, your N multiplier to 79 and /R to 7. This outputs a SAIP of 11.285714 which is ~0.3% from your target frequency.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-11-11 9:31 PM

Thank you for trying to help, but your method will not work as the divisor M can not be set to 24.

To address the issue I used the recommendations of waclawek.jan.

- STM32 handshake with MATLAB&Simulink. in Others: STM32 MCUs related

- STM32H503 – ADC trigger shifting from OFF midpoint at duty > 50% in center-aligned complementary PWM in STM32CubeIDE (MCUs)

- CubeMX2: I2S Sample rate calculation does not match value computed in hardware by HAL in STM32CubeMX2 (MCUs)

- Generate 2 PWMs with same frequency & duty, 90 degree phase shift, using one timer in STM32 MCUs Products

- EVALSTDRIVE601 Failure and IGBT Destruction at 600V in STM32 MCUs Motor control