- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- AXI SRAM and SRAMn with DMA in stm32h7x3?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

AXI SRAM and SRAMn with DMA in stm32h7x3?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-01-31 12:21 AM

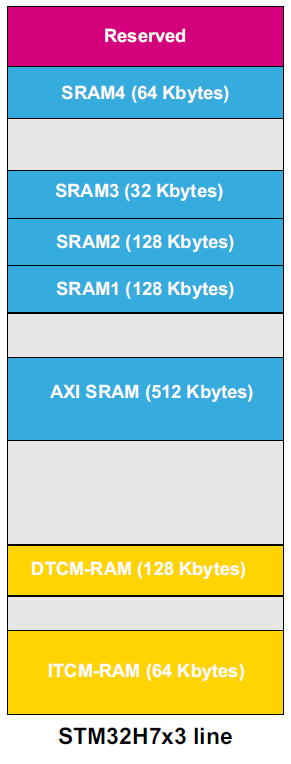

Hello, that's the SRAM of STM32H7x3 microcontroller. I need to receive over 800 kib of data on high speed and place it in RAM via DMA. I read that there's 864 kib of ram here but I was confused to find out that it's segmented like that for some reason. My questions are:

1. What is AXI SRAM and how it's different from SRAM1-SRAM4? In linker configuration file it's used only for HEAP, but I want to declare an array here.

2. In DMA you assign starting address, amount of data and peripheral increment. Is there a way to receive 800 kib of consecutive data that way? The biggest region is 512 kib and it seems that some 'jumps' between the SRAMs are needed to be performed for it to work in the middle of DMA? I worked only with F4 dma, so maybe in H7 there's something different that could allow that?

Thank you!

- Preferred serial interface between 2+ STM32 in Others: STM32 MCUs related

- STM32H7x3 ADC synchronous mode: clock ratio confusion in STM32 MCUs Products

- AzureRTOS Nx_TCP_Echo_Server on NUCLEO-H743ZI2 in STM32 MCUs Embedded software

- STM32H7 execute code in parallel FLASH in STM32 MCUs Products

- AN5215 associated example source code is MISSING in STM32 MCUs Embedded software