- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- ADC trigger with PWM and reading voltage on its st...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

ADC trigger with PWM and reading voltage on its state

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-06 5:38 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-07 1:31 AM

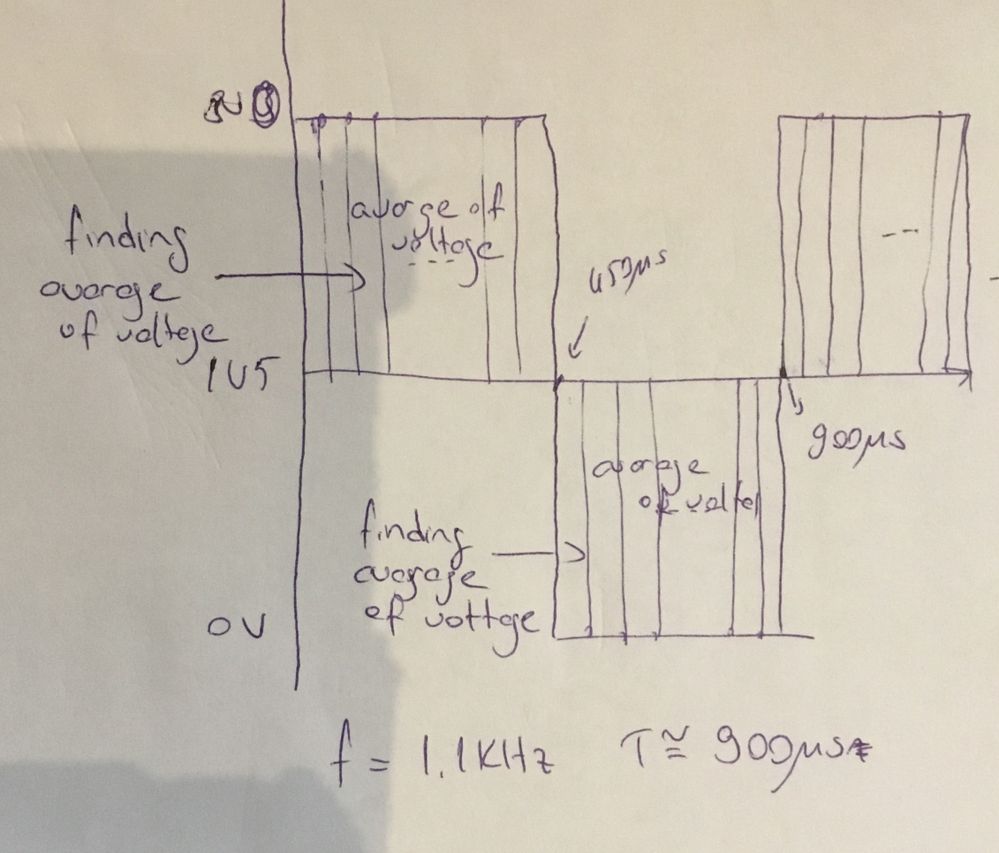

The way you generate the 1.1kHz is by the time it takes to perform all the ADC required conversions, half of them with GPIO low, half of them with GPIO high.

Because the callback is within interrupt, jitter will come if other interrupts delays from time to time yours. (USB, etc...). The PWM frequency is not accurate and it will definitely stop if you put a breakpoint in the callback.

Usually, we try to rely on the HW so that SW is non critical for the signals generation with precise timings.

In this case, we would generate the PWM and check how many ADC samples filled the buffer. Half of them would be for high level, the other half for the low level (exluding the ones near the boundaries).

This way, if the SW stops, the PWM may continue. And if you adjust the ADC sampling time, the number of conversions will vary and you'll still be able to calculate an average.

Make sense? There would be still different scenarios to make it better, this is the way to look at the implementation.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-12 1:41 AM

Thank you @S.Ma

I didn't understand what you meant in second paragraph. Please give me more details?

- « Previous

-

- 1

- 2

- Next »

- How to trigger SPI DMA transfer using TIM12 TRGO on STM32H7 in STM32 MCUs Embedded software

- Flash failures with STM32Progammer_CLI (STM32H7S78-DK, NUCLEO-H7S3L8) in STM32CubeProgrammer (MCUs)

- 3-shunt current calib result not consistent v6.4.1 in STM32 MCUs Motor control

- ADC1 sample from 2 channels with interrupt for conversion ready in STM32 MCUs Products

- How to get PVD working on STM32F1 series in STM32 MCUs Products