- STMicroelectronics Community

- Missing nodes

- missing-QuestionPost

- FlexRay SPC56EL70L5

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FlexRay SPC56EL70L5

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-08-07 11:29 PM

Hello community,

I am asking myself if there is actually anyone running FlexRay on the SPC56EL70L5 Board?

I am currently stuck in the wakeup process (I think that is where I am stuck), because the wakeup pattern does not get send. Does anyone have any experience with that?

Thanks in advance.

Best Regards,

David

Solved! Go to Solution.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-08-11 5:49 AM

Hello David,

1.)

Node B should be

integration_listen

state just like you said. I think you left the part in your code for Node B which set the controller into POC:allow coldstart.

Example:

/***********************************************/

// flexray_allow_coldstart(&Flex1);

sysWaitMilliseconds(90UL);

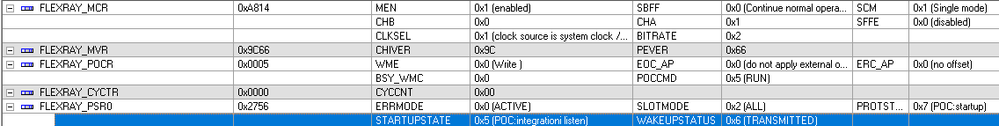

flexray_start_communication(&Flex1);�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?If I dont include the allow_coldstart part the POC ends in the

integration_listen state:

2.)

Could that be that the

FID and HCRC are from different frames sent by different nodes? You should try to configure to usethe keyslot as a startup / sync frame so you know what do you need to see on the scope.

3.)

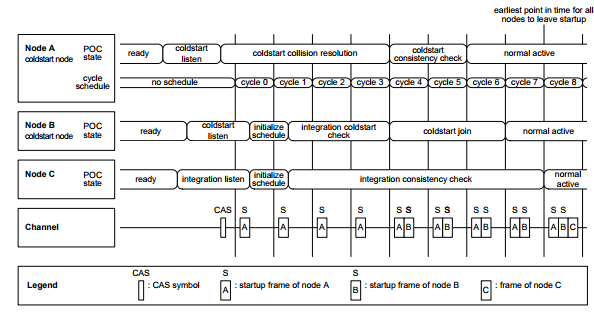

Accordint to the specification: A TT-L coldstart node always finishes the startup after six cycles. What I still dont know how the controller knows that he is a TT-D or a TT-L coldstart node. I think the reason that your Noda A does not stop transmitting his sync frames is because he think that he is a TT-D cs node. Here is the image of the TT-D coldstart startup:

I will give you an update if I find anything out.

As for the rest I am still trying to get the node to send some sync frames soI havent had the chance to test the rest of the protocol

Regards,

Marcell

Ps: Alternatively, I cluster with two coldstart nodes also should be able to start the communication completely. Pay attention to the correct configuration of the startup frames to avoid collisions.

Edit:

Just guessing but it might work:

Set thegClusterDriftDamping to 0 (zero)

A TT-L coldstart node needs to act like the cluster contains two coldstart nodes -> a non-sync node shouldnt recognise the difference between a TT-D and a TT-L cluster. So your coldstart nodes need to transmit two startup frame in each cycle so it would look like there is two coldstart node on the channel. For this you should:

SetpTwoKeySlotMode to TRUE

Set the ID for the second keyslot (Assuming your first keyslot id's is 1, setting it to 2 shall work)

And the action point offset need to calculate in a different way. What is your value for the action point offset?

Edit 2:

It looks like only FlexRay Protocol Specification 3.0 supports the TT-L cluster type and the SPC56xx microcontroller series implements the 2.1 version so you should ignore what i said about the single node startup.

From the spec.:

In clusters consisting of less than three nodes, each node shall be a coldstart node. Each startup frame shall also be a sync frame; therefore each coldstart node will also be a sync node. The parameter gColdStartAttempts shall be configured to be at least two. At least two fault-free coldstart nodes are necessary for the cluster to start up.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-08-16 1:44 AM

Hello Marcell,

I am really amazed how detailed your answers are, thank you so much for that.

1)

Actually, I did not leave it in there, but I realized that I have to disable pKeySlotUsedForStartup on my non-coldstart node but I am still not in integration_listen. I also did not realize that with 2 nodes both of them have to be coldstart nodes. I misunderstood the specification at this point - will try if it works of they both are coldstart nodes.

2)

I think that the sync frames came from both boards. I am not 100% sure but I think that there should be everything correct - I guess there was some misunderstanding on my side. Although I am not sure why it does not show my configured pKeySlotHeaderCRC?

3)

At this point I am a little bit clueless what TT-L or TT-D means and I cannot find anything in the specification.

But I have seen this timing diagram - that is why I am a little bit confused because I am not reaching those states plus I think that some of those startes cannot be seen on the debugger because they happen 'so fast'.

The configuration I got was from a sample program NXP offers with their MPC5 boards becasue they should be pretty similar to my controller as far as I know. But it seems that there are some faults in the configuration or at least I already found a constraint violation. Is there any chance that you could provide some sort of super basic configuration for two nodes? It is kind of hard to configure all those parameters without any help or tools.

My actionPointOffset is 3 and the drift dampening is 1.

Can I simply chance one of those parameters?

Thank you so much for your help - I will try some of your suggestions and will edit this answer.

Best regards,

David.

EDIT 1:

I just double checked - and I actually forgot to remove the coldStartAllowed part, now I am in integration listen.

Now I just ran into an issue that one of the controller seems not to work properly, I am not able to load any programs onto it, but that is a different issue.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-08-16 2:57 AM

Hello David,

Yes I mixed up a little bit the version numbers and I wrote a few false thing about the startup, so to clear it up:

- The nxp and st controllers (as far as I know, even the new ones) implements the 2.1 version of the protocol, NOT the 3.0 so everything I said about the TT-L and TT-D clusters is not implemented and should be ignored. Here is a if you want to read about it (from page 29 and 176).

- The startup needs at least two coldstart nodes, one leading and one following. The following coldstart node should be able to see that the coldstart process has been started on the channel. (maybe delay a bit the transition to the startup state on the following node should work?) The following node should end in the Coldstart Join state before reaching the normal active state

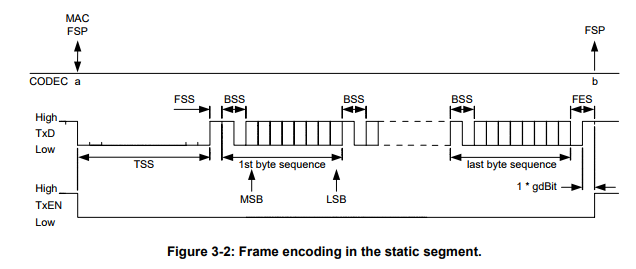

- The two nodes need to have different key slot IDs obviously so they would not be transmitted in the same slot. Keep in mind that what you see on the scope is containing the coding sequences (TSS, FSS, BSS), so if you want to decode the frame segments exclude those.

- For the configuration I use a sample from the Nxp guys as well.

Best Regards

Marcell

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-08-28 1:32 AM

Hello Guys, little update:

I have now checked a few things and I realized something.

I configured the coldstart_attempts to be 10, but in the register FR_PSR1 the field REMCSAT indicates that I have 19 attempts left. Any experience?

EDIT:

Is it at this point actually important that the message buffers are configured correctly?

Best Regards,

David

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-08-29 5:24 AM

I was finally able to bring the bus into POC:normal_active state. It was my fault.

I built a struct for the 30 PCR registers where all the configuration parameter go. These registers are all 16-bit long but I made a mistake which resulted the PCR11 to be longer than 16 bit and therefore all the following parameter where shifted to the back.

Thank you to both of you for your time and help! I really appreciate it.

Best Regards,

David.

- « Previous

-

- 1

- 2

- Next »

- Utilisation of RX Individual Mask Registers in FlexCAN module (SPC56EL70L5) in missing-QuestionPost

- Flexray 2 Node Communication Using Spc560p Microcontroller. in missing-QuestionPost

- i want to ask a question about flexray in SPC56EL60 ,when i use SPC5 studio,i cannot find the driver of flexray,where to find the driver of flexray in missing-QuestionPost

- Flexray to Optical fiber communication?? in missing-QuestionPost