- STMicroelectronics Community

- Product forums

- Interface and connectivity ICs

- Re: SPI DMA SLAVE (M0 Based Micro Controller) DATA...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

SPI DMA SLAVE (M0 Based Micro Controller) DATA SHIFT Problem

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-04 12:57 AM

Hello to all,

am trying trying to interface micocontroller using SPI Protocal.

here , am having 4 slaves and a Master, SLAVES are M0 based Micro controllers where as Master is M3 based micro controller.

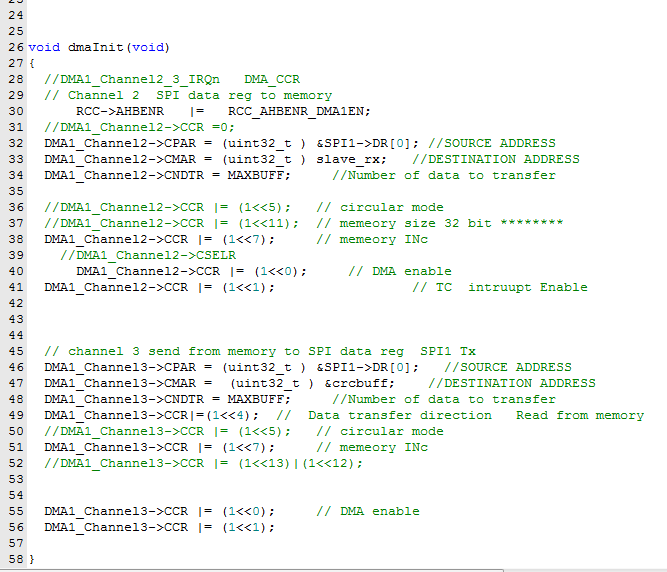

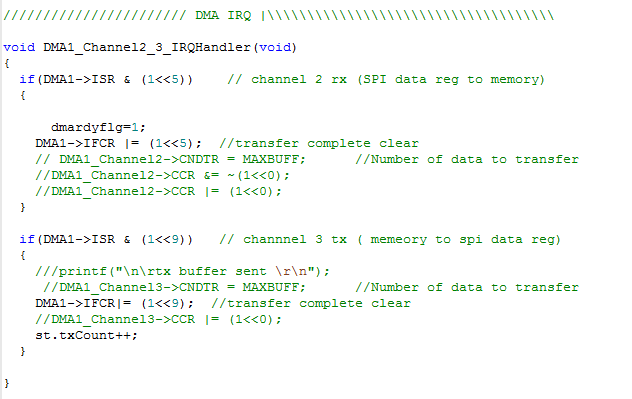

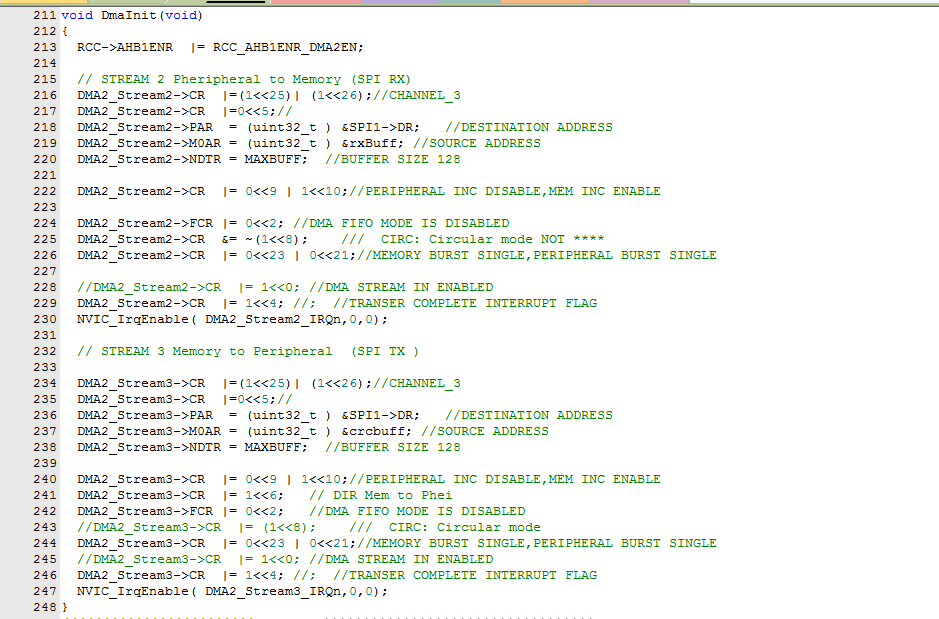

am sending and receving from slaves using DMA .

Both side Master and Slave side am using DMA for transmit and receive.

sending 133 bytes to every slaves interval of 3 milliseconds.

MASTER Clock tested at 1.875mhz and 3.75mhz.

Problem :

problem is in 4th SLAVE it receive shifted data

suppose i sended :

tx from MASTER: 133 bytes

aa cc 80 5d 5e 5f 60

61 62 63 64 65 66 67 68 69 6a

6b 6c 6d 6e 6f 70 71 72 73 74

75 76 77 78 79 7a 7b 7c 7d 7e

7f 84 85 86 87 88 89 8a 8b 8c

8d 8e 8f 90 91 92 93 94 95 96

97 98 99 9a 9b 9c 9d 9e 9f a0

a1 a2 a3 a4 a5 a6 a7 a8 a9 aa

ab ac ad ae af b0 b1 b2 b3 b4

b5 b6 b7 b8 b9 ba bb bc bd be

bf c0 c1 c2 c3 c4 c5 c6 c7 c8

c9 ca cb cc cd ce cf d0 d1 d2

d3 d4 d5 d6 d7 d8 d9 da db dc

dd de db dc a0 9d

RX SLAVE side

db dc a0 9d aa cc 80 5d 5e 5f 60

61 62 63 64 65 66 67 68 69 6a

6b 6c 6d 6e 6f 70 71 72 73 74

75 76 77 78 79 7a 7b 7c 7d 7e

7f 84 85 86 87 88 89 8a 8b 8c

8d 8e 8f 90 91 92 93 94 95 96

97 98 99 9a 9b 9c 9d 9e 9f a0

a1 a2 a3 a4 a5 a6 a7 a8 a9 aa

ab ac ad ae af b0 b1 b2 b3 b4

b5 b6 b7 b8 b9 ba bb bc bd be

bf c0 c1 c2 c3 c4 c5 c6 c7 c8

c9 ca cb cc cd ce cf d0 d1 d2

d3 d4 d5 d6 d7 d8 d9 da db dc

dd de

so as you seen how last 4 bytes came in front

am using 4 chip select lines for 4 salves

*** when i test with 3 slaves it work perfect ***

after adding 4 th slave this problem starts

Initially all slaves work correctly bt after some lakhs of tx and rx it SLAVE 4th get errors

so how to correct it.

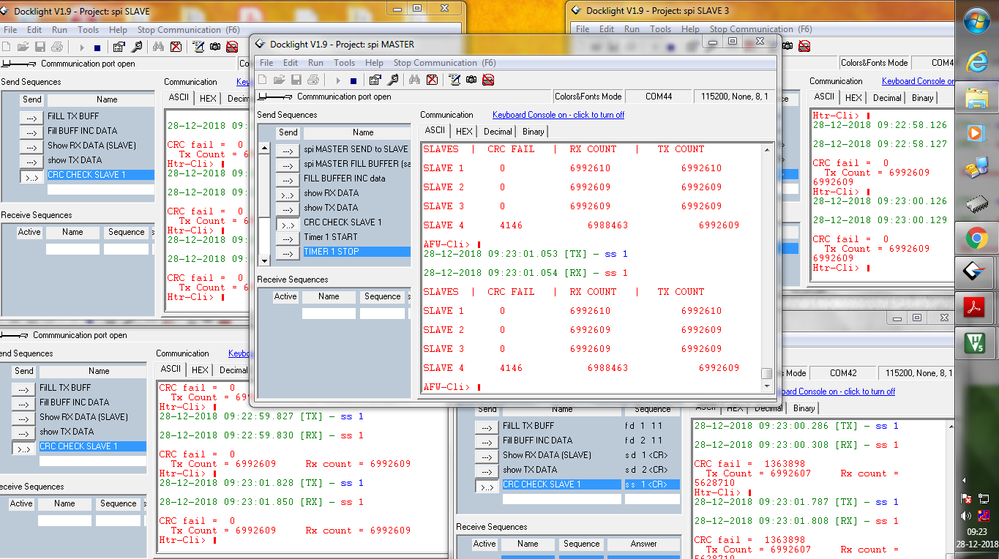

in RIGHT LAST CORNER is SLAVE 4

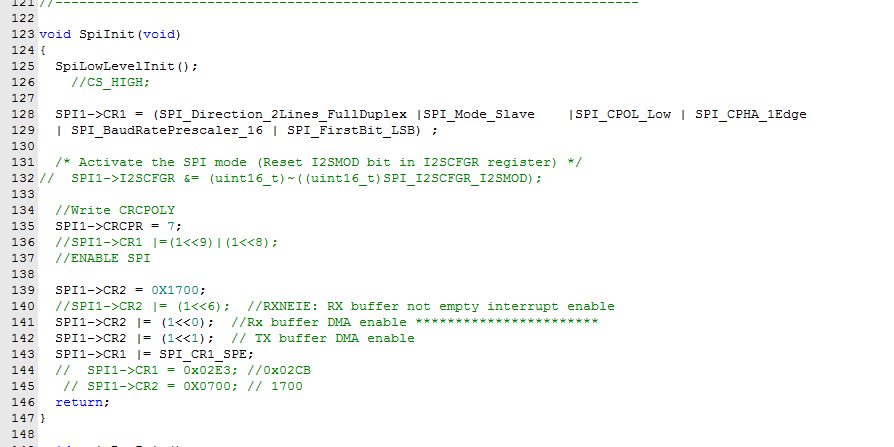

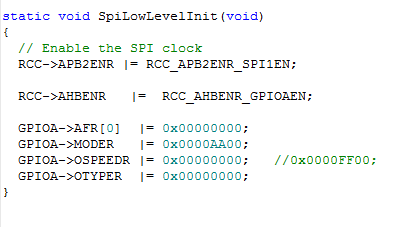

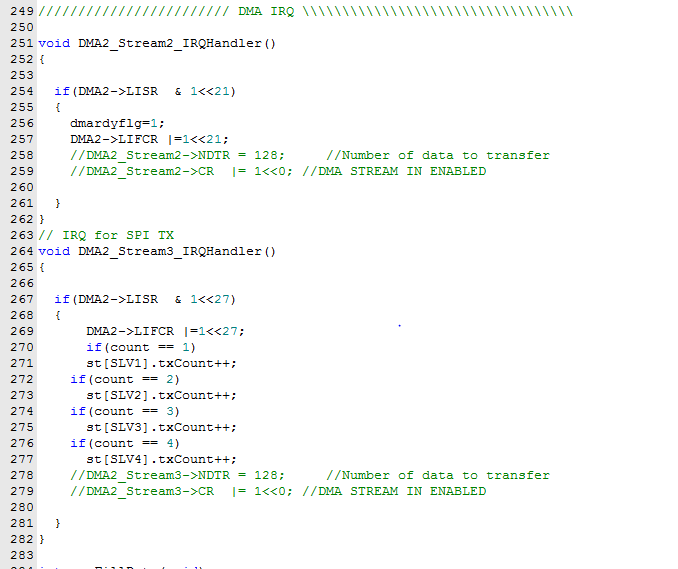

M0 SLAVE SPI AND DMA CONFIG

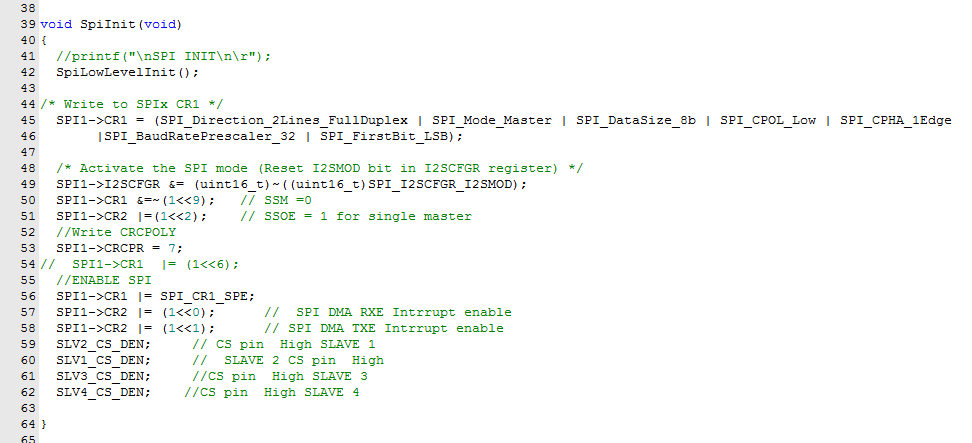

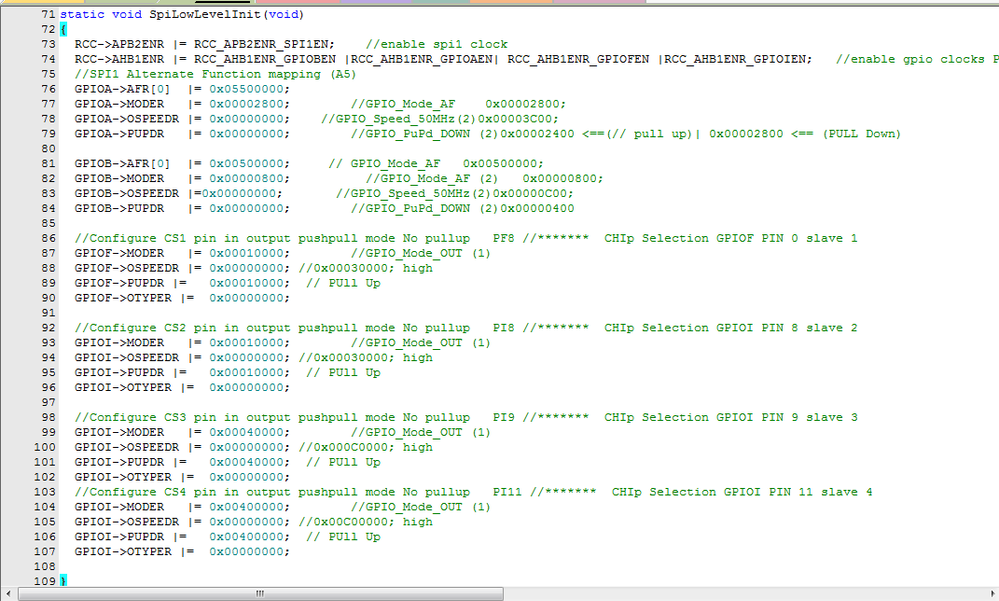

**** MASTER SIDE SPI AND DMA CONFIG ****

below:

(Cortex M3) MASTER stm32F20x

Thanks in advance.

Solved! Go to Solution.

- Labels:

-

SPI

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-04 04:28 AM

An SPI transaction is complete once its RXNE flag is set. (not TXE).

Use NSS rise/fall edge to reset/reconfigure the SPI for the next transfer.

Add some slight delay on master side between NSS toggle and SCK data activitiy start.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-04 02:53 AM

Does this MCU SPI has FIFOs?

Hard to see the captures. Are the SPI Slave MCUs using DMA in CYCLIC mode?

Are you using EXTI on the NSS slave pin?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-04 03:05 AM

hello,

captures are clear when you click or zoom them

No CYCLIC mode am using

no EXTI on the NSS slave pin

slave spi controller is handle itself Slave Select pin

In master side am makeing Chip Select Pin high to low when to select a slave

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-04 04:28 AM

An SPI transaction is complete once its RXNE flag is set. (not TXE).

Use NSS rise/fall edge to reset/reconfigure the SPI for the next transfer.

Add some slight delay on master side between NSS toggle and SCK data activitiy start.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-04 04:35 AM

ok, let me try

after implementing and testing i will tell its helping or not.

thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-04 11:20 AM

The most important to remember in SPI mode is that the TXE will occur just when you write the data register, while the RXNE will occur once all the clock bits have been actually been transiting on the SPI bus. Going higher level, the DMA RX usually is used as possible interrupt source, never the DMA TX which is only used in master mode to generate the required number of clock pulses. (in 4 wire mode which is the default reference for me).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-04 08:27 PM

ok thanks ,

bt still i want to know why it works perfectly with 2 or 3 or 5 slaves

not with 4 slaves.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-04 11:16 PM

This would be debugging, I've got 1 master with 12 slaves MCU running on 12MHz SPI with 2048 bytes packet every 3 msec with no errors over hours in one of my hobby project.

First, have you checked it's not a timing issue?

For example, sequence swap 4 and 2 and observe where the bug shows up.

If there are other possible interrupts that could happen in master or some slaves generates this side effect.

Second, check if the memory addressed by the DMA contains the right range and data, When there is wrong memory location, you may generate wrong data fillup and old one remains.

By not using NSS to synchronise the slaves to the master is like implementing an I2C bus without the START/STOP bits.

Debugging master - slave SPI is a bit more tricky as you have to debug on both sides. Also check if the first, second talk between master ans slave starts right or wrong.

A good way to debug is to put a transaction counter in the message you are sending.

Ideally, also put the intended slave target number, this way, you can breakpoint conditionality and get some clues for debugging.

Good luck!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-04 11:18 PM

ok thanks

i will do multiple test .

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-07 03:03 AM

hello,

as you told to check Chip select Pin

Use NSS rise/fall edge to reset/reconfigure the SPI for the next transfer

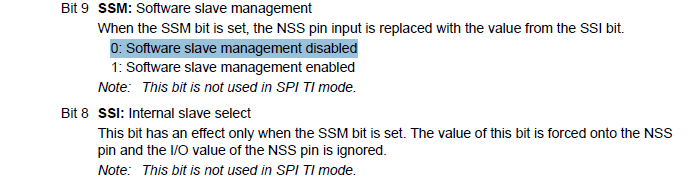

when am using this config : SOFTWARE SLAVE MANAGEMENT DISABLED

so my Question is that how i can see/ Check my Chip Select pin is high or low ?

if you having some codes so, please share with me .

- stm32l4r9aii6 interrupt issue in STM32 MCUs Products

- USB Implementation from scratch/first principles in STM32 MCUs Embedded software

- STM32G070RB Boot problem and Option bytes not setting right. No option for Boot Lock in code. in STM32 MCUs Products

- STM32H7: SPI problem with SPI_RXDR in STM32 MCUs Products

- Problems controlling SK6812RGBW/Neopixel with STM32H7 in STM32 MCUs Products