Turn on suggestions

Auto-suggest helps you quickly narrow down your search results by suggesting possible matches as you type.

Showing results for

- STMicroelectronics Community

- Product forums

- Analog and audio

- STA321MP INQUIRIES

Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STA321MP INQUIRIES

Options

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-07-08 5:05 PM

Posted on July 09, 2016 at 02:05

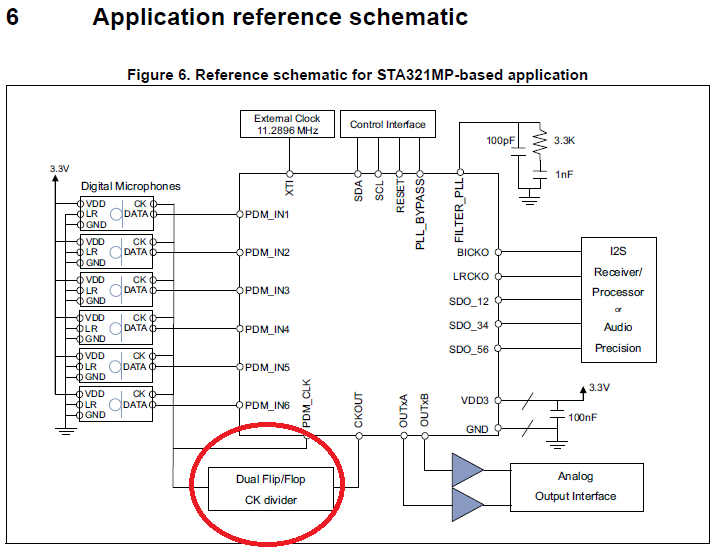

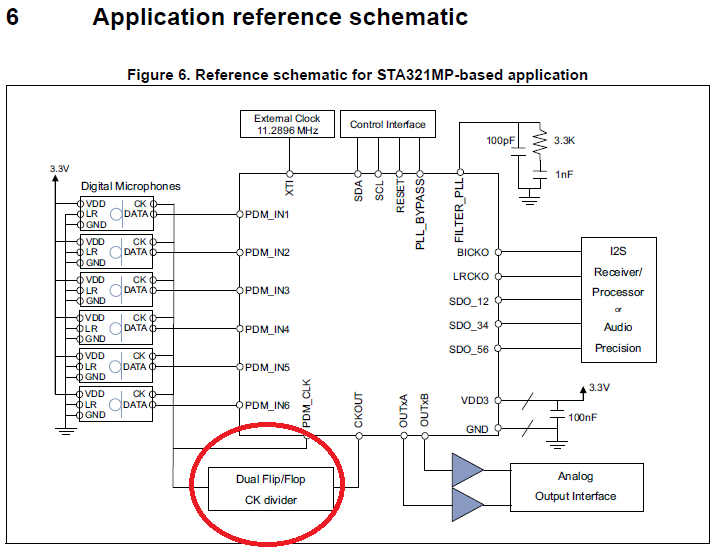

1) What is main function or porpouse of the Dual Flip Flop than can be seen in the image below? Is this one located inside the STA321MP or is and external component?

1) What is main function or porpouse of the Dual Flip Flop than can be seen in the image below? Is this one located inside the STA321MP or is and external component?

Greetings, currently i am working on my thesis and i am planning to use this IC (STA321MP) for my proyect as it fits the requierments that i am proposing for it, but there are some specific points and doubts that i can not solve along side the data sheet so that�s why i am writing this request. The questions goes as follows:

1) What is main function or porpouse of the Dual Flip Flop than can be seen in the image below? Is this one located inside the STA321MP or is and external component?

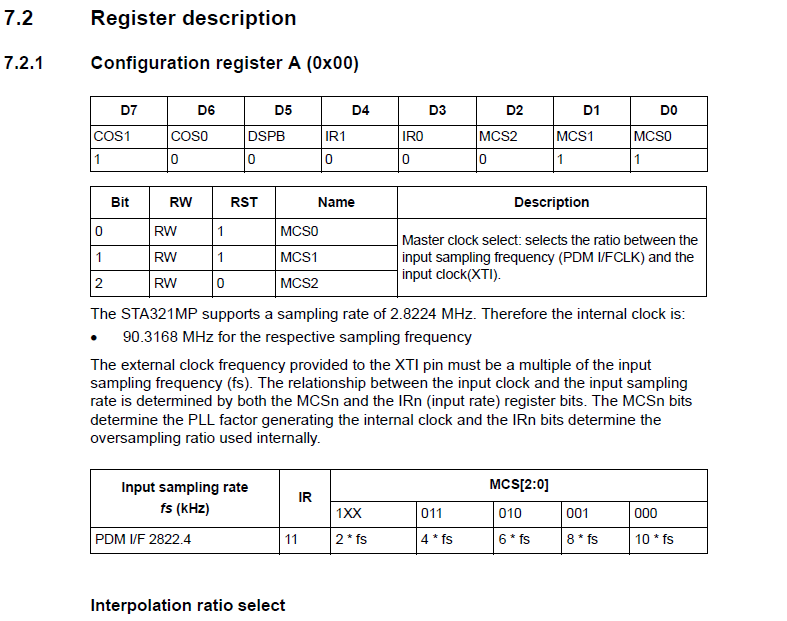

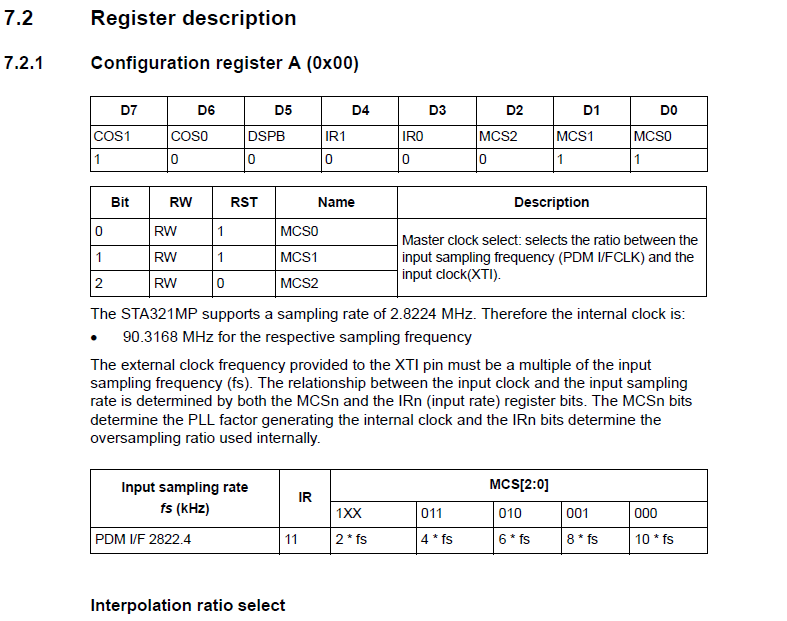

1) What is main function or porpouse of the Dual Flip Flop than can be seen in the image below? Is this one located inside the STA321MP or is and external component? 2) How does the PLL (phase locked_loop) ratio is program orr set? is not very clear on the data sheet.

3) What is the purpouse of the PLL_BYPASS pin ? Its functionality overall. 4) The subject around the PDM_CLK and how to obtain the CKOUT frequency is not very clear for me, could you please help me to understand it in a simpler way. 5) The sampling frequency that is said on the datasheet of the STA321P supports a 2.8224Mhz frequency with a internal fixed clock of 90.3168 hz, Is it a fixed default value? is it variable or i can be set apart? Time is of scense for me, i would apreciate any help you can provide me. Thanks before hand. Good Day. #sta321mp #audio-processing

Labels:

- Labels:

-

Audio

-

Operational Amplifiers

This discussion is locked. Please start a new topic to ask your question.

1 REPLY 1

Options

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-07-10 11:06 PM

Posted on July 11, 2016 at 08:06

Hello Carlos,

The STA321MP is an audio product. In order to have a more appropriate answer, I recommend you to create a similar post in the audio section. Here is ahttps://my.st.com/public/STe2ecommunities/analog/Lists/Audio%20Amplifiers/AllItems.aspx

. Sorry for the inconvenience, and don't hesitate to come back for questions related to op-amps/comparator or current sensing products. Regards, Sylvain

Related Content

- Inquiry on OpenPLC Yocto Layer/Recipe Support for STM32MP157-DK2 in STM32 MPUs Embedded software and solutions

- STM32WBA55CGU6 Availability Inquiry in STM32 MCUs Wireless

- Inquiry about Equivalent Gate Count and FIT Data for STM32H750VB in STM32 MCUs Products

- STM32MP2 Hantro VPU V4L2 H.264/VP8 Encoding & Decoding Usage Inquiry in STM32 MPUs Products and hardware related

- Inquiry about SIMPLIS or SPICE model for STDRIVEG600 in Power management