Turn on suggestions

Auto-suggest helps you quickly narrow down your search results by suggesting possible matches as you type.

Showing results for

- STMicroelectronics Community

- Product forums

- STM8 MCUs

- TIM1->CCMR1 erratic operation

Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

TIM1->CCMR1 erratic operation

Options

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-06-19 5:14 PM

Posted on June 20, 2014 at 02:14

Someone, please help, I am really stumped.

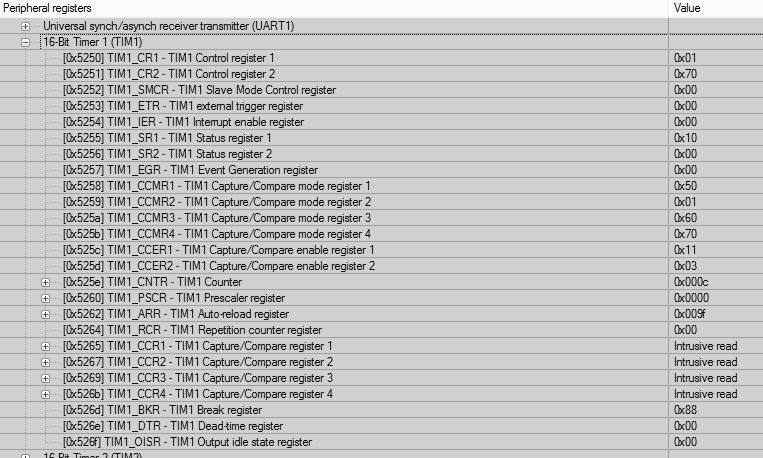

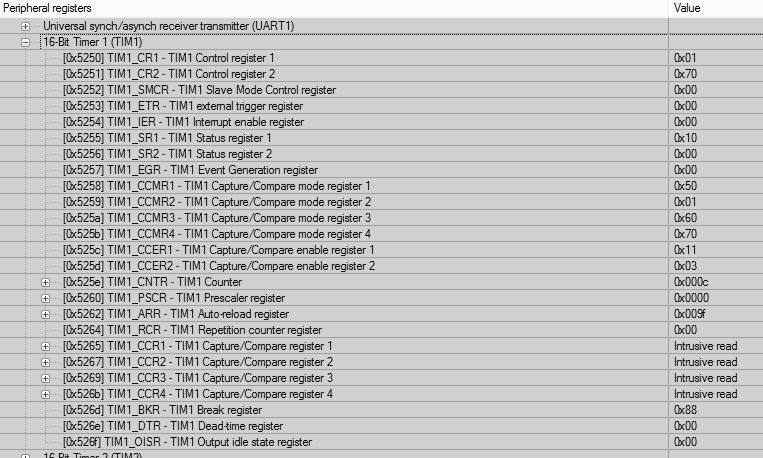

Is there some secret process not mentioned in the ref manual for writing to the CCMR1 register?For any single code sequence the behavior is repeatable even if wrong; but if I change up the code, the behavior changes.I am trying to force the output pin by writing 0x50 and 0x40 to the CCMR1 register. Often I can see the pin go high momentarily but then go back low. Sometimes the value doesn't go into the register - reads back as 0x00. When I set the GPIOC->ODR bit, the pin goes high - it's not supposed to when the counter channel is enabled? Is it? Earlier in the code I have the channel working properly in compare mode with TIM1->CCMR1=0x18.At start up, I write, TIM1->BKR = 0x88. TIM1->CCER1=0x11Should the SR1 bit be set for that channel? It isn't.I have tried writing the register multiple times with delay between.I have tried toggling the CC1E bit with no effect.I have tried toggling the CC1P bit with no effect.But writing to GPIOC->ODR DOES toggle the pin - but it shouldn't.Any help would be greatly appreciated.

This discussion is locked. Please start a new topic to ask your question.

0 REPLIES 0

Related Content

- Speeding up access to shared memory on dual-core STM32 in STM32 MCUs Products

- TouchGFX - How to detect and recover from reset/failure during operation? in STM32 MCUs TouchGFX and GUI

- VBAT on STM32U5G9J-DK1 in STM32 MCUs Products

- SD card operation on STM32N6570-DK in STM32 MCUs Embedded software

- STM32N6 cache operations inside noncacheable memory in STM32 MCUs Embedded software