Turn on suggestions

Auto-suggest helps you quickly narrow down your search results by suggesting possible matches as you type.

Showing results for

- STMicroelectronics Community

- Knowledge base

- STM32 MCUs

- ADC interleaved mode (1/2): How to improve ADC sam...

Options

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Email to a Friend

- Printer Friendly Page

- Report Inappropriate Content

ADC interleaved mode (1/2): How to improve ADC sampling rate

Bartosz BORYNA

ST Employee

Options

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Email to a Friend

- Printer Friendly Page

- Report Inappropriate Content

on

2020-12-02

1:54 AM

- edited on

2025-08-01

4:08 AM

by

![]() Laurids_PETERSE

Laurids_PETERSE

This series of articles will provide you with:

- Tips&tricks on how to implement ADC interleaved mode to double equivalent sampling rate

- ADC interleave mode details from practical point of view

- Info on DMA data transfer using ADC Common Data Register

- How to increase ADC sampling rate

Article part 2 available here

1. ADC interleaved mode description

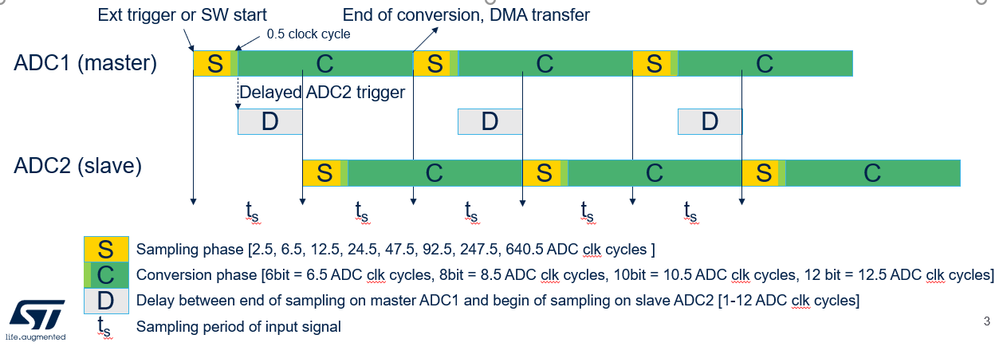

- It allows performing faster ADC conversion by using two ADCs on the same input channel

- Once sampling phase is finished on “master” ADC1, after programable delay D , “slave” ADC2 is triggered by ADC1 and can start its sampling phase on the same pin

2. ADC interleaved mode DMA transfer

- After ADC2 conversion finish, DMA is triggered to perform a data transfer from ADC_CDR register (Common Data Register for ADC1, ADC2) to the buffer and end of conversion flags are cleared for both ADCs

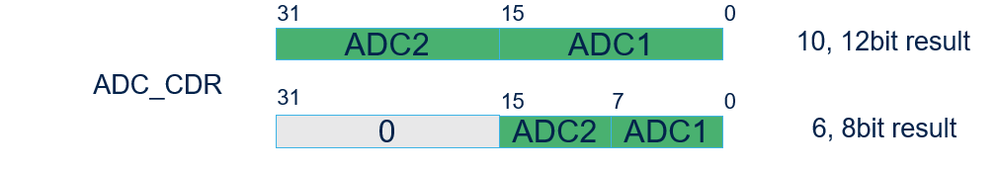

- Depending on the selected ADC resolution content of ADC_CDR register can have different structure:

- User is responsible for proper timing programming of ADC2 in order to have data ready for ADC1 and ADC2 at ADC1 end of conversion

3. App analyze

- Acquire data in ADC interleave mode @ 12-Bits resolution and high sampling rate

- ADC input fast channel is used, see DS: PC0,PC1,PC2,PC3,PA0 can be selected as fast channels, see also AN2834 for SAR ADC sampling diagram and related details.

- Number of samples to acquire: 40,

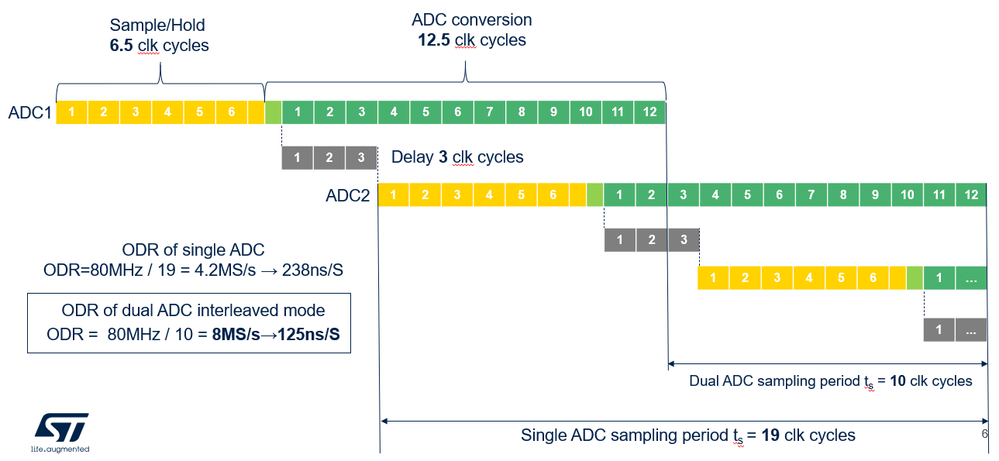

- ADC clock: synchronous 80MHz (highest possible STM32L476 SYSCLK frequency),

- Sample/Hold period T_SMPL = 6.5 clock cycles following given R_AIN/C_AIN (worst case),

- Delay of slave ADC trigger: 3 clock cycles; T_SAR = 12.5 clock cycles (12-Bits),

- Single ADC ts = T_SMPL + T_SAR = 19 clock cycles → trigger of slave ADC after 6.5+0.5+3=10 clock cycles, Output Data Rate of single ADC, ODR= 80MHz / 19 clock cycles = 4.2MS/s,

- ADC input signal acquisition every 1s, print out data in CSV text format: DMA transfer in one shot mode using ADC_CDR output data register, redirect printf stream to UART

Article part 2 available here

Labels: