- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- STM32F429 interfacing- LTDC, DMA2D and SDRAM

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F429 interfacing- LTDC, DMA2D and SDRAM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-15 1:48 AM

Hi,

We are using Tianma’s - TM070RVHG01 TFT in our design with STM32F429 processor working at 168 MHz frequency. We are using EmWin Library on RTX operating system with LTDC support. We are statically storing the required ARGB format in external SDRAM. The data is loaded from SDRAM to LTDC (STM32F4 LCD Controller) using DMA2D and FMC interface (Flexible Memory Controller – Working at 168/2 MHz).

The colour configuration is ARGB8888 and driver configuration of EmWin is GUI_LIN_32.

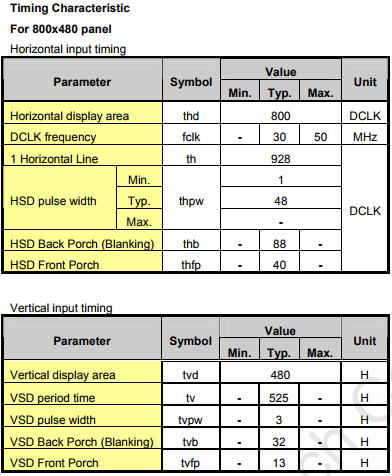

From datasheet we understand that minimum DCLK is 28 MHz. So we are setting the DCLK as 28 MHz and calculated the parameters for LTDC which are as follows.

From Datasheet

HSYNC Width

20

VSYNC Width

3

HBP

46

VBP

23

Active Width

800

Active Height

480

BVBP

23

HFP

210

VFP

22

Calculated Value for LTDC Register

HSW

19

VSH

2

AHBP

65

AVBP

25

AAW

865

AAH

505

TOTAL W

1075

TOTAL H

527

Issue :

- We are find Tearing Effect in the display and the same time if we probe we could find FIFO underrun issue. Please let us know the above setting as correct for 28 MHz DCLK.

- When we reduce the DCLK to 24 MHz the display is stable but we are facing flicker issue.

Is there any solution for the above problems without using multi buffer support. Also could you send sample source running on any RTOS for reference

Thanks and Regards,

Manoj

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-30 7:59 AM

Try 180 MHz

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-30 5:32 PM

800*480*60=23Mgz

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-04-01 7:23 PM

Dear every body,

Chandran.Manoj

Iare using LCD TFT 7 inch 800x480

in our design with STM32F746BTG6processor working at200 MHz frequency.We are usingSTemWinLibrary on RTOS operating system

with LTDCsupport.GUIBuilder.exe software will generate gui data.

I are statically storing the required ARGB format in external SDRAM.

The data is loaded from SDRAM to LTDC (STM32F7 LCD Controller)using DMA2D and FMC interface(Flexible Memory Controller – Working at 200/2 MHz).

Timing LCD TFT 7 inch from datasheet:

http://www.buydisplay.com/download/ic/OTA7001A.pdf

About frequency in system:

- SDRAM: 100MHz, use same bus data 16bit with other device. Examples:nor flash.

/* Timing configuration for 100Mhz as SD clock frequency (System clock is up to 200Mhz) */

Timing.LoadToActiveDelay = 2; Timing.ExitSelfRefreshDelay = 7; Timing.SelfRefreshTime = 4; Timing.RowCycleDelay = 7; Timing.WriteRecoveryTime = 2; Timing.RPDelay = 2; Timing.RCDDelay = 2; sdramHandle.Init.SDBank = FMC_SDRAM_BANK1;sdramHandle.Init.ColumnBitsNumber = FMC_SDRAM_COLUMN_BITS_NUM_9;

sdramHandle.Init.RowBitsNumber = FMC_SDRAM_ROW_BITS_NUM_13;sdramHandle.Init.MemoryDataWidth = SDRAM_MEMORY_WIDTH;

sdramHandle.Init.InternalBankNumber = FMC_SDRAM_INTERN_BANKS_NUM_4; sdramHandle.Init.CASLatency = FMC_SDRAM_CAS_LATENCY_2; sdramHandle.Init.WriteProtection = FMC_SDRAM_WRITE_PROTECTION_DISABLE; sdramHandle.Init.SDClockPeriod = SDCLOCK_PERIOD; sdramHandle.Init.ReadBurst = FMC_SDRAM_RBURST_ENABLE; sdramHandle.Init.ReadPipeDelay = FMC_SDRAM_RPIPE_DELAY_0;- LTDC: 2 MHz.

PeriphClkInitStruct.PeriphClockSelection = RCC_PERIPHCLK_LTDC;

PeriphClkInitStruct.PLLSAI.PLLSAIN = 192; PeriphClkInitStruct.PLLSAI.PLLSAIR = 5; PeriphClkInitStruct.PLLSAIDivR = 2; HAL_RCCEx_PeriphCLKConfig(&PeriphClkInitStruct);While I'm getting data in norflash, LCD have prolems is flickering.

I know that LTDC will gennerate data to LCD automatically after SDRAM refresh, isn't it?

What is solution to hold data on LTDC while other device use bus data of SDRAM (16 bit data)?

Can you tell me solutions to fix that bug, please?

Thank you so much!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-17 8:50 PM

Dear @Manoj Chandran

Did you solve this problem ?

I'm facing the same problem with below information

- STM32H7 MCU platform

- Embedded wizard for GUI development, LTDC support of course

- TFT LCD with DCLK (26.4 MHz min, 33.3 MHz Typ., 46.8 MHz max)

- System clock configuration: 400MHz

- SDRAM clock configuration: 100MHz

Tearing effect in TFT LCD also occur.

I'm very appreciate if you help me to solve it

Thanks and best regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-18 1:35 AM

So what rate are you clocking the display?

How wide is you SDRAM interface?

Understand H7 quite a different beast that F429I.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-18 2:02 AM

So what rate are you clocking the display?

==> 33MHz.

How wide is you SDRAM interface?

==> 32 bit

For more information, I already config Pixel clock and timings configuration as TFT LCD specification but it does not work.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-18 2:13 AM

Exact same display, I'm assuming.

Under what circumstances is display tearing? All the time, when image static, when you are accessing SDRAM concurrently? What are caching and MPU settings for memory regions?

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-18 2:18 AM

Display tearing occur when I display a background (800x400) image with rich gradient.

- MCU power consuption measurment STM32N6570-DK in STM32 MCUs Boards and hardware tools

- Dual SDRAM interface in STM32 MCUs Boards and hardware tools

- STM32F469 LTDC Display Shows RGBW Color Cycling Instead of TouchGFX UI - Custom Board in STM32 MCUs TouchGFX and GUI

- tft lcd (LI48800T043TB3099Z02) interface with sdram (Winbond W9825G6KH) on stm32f479zit6 in Others: STM32 MCUs related

- OV7670 + STM32F429 (DCMI + DMA) + ILI9341 SPI — LCD works, no camera image yet in Others: STM32 MCUs related