- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- STM32 and NAND flash ?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32 and NAND flash ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-03-26 3:36 AM

Guys,

Does R/B pin on Nand flash needed on the software ? I can't find R/B pin on GPIO definition, Anyone knows ? thanks #nand- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-03-26 3:48 AM

which device ?

STM32F4 support busy line in FSMC peripheral read RM0090 par. 36.6 Nand flash/PC card controller thebusy signal is called NWAIT for STM32F4 devices PD6 alternate function pin- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-03-26 6:45 AM

Connect the Ready/Busy pin to an EXTI interrupt pin. Use it to time long operations like block erase, where it generates an interrupt when the operation completes (busy to ready edge). That way you can do something else while NAND is busy and not have to poll it.

Jack Peacock- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-03-26 7:21 PM

void

FSMC_NAND_Init(

void

)

{

GPIO_InitTypeDef GPIO_InitStructure;

FSMC_NANDInitTypeDef FSMC_NANDInitStructure;

FSMC_NAND_PCCARDTimingInitTypeDef p;

/* Enable FSMC, GPIOD, GPIOE and AFIO clocks */

RCC_AHBPeriphClockCmd(RCC_AHBPeriph_FSMC, ENABLE);

RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOD | RCC_APB2Periph_GPIOE |

RCC_APB2Periph_GPIOG | RCC_APB2Periph_AFIO , ENABLE);

/*-- GPIO Configuration ------------------------------------------------------*/

/* CLE, ALE, D0->D3, NOE, NWE and NCE2 NAND pin configuration */

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_11 | GPIO_Pin_12 | GPIO_Pin_14 | GPIO_Pin_15 |

GPIO_Pin_0 | GPIO_Pin_1 | GPIO_Pin_4 | GPIO_Pin_5 |

GPIO_Pin_7;

GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF_PP;

GPIO_Init(GPIOD, &GPIO_InitStructure);

/* D4->D7 NAND pin configuration */

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_7 | GPIO_Pin_8 | GPIO_Pin_9 | GPIO_Pin_10;

GPIO_Init(GPIOE, &GPIO_InitStructure);

/* NWAIT NAND pin configuration */

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_6;

GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_IPU;

GPIO_Init(GPIOD, &GPIO_InitStructure);

/* INT2 NAND pin configuration */

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_6;

GPIO_Init(GPIOG, &GPIO_InitStructure);

/*-- FSMC Configuration ------------------------------------------------------*/

p.FSMC_SetupTime = 0xf1;

p.FSMC_WaitSetupTime = 0xf2;

p.FSMC_HoldSetupTime = 0xf3;

p.FSMC_HiZSetupTime = 0xf1;

FSMC_NANDInitStructure.FSMC_Bank = FSMC_Bank2_NAND;

FSMC_NANDInitStructure.FSMC_Waitfeature = FSMC_Waitfeature_Enable;

FSMC_NANDInitStructure.FSMC_MemoryDataWidth = FSMC_MemoryDataWidth_8b;

FSMC_NANDInitStructure.FSMC_ECC = FSMC_ECC_Enable;

FSMC_NANDInitStructure.FSMC_ECCPageSize = FSMC_ECCPageSize_512Bytes;

FSMC_NANDInitStructure.FSMC_TCLRSetupTime = 0xa1;

FSMC_NANDInitStructure.FSMC_TARSetupTime = 0x15;

FSMC_NANDInitStructure.FSMC_CommonSpaceTimingStruct = &p;

FSMC_NANDInitStructure.FSMC_AttributeSpaceTimingStruct = &p;

FSMC_NANDInit(&FSMC_NANDInitStructure);

/* FSMC NAND Bank Cmd Test */

FSMC_NANDCmd(FSMC_Bank2_NAND, ENABLE);

}- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-03-26 7:39 PM

READY/BUSY/WAIT - Many NAND drivers will spin on the GPIO read status.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-03-26 7:45 PM

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-03-27 4:08 AM

which one is R/B ?

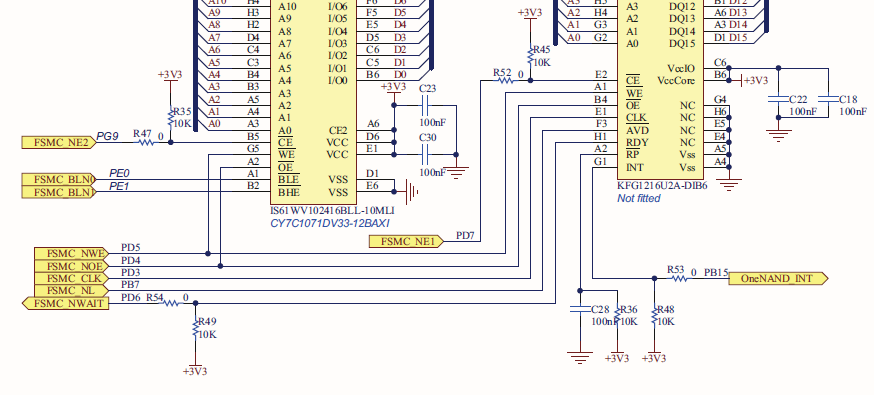

I don't have PG6, could it be PD6 ? what's PG6 for then ?? I attached the schematic and Nand Flash chip datasheet, what do you reckon ? thanks

/* NWAIT NAND pin configuration */

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_6;

GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_IPU;

GPIO_Init(GPIOD, &GPIO_InitStructure);

/* INT2 NAND pin configuration */

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_6;

GPIO_Init(GPIOG, &GPIO_InitStructure);- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-03-27 5:49 AM

FFS it's the WAIT pin, in this case a GPIO Input on PD6, providing a BUSY (B) or READY (R) signal. It's presumably a GPIO because the signal is not sufficiently compatible with the FSMC, or that's it's not appropriate to stall the CPU waiting for a slow memory device.

The interrupt mode would only be appropriate if you have some stateful implementationUp vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-03-27 5:59 AM

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-03-28 5:50 AM

am I defining the pin on code into the board correctly ? Please have a look on the code :

/* CLE, ALE, D0->D3, NOE, NWE and NCE2 NAND pin configuration */

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_11 | GPIO_Pin_12 | GPIO_Pin_14 | GPIO_Pin_15 |

GPIO_Pin_0 | GPIO_Pin_1 | GPIO_Pin_4 | GPIO_Pin_5 |

GPIO_Pin_7;

GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF_PP;

GPIO_Init(GPIOD, &GPIO_InitStructure);

CLE = PD11

ALE = PD12

D0 = PD14

D1 = PD15

D2 = PD0

D3 = PD1

NOE = PD4 = RE ? <==On NAND Flash board

NWE = PD5 = WE ? <==On NAND Flash board

NCE2= PD7 = CE ? <==On NAND Flash board

/* D4->D7 NAND pin configuration */

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_7 | GPIO_Pin_8 | GPIO_Pin_9 | GPIO_Pin_10;

GPIO_Init(GPIOE, &GPIO_InitStructure);

/* NWAIT NAND pin configuration */

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_6;

GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_IPU;

GPIO_Init(GPIOD, &GPIO_InitStructure);

D4 = PD7

D5 = PD8

D6 = PD9

D7 = PD10

NWAIT = PD6 = R_B ? <==On NAND Flash board- Questions regarding STM32U5 Flash endurance in STM32 MCUs Products

- NUCLEO-N657X0-Q does not power up after supplying 7V through VIN with CN9 set to VIN in STM32 MCUs Boards and hardware tools

- Programming OSPI flash of STM32U5G-DK1 in Indirect memory mode in STM32 MCUs Products

- Loading New Firmware onto Write-Protected STM32 B-U585I in STM32 MCUs Security

- GPIO_IOToggle_TrustZone example using STM32 TrustZone in STM32 MCUs Security