- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- [OTG + documentation + Cube] OTG_HS_GUSBCFG.TRDT v...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

[OTG + documentation + Cube] OTG_HS_GUSBCFG.TRDT values

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-08-29 2:06 PM

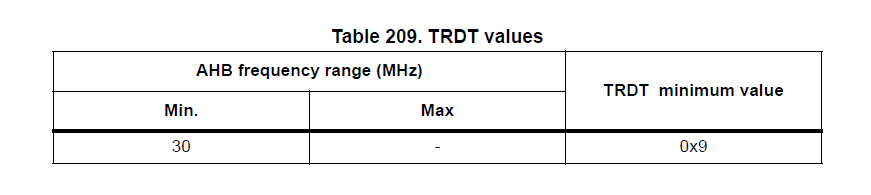

In RM0090 rev.15, OTG_HS_GUSBCFG.TRDT description (p1410) links to Table9, which gives a single value, 0x09.

However, in CubeF4, the TRDT value is determined based on the actual link speed (regardless of whether internal FS_PHY is used or an external ULIP PHY), as determined by USB_GetDevSpeed(), i.e. by reading OTG_HS_DSTS.ENUMSPD: if it is USB_OTG_SPEED_HIGH, the value of USBD_HS_TRDT_VALUE (== 0x09) is used; otherwise the value is determined based on AHB speed in the same way as for OTG_FS (which is contrary to documentation which calls for a single value).

IMO, both are wrong.

My guess is, that the documentation should say '0x09 if ULPI PHY is used, the variable value based on AHB asi in the OTG_FS chapter if the internal FS_PHY is used'.

And then Cube should follow this rule, i.e. set TRDT based on the PHY used rather than based on the detected speed.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-08-30 6:45 AM

Both OTG_HS and OTG_FS in RM0090 contain a 'Choosing the value of TRDT ...' subchapter, adding to the confusion.

If the values given in the tables are 100% OK and should the description be precise enough, those subchapters ought to be removed.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-09-14 7:22 AM

Hi Jan,

- For the

HS mode

, the TRDT minimum value should be 0x9.

if ( USB_GetDevSpeed(hpcd->Instance) == USB_OTG_SPEED_HIGH)

{

hpcd->Init.speed = USB_OTG_SPEED_HIGH;

hpcd->Init.ep0_mps = USB_OTG_HS_MAX_PACKET_SIZE ;

hpcd->Instance->GUSBCFG |= (uint32_t)((USBD_HS_TRDT_VALUE << 10U) & USB_OTG_GUSBCFG_TRDT);

}�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?- For the

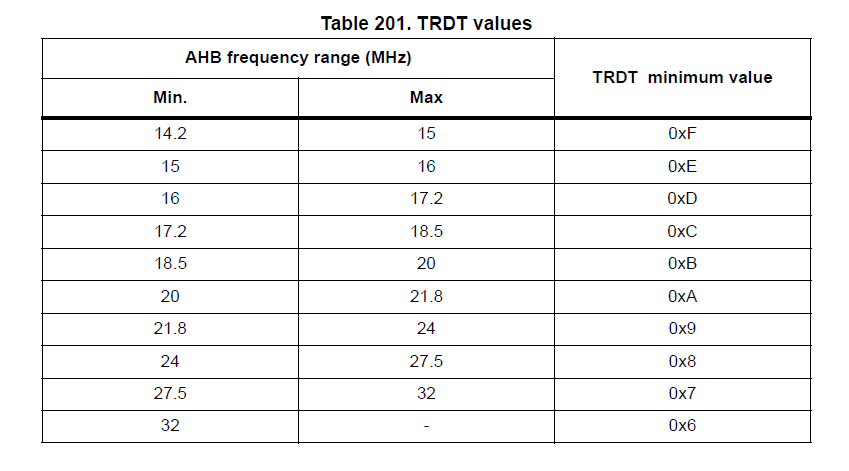

FS mode

, the TRDT minimum value depends on the AHB frequency range, it should be configured as described in the table below:

else

{

hpcd->Init.speed = USB_OTG_SPEED_FULL;

hpcd->Init.ep0_mps = USB_OTG_FS_MAX_PACKET_SIZE ;

/* The USBTRD is configured according to the tables below, depending on AHB frequency

used by application. In the low AHB frequency range it is used to stretch enough the USB response

time to IN tokens, the USB turnaround time, so to compensate for the longer AHB read access

latency to the Data FIFO */

/* Get hclk frequency value */

hclk = HAL_RCC_GetHCLKFreq();

if((hclk >= 14200000U)&&(hclk < 15000000U))

{

/* hclk Clock Range between 2-15 MHz */

hpcd->Instance->GUSBCFG |= (uint32_t)((0xFU << 10U) & USB_OTG_GUSBCFG_TRDT);

}

else if((hclk >= 15000000U)&&(hclk < 16000000U))

{

/* hclk Clock Range between 15-16 MHz */

hpcd->Instance->GUSBCFG |= (uint32_t)((0xEU << 10U) & USB_OTG_GUSBCFG_TRDT);

}

else if((hclk >= 16000000U)&&(hclk < 17200000U))

{

/* hclk Clock Range between 16-2 MHz */

hpcd->Instance->GUSBCFG |= (uint32_t)((0xDU << 10U) & USB_OTG_GUSBCFG_TRDT);

}

else if((hclk >= 17200000U)&&(hclk < 18500000U))

{

/* hclk Clock Range between 2-5 MHz */

hpcd->Instance->GUSBCFG |= (uint32_t)((0xCU << 10U) & USB_OTG_GUSBCFG_TRDT);

}

else if((hclk >= 18500000U)&&(hclk < 20000000U))

{

/* hclk Clock Range between 5-20 MHz */

hpcd->Instance->GUSBCFG |= (uint32_t)((0xBU << 10U) & USB_OTG_GUSBCFG_TRDT);

}

else if((hclk >= 20000000U)&&(hclk < 21800000U))

{

/* hclk Clock Range between 20-8 MHz */

hpcd->Instance->GUSBCFG |= (uint32_t)((0xAU << 10U) & USB_OTG_GUSBCFG_TRDT);

}

else if((hclk >= 21800000U)&&(hclk < 24000000U))

{

/* hclk Clock Range between 8-24 MHz */

hpcd->Instance->GUSBCFG |= (uint32_t)((0x9U << 10U) & USB_OTG_GUSBCFG_TRDT);

}

else if((hclk >= 24000000U)&&(hclk < 27700000U))

{

/* hclk Clock Range between 24-7 MHz */

hpcd->Instance->GUSBCFG |= (uint32_t)((0x8U << 10U) & USB_OTG_GUSBCFG_TRDT);

}

else if((hclk >= 27700000U)&&(hclk < 32000000U))

{

/* hclk Clock Range between 7-32 MHz */

hpcd->Instance->GUSBCFG |= (uint32_t)((0x7U << 10U) & USB_OTG_GUSBCFG_TRDT);

}

else /* if(hclk >= 32000000) */

{

/* hclk Clock Range between 32-180 MHz */

hpcd->Instance->GUSBCFG |= (uint32_t)((0x6U << 10U) & USB_OTG_GUSBCFG_TRDT);

}

}�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?�?I don’t see any mismatch between the information on the reference manual and the driver.

Please let me know if I misunderstood your request.

Many thanks and best regards,

Khouloud.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-09-16 12:11 AM

Hi Khouloud,

In 'F4xx, we have 4 possible combinations for USB device:

1. the OTG_FS module with its internal FS_PHY operating at FS

2. the OTG_HS module with its internal FS_PHY operating at FS

3. the OTG_HS module with external ULPI PHY operating at FS

4. the OTG_HS module with external ULIP PHY operating at HS

As TRDT expresses a synchronisation parameter between core/AHB clock and PHY clock, in my opinion, in cases 1 and 2 table 201. pertains, while in cases 3 and 4 TRDT should be set according to table 209.

If the above is true, then the following two problems arise:

1. The OTG_HS chapter (which is relevant for cases 2, 3 and 4) in RM0090 refers to table 209 only, which is IMO wrong for case 2.

2. The code in Cube uses table 209 only for case 4 (uses the detected link speed rather than the type of PHY to distinguish between the cases) and that's IMO wrong for case 3.

JW

- CubeMx Generates FDCAN clock divider multiple times for STM32G474RETx in STM32CubeMX (MCUs)

- Strangely accurate ADC noise in STM32 MCUs Products

- STM32CubeMX2 v1.0.1 released in STM32CubeMX2 (MCUs)

- Flash TrustZone‑enabled firmware with SBSFU using USB DFU (CubeProgrammer)? in STM32 MCUs Security

- USB PD VDM / eMarker Example on STM32G071C8 ? in STM32 MCUs Embedded software