- STMicroelectronics Community

- Automotive and Transportation

- Automotive MCUs

- ECC for Flash and RAM configuration Issues

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

ECC for Flash and RAM configuration Issues

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-04-17 5:12 AM

Hello All,

I am using SPC560B54L5 board along with SPC studio V5.2.1.

I want to enable ECC for RAM and Flash memory area for checking the memory corruption. I enabled the corresponding bits for 1-bit and 2-bit ECC in ECR register but I am unable to enable the corresponding interrupt callback function. I referred to the SPC560Bxx_RLA Test application, and '@How to Find the memory(FLASH) corruption issues in SPC MCUs?'.(from community). But I am unable to call the corresponding interrupt callbacks.

Kindly guide me in enabling the ECC interrupts for Flash and RAM. Please share the example test application for enabling ECC for flash and RAM memory.

Thanks in Advance,

Regards,

R.Santhamurthy

#spc5 #spc5studioSolved! Go to Solution.

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-04-25 8:22 AM

Hello ,

we have not some examples applications on ECC.

we have a change request to integrate ECC test example on the application wizard

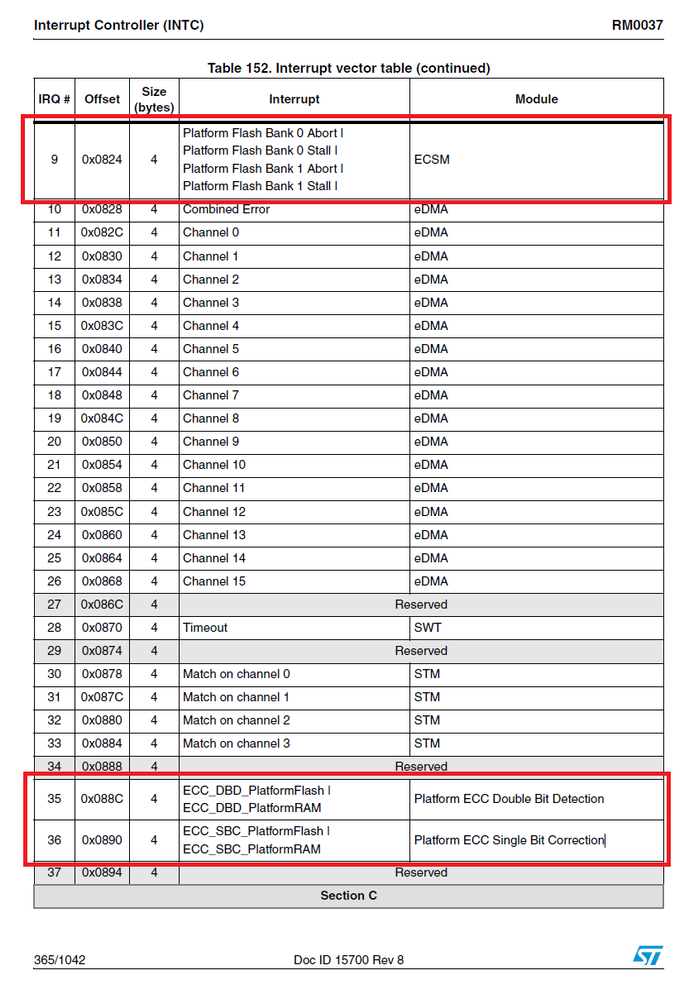

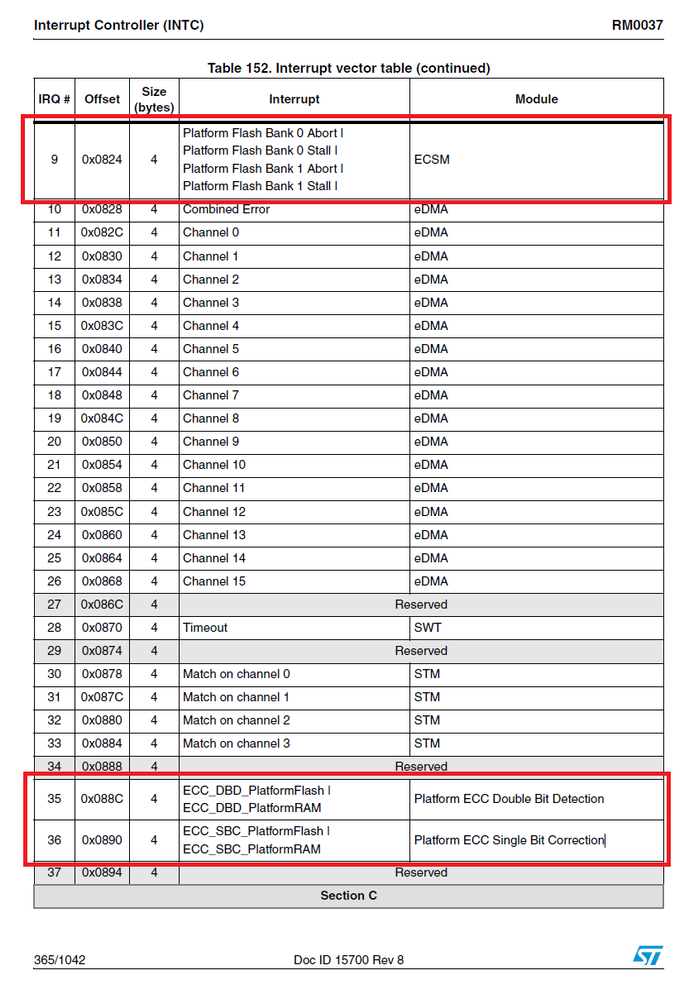

you can go to the ECSM chapter (chapter 36)

i think that you should use vetcor35,vector36

After configuring your ECSM and enable the interrupts,

you can use

ECC Error Generation Register (EEGR)

The ECC Error Generation Register is a 16-bit control register used to force the generationof single- and double-bit data inversions in the memories with ECC, most notably the SRAM.This capability is provided for two purposes:? It provides a software-controlled mechanism for ?injecting? errors into the memoriesduring data writes to verify the integrity of the ECC logic.? It provides a mechanism to allow testing of the software service routines associatedwith memory error logging.Best regards

Erwan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-04-25 8:22 AM

Hello ,

we have not some examples applications on ECC.

we have a change request to integrate ECC test example on the application wizard

you can go to the ECSM chapter (chapter 36)

i think that you should use vetcor35,vector36

After configuring your ECSM and enable the interrupts,

you can use

ECC Error Generation Register (EEGR)

The ECC Error Generation Register is a 16-bit control register used to force the generationof single- and double-bit data inversions in the memories with ECC, most notably the SRAM.This capability is provided for two purposes:? It provides a software-controlled mechanism for ?injecting? errors into the memoriesduring data writes to verify the integrity of the ECC logic.? It provides a mechanism to allow testing of the software service routines associatedwith memory error logging.Best regards

Erwan

- SPC56EL70 RAM program creation and launch in Automotive MCUs

- SPC5 Flash Programmer 2.8.1 – cannot connect to SPC560B64 via UART (works in 2.7.9) in Automotive MCUs

- Connection refused UDE STK on SPC574K-DISP in Automotive MCUs

- Clarity in the steps for configuring a sample project and flashing it to C4MINI Mcu. in AutoDevKit Ecosystem

- UDE Debugging Error on AEK-MCU-C4MLIT1 Board Using AutoDevKit – LED Blinking Fails in AutoDevKit Ecosystem