- STMicroelectronics Community

- Automotive and Transportation

- Automotive MCUs

- Clocking SPC570

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Clocking SPC570

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-08-10 10:17 PM

Hi,

i have a Problem with the Clock Configuration of the SPC570 �C (SPC570S-DISP). I just want to use the External Clock (crystal).

my Configuration:

CGM_SC_DC0/

CGM_SC_DC1/

CGM_SC_DC2 are set to 0x80000000

AC0_SC/AC1_SC/AC2_SC/AC3_SC are set to 0x01000000

My Problem is, i divide the SPI Clock with:

AC0_DC3 = 0x80310000

According to the Reference Manual, the Spi Clock should be 400kHz (40Mhz Crystal / 50 / 2), but it's 200kHz.

Could anyone tell me where my issue could be ?

#spc570sx #dspiSolved! Go to Solution.

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-08-21 4:53 AM

Hello David ,

aips_clk1 is not the good clock.

- apis_clk is the frequency to access the register not the periph

you have to take periph clock

Best regards

Erwan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-08-11 1:17 AM

Hello David ,

AC0_SC/AC1_SC/AC2_SC/AC3_SC is well set to external crystal simulator

the SPI clock should be

(40Mhz Crystal / 50) = 800kHz

Maybe i have missed something.

Did you check your CTAR configuration ?

Anyway, i am going to check with DSPI experts in Autosar team .

Best regards

Erwan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-08-11 2:36 AM

Thanks for your fast answer.

RM0349 Page 473 (Figure 160) say, that the Clock aips_clk1 is divided with 2. 400kHz should be correct.

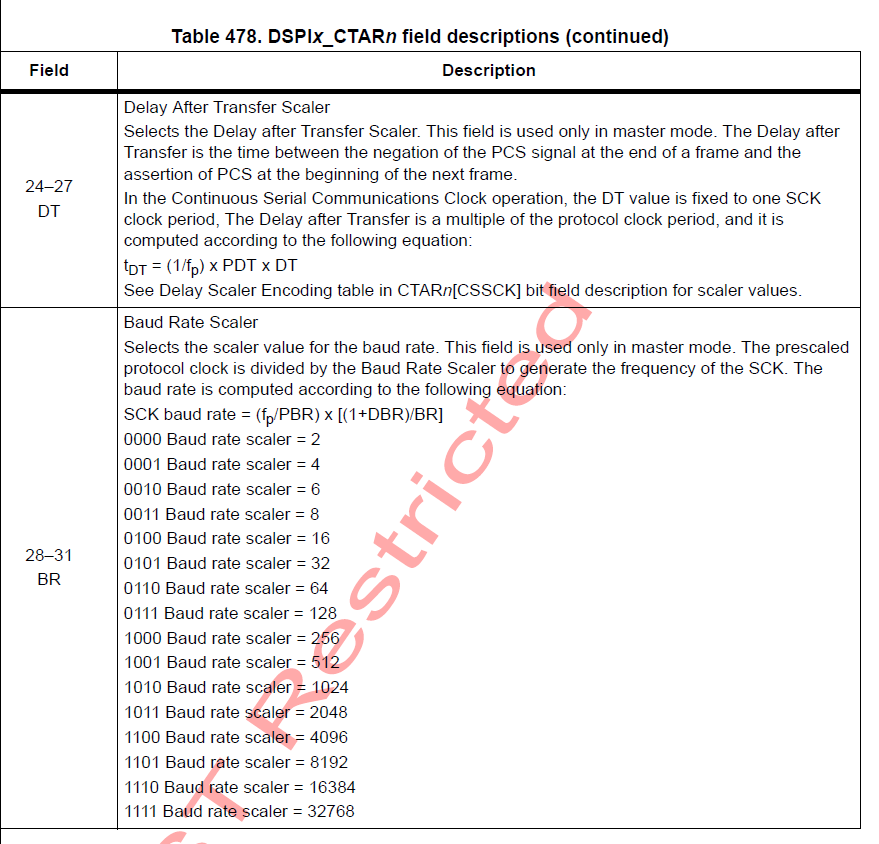

BR, PBR and DBR are set to 0.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-08-21 4:53 AM

Hello David ,

aips_clk1 is not the good clock.

- apis_clk is the frequency to access the register not the periph

you have to take periph clock

Best regards

Erwan

- TCXO frequency & CPU clock tuning for best PPS precision in GNSS positioning

- Still no Clock Tree Wizard for ST SPC58xE series? in Automotive MCUs

- SPC58 RAM Loader over BAF (crash on clock/peripheral init) in Automotive MCUs

- SPI Tx stucks on 1MHz clock in Automotive MCUs

- AEK-COM-ISOSPI1 L9963T MISO and clock out of sync in AutoDevKit Ecosystem