- STMicroelectronics Community

- Knowledge base

- STM32 MCUs

- Do you need a fast slave interface with high throu...

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Email to a Friend

- Printer Friendly Page

- Report Inappropriate Content

Do you need a fast slave interface with high throughput? This is for you.

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Email to a Friend

- Printer Friendly Page

- Report Inappropriate Content

on

2023-02-23

1:58 AM

- edited on

2025-11-26

5:35 AM

by

![]() Laurids_PETERSE

Laurids_PETERSE

Is there an interface that replies to your need?

-

Yes, it is the PSSI.

What does a PSSI stand for?

-

Parallel synchronous slave interface.

What the PSSI interface is?

-

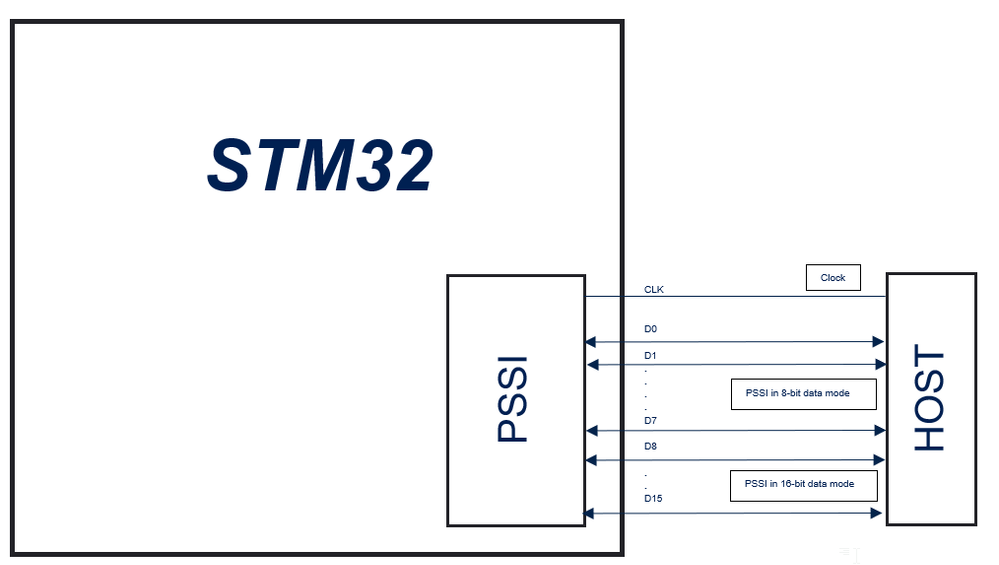

A generic synchronous 8/16-bit parallel data input/output slave interface that can send or receive high-speed data flows.

-

It consists of up to 16 data lines plus a clock line. The clock polarity can be configured so that data can be captured or transmitted on either the clock rising or falling edge.

What is it the most specific about it?

The PSSI interface is:

-

Generic

-

Fast

-

it can only operate in slave mode so a clock must be provided from the master

-

Able to go upward in terms of frequency

PSSI main features?

The PSSI peripheral main features are the following:

-

8-bit or 16-bit parallel data input or output

-

32-byte FIFO

-

DMA capability

-

Data enable alternate function input and ready alternate function output.

What is the maximum PSSI throughput?

-

The max speed is retrieved from the relevant MCU used datasheet

-

The product maximum throughput is defined as following: in 8-bit mode, it goes up to 60MB/s and in 16-bit mode, it goes up to 120MB/s.

-

Let us take the STM32H7B3x as an example, the PSSI interface can go up to:

- 50MB/s in 8-bit read mode and up to 100MB/s in 8-bit write mode- 100MB/s in 16-bit read mode and up to 200MB/s in 16-bit write mode

Where can you find the PSSI interface in the STMicroelectronics products?

-

STM32L4P5xx and STM32LQ5xx (RM0432)

-

STM32U575/585 (RM0456)

-

STM32H7A3/7B3 and STM32H7B0 (RM0455)

-

STM32H723/733, STM32H725/735, and STM32H730 (RM0468)

Example for PSSI project:

-

For an example of communication between two STM32H7 devices connected via the PSSI, please check the STM32CubeH7 under the path: "STM32Cube_FW_H7_Vx.x\Projects\NUCLEO-H723ZG\Examples\PSSI\PSSI_Transmit_Receive_DMA".

This example describes how to perform PSSI data buffer transmission/reception between it as a slave configured on a board and a master simulated by another board. - How to configure and use the PSSI on STM32H7 FAQ article

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Email to a Friend

- Report Inappropriate Content

Hello @ChahinezC ,

Very interesting and informative article. And the short answer to this is a big "YES", I need it, and I always wanted it in an STM32 for a myriad for applications and use cases.

Well, in theory, this is probably the long awaited solution/answer to many problems and challenges I had in previous lines trying to do parallel transmission without a CPLD/FPGA, extra glue logic, or even turning to a completely different silicon, which is something I'm very reluctant to do as an STer.

Unfortunately, skimming the datasheet, the RM for the PSSI section, turns out the synchronous nature of the peripheral is a big set back for me, or at least, the use case in mind. I know there could be a workaround to do it, but I prefer to keep things aligned and use it in its design context.

Thanks

- Mark as Read

- Mark as New

- Bookmark

- Permalink

- Email to a Friend

- Report Inappropriate Content

Moved to a separate thread