Turn on suggestions

Auto-suggest helps you quickly narrow down your search results by suggesting possible matches as you type.

Showing results for

- STMicroelectronics Community

- Knowledge base

- STM32 MPUs

- STM32MP1 how to setup the SDMMC_CK clock frequency...

Options

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Email to a Friend

- Printer Friendly Page

- Report Inappropriate Content

STM32MP1 how to setup the SDMMC_CK clock frequency in Linux

Emmanuel COMBETTE DE RYMON

ST Employee

Options

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Email to a Friend

- Printer Friendly Page

- Report Inappropriate Content

on 2021-07-21 7:15 AM

In the below sdmmc info command, we see timing spec is "mmc DDR52",

whereas clock frequency on SDMMC_CK pin is only at 12.5 MHz

why ?

root@stm32mp151c-oeswa63:~# cat /sys/kernel/debug/mmc0/ios

clock: 25000000 Hz >>>> is SDMMC kernel clock

actual clock: 12500000 Hz >>>> is clock frequency on SDMMC_CK pin chosen by the driver

vdd: 21 (3.3 ~ 3.4 V)

bus mode: 2 (push-pull)

chip select: 0 (don't care)

power mode: 2 (on)

bus width: 3 (8 bits)

timing spec: 8 (mmc DDR52)

signal voltage: 0 (3.30 V)

driver type: 0 (driver type B)

The Linux SDMMC driver decides to takes the highest frequency for the SDMMC_CK pin possible

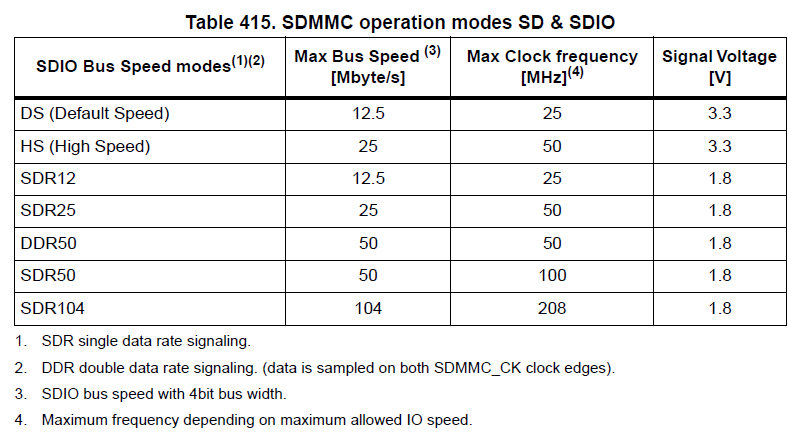

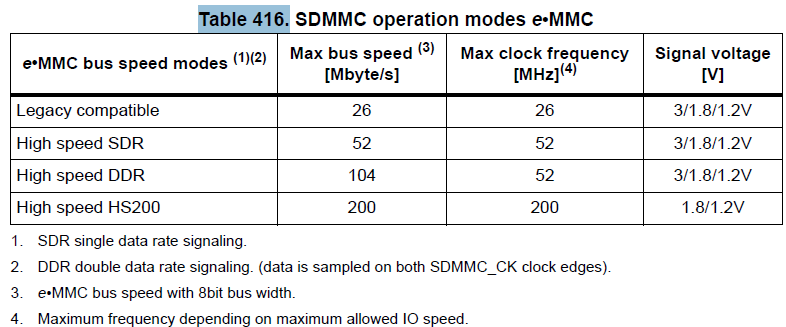

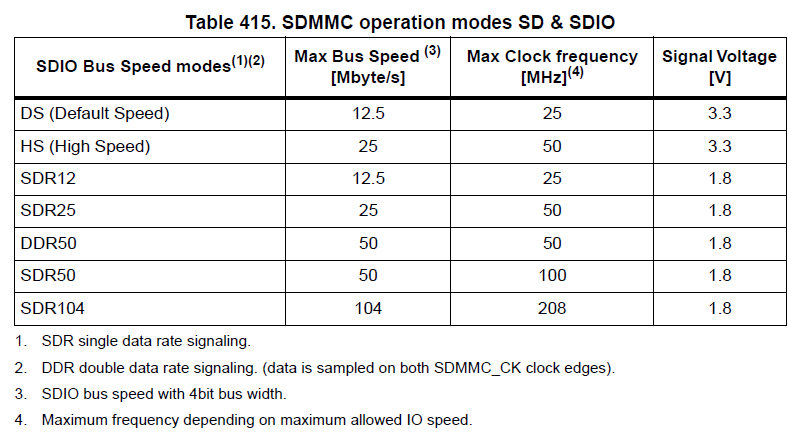

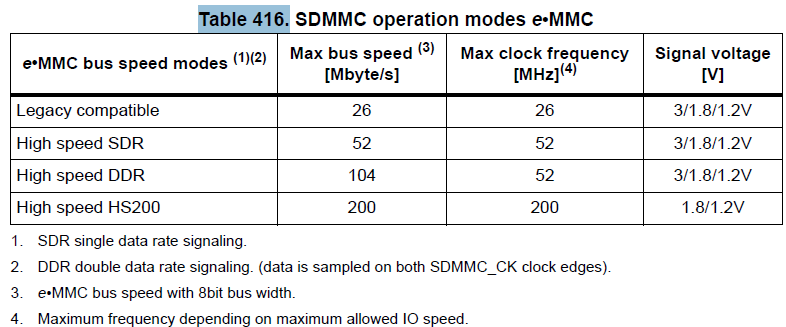

within the max frequency defined by the SDMMC mode (in device tree binding file and table below)

The frequency on SDMMC_CK pin depends SDMMC kernel clock and SDMMC divider.

This divider is at minimum = 2 when the SDMMC is in DDR mode or 1 when in SDR mode

(RM0436rv5 Figure 693)

PLL4P settings in TF-A device tree :

cfg = < 1 42 20 7 7 PQR(1,0,1) >;

frac = < 0x1800 >;

Let's decode the PLL settings from this two device tree lines,

see https://wiki.st.com/stm32mpu/wiki/Clock_device_tree_configuration_-_Bootloader_specific#Defining_peripheral_PLL_frequencies_with_st-2Cpll_property

HSE=24Mhz

PLL4 freq= HSE/2 * (42+1 + 0x1800/8192) = 12 * 43.75 = 525MHz

20=>DIVP=21 ->525/21=25MHz

0x1800 = 6144

8192 value from RefMan FRACV definition

FracN provide decimal value, between 0 min and almost 1 (8191/8192))

So in current situation, PLL4P is 25MHz.

SDMMC Mode in device Tree : mmc-ddr-3_3v (cf binding and tables below) =>max SDMMC_CK = 52 MHz

Better to set PLL4P=89.57MHz -> SDMMC_CK=44.785

Because if we set 104.5 /2 = 52.25 > 52 MHz so driver will not use div=2.

It will use div=4, 104.5/4 = 26.125 MHz

The list of possible "parent clock" for SDMMC kernel clock

See https://github.com/STMicroelectronics/u-boot/blob/v2020.10-stm32mp/include/dt-bindings/clock/stm32mp1-clksrc.h

The parent clock is selected by the device tree "st,pkcs" property

See https://wiki.st.com/stm32mpu/wiki/Clock_device_tree_configuration_-_Bootloader_specific#Defining_peripheral_kernel_clock_tree_distribution_with_st-2Cpkcs_property

SMMDC mode is set according to the flash device and the expected speed .

All mode are not supported by HW (e.g. HS400 on eMMC)

The driver modes are defined in device tree file:

https://github.com/STMicroelectronics/linux/blob/v5.10-stm32mp/Documentation/devicetree/bindings/mmc/mmc-controller.yaml#L181

SDMMC_CK clock max frequency is in tables of RM0436rv5 "SDMMC operation modes"

It is a maximum, so for example SDMMC in "eMMC High speed DDR" mode can have whatever SDMMC_CK frequency value between 0 and 52MHz.

In RefMan0436 tables present HS200, 200MHz is the max clock is defined here is from the JDEC standard .

On STM32MP1 there is limitation on SDMMC_CK for eMMC and SDCard: Max is not 130MHz but 100MHZ.

I/O max speed is the limitation.

whereas clock frequency on SDMMC_CK pin is only at 12.5 MHz

why ?

root@stm32mp151c-oeswa63:~# cat /sys/kernel/debug/mmc0/ios

clock: 25000000 Hz >>>> is SDMMC kernel clock

actual clock: 12500000 Hz >>>> is clock frequency on SDMMC_CK pin chosen by the driver

vdd: 21 (3.3 ~ 3.4 V)

bus mode: 2 (push-pull)

chip select: 0 (don't care)

power mode: 2 (on)

bus width: 3 (8 bits)

timing spec: 8 (mmc DDR52)

signal voltage: 0 (3.30 V)

driver type: 0 (driver type B)

The Linux SDMMC driver decides to takes the highest frequency for the SDMMC_CK pin possible

within the max frequency defined by the SDMMC mode (in device tree binding file and table below)

The frequency on SDMMC_CK pin depends SDMMC kernel clock and SDMMC divider.

This divider is at minimum = 2 when the SDMMC is in DDR mode or 1 when in SDR mode

(RM0436rv5 Figure 693)

-

Let's take the RCC setup of the command above where:

SDMMC is connected to eMMC in DDR mode " eMMC HighSpeed" (see table below) with SDMMC kernel clock source = PLL4P.

PLL4P settings in TF-A device tree :

cfg = < 1 42 20 7 7 PQR(1,0,1) >;

frac = < 0x1800 >;

Let's decode the PLL settings from this two device tree lines,

see https://wiki.st.com/stm32mpu/wiki/Clock_device_tree_configuration_-_Bootloader_specific#Defining_peripheral_PLL_frequencies_with_st-2Cpll_property

HSE=24Mhz

PLL4 freq= HSE/2 * (42+1 + 0x1800/8192) = 12 * 43.75 = 525MHz

20=>DIVP=21 ->525/21=25MHz

0x1800 = 6144

8192 value from RefMan FRACV definition

FracN provide decimal value, between 0 min and almost 1 (8191/8192))

So in current situation, PLL4P is 25MHz.

The driver sets a DDR mode " eMMC HighSpeed" ("mmc-ddr-3_3v" is in sdmmc device tree node)

and selects the highest clock below 52 MHz freq with div=2. It sets SDMMC_CK to PLL4P/2 =12.5 MHz.

and selects the highest clock below 52 MHz freq with div=2. It sets SDMMC_CK to PLL4P/2 =12.5 MHz.

-

Choice of PLL frequency for the SDMMC kernel clock

SDMMC Mode in device Tree : mmc-ddr-3_3v (cf binding and tables below) =>max SDMMC_CK = 52 MHz

Better to set PLL4P=89.57MHz -> SDMMC_CK=44.785

Because if we set 104.5 /2 = 52.25 > 52 MHz so driver will not use div=2.

It will use div=4, 104.5/4 = 26.125 MHz

The list of possible "parent clock" for SDMMC kernel clock

See https://github.com/STMicroelectronics/u-boot/blob/v2020.10-stm32mp/include/dt-bindings/clock/stm32mp1-clksrc.h

The parent clock is selected by the device tree "st,pkcs" property

See https://wiki.st.com/stm32mpu/wiki/Clock_device_tree_configuration_-_Bootloader_specific#Defining_peripheral_kernel_clock_tree_distribution_with_st-2Cpkcs_property

Background information

SMMDC mode is set according to the flash device and the expected speed .

All mode are not supported by HW (e.g. HS400 on eMMC)

The driver modes are defined in device tree file:

https://github.com/STMicroelectronics/linux/blob/v5.10-stm32mp/Documentation/devicetree/bindings/mmc/mmc-controller.yaml#L181

SDMMC_CK clock max frequency is in tables of RM0436rv5 "SDMMC operation modes"

It is a maximum, so for example SDMMC in "eMMC High speed DDR" mode can have whatever SDMMC_CK frequency value between 0 and 52MHz.

In RefMan0436 tables present HS200, 200MHz is the max clock is defined here is from the JDEC standard .

On STM32MP1 there is limitation on SDMMC_CK for eMMC and SDCard: Max is not 130MHz but 100MHZ.

I/O max speed is the limitation.

Labels: