- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Wireless

- BLE_HeartRateFreeRTOS example located in STM32Cub...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

BLE_HeartRateFreeRTOS example located in STM32Cube_FW_WB_V1.3.0 (CubeMX 5.4)

doesn't work

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-11-07 3:50 AM

I reopen this issue under the correct place with correct Topic as STM32WB !

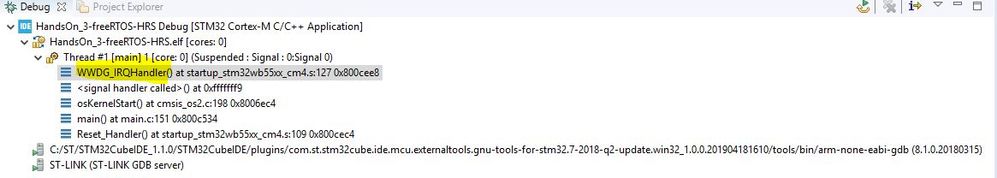

I comiled the BLE_HeartRateFreeRTOS project example located at STM32Cube_FW_WB_V1.3.0 (CubeMX 5.4) as CubeIDE (1.1.0) project,

However the project start running then stucked inside the procedure osKernelStart();

seems, received an WWDG interrupt (see attached snapshot)

although the WWDG compile flag is remarked /*#define HAL_WWDG_MODULE_ENABLED */

Any Idea?

Thanks In Advance,

Micha

- Labels:

-

STM32Cube MCU packages

-

STM32WB series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-02-24 4:20 AM

any solution for this?

I am having the same issue when initiating a cube project.

using:

- cube version 5.6.0

- STM32Cube_FW_WB_V1.5.0

- Atollic true studio version 9.3.0

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-02-24 4:37 AM

Hi Amit,

Seems the existing code, for this project is working fine!

You can generate code from the BLE_HeartRateFreeRTOS.ioc in a separate director (this is the where the original code was taken - this code has some errors) and compare it to existing working code.

Thanks,

Micha

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-05-12 9:46 PM

Hi Amit,

The above problem occur due to a missing handler in the stm32wbxx_it.c file

In order to resolve it, please see an article in freeRTOS website, located at: https://www.freertos.org/Debugging-Hard-Faults-On-Cortex-M-Microcontrollers.html

You need to add some ASM lines (see below)

Default_Handler:

/* Load the address of the interrupt control register into r3. */

ldr r3, NVIC_INT_CTRL_CONST

/* Load the value of the interrupt control register into r2 from the address held in r3. */

ldr r2, [r3, #0]

/* The interrupt number is in the least significant byte - clear all other bits. */

uxtb r2, r2 /* put Break Point (PKBT) here and watch the value in register R2 , this will be the offset in the g_pfnVectors table (see below)

Infinite_Loop:

/* Now sit in an infinite loop - the number of the executing interrupt is held in r2. */

b Infinite_Loop

.size Default_Handler, .-Default_Handler

.align 4

/* The address of the NVIC interrupt control register. */

NVIC_INT_CTRL_CONST: .word 0xe000ed04

g_pfnVectors:

.word _estack /* 0 */

.word Reset_Handler /* 1 */

.word NMI_Handler /* 2 */

.word HardFault_Handler /* 3 */

.word MemManage_Handler /* 4 */

.word BusFault_Handler /* 5 */

.word UsageFault_Handler /* 6 */

.word 0

.word 0

.word 0

.word 0

.word SVC_Handler

.word DebugMon_Handler

.word 0

.word PendSV_Handler

.word SysTick_Handler

.word WWDG_IRQHandler

.word PVD_PVM_IRQHandler

.word TAMP_STAMP_LSECSS_IRQHandler

.word RTC_WKUP_IRQHandler

....