- STMicroelectronics Community

- Automotive and Transportation

- Automotive MCUs

- Using CTU in SPC56EC74

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Using CTU in SPC56EC74

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-09 11:56 PM - edited 2023-11-20 9:38 AM

Hi,

I want to use CTU in SPC56EC74 to trigger ADC conversions upon events generated by EMIOS Unified Channels running in OPWM mode. The ADC and EMIOS are configured and appear working, however CTU does not seem operational.

As far as I understand the CTU has to be enabled by setting appropriate bit in ME_PCTL57. Quoting the xpc56ec.h:

/* Note on PCTL registers: There are only some PCTL implemented in */

/* Bolero 3M. In order to make the PCTL easily addressable, these */

/* are defined as an array (ie ME.PCTL[x].R). This means you have */

/* to be careful when addressing these registers in order not to */

/* access a PCTL that is not implemented. Following are available: */

/* 104, 92, 91, 73, 72, 69, 68, 60, 57, 44, 33, 32, 24, 23, 21-16, 13-4*/

union { /* Peripheral Control 0..143 (+0x00C0-0x0128) */

vuint8_t R;

struct {

vuint8_t :1;

vuint8_t DBG_F:1;

vuint8_t LP_CFG:3;

vuint8_t RUN_CFG:3;

} B;

} PCTL[105];

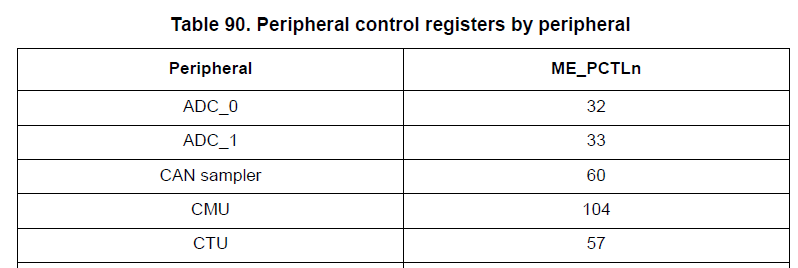

, which apparently means that register 57 is available, and is the right register for the CTU, according to the datasheet:

So I try enabling the CTU:

&sharpdefine SPC5_CTUL_START_PCTL (SPC5_ME_PCTL_RUN(1) | SPC5_ME_PCTL_LP(2))

SPCSetPeripheralClockMode (57, SPC5_CTUL_START_PCTL);

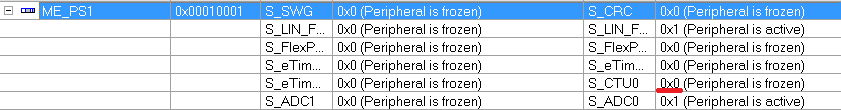

, but cannot verify the actual contents of ME_PCTL57 as there is no such register in SFR View. The SPCSetPeripheralClockMode() executes OK, however looking at the contents of ME_PS1 I can see that the CTU still is frozen:

So my question is, what should be the proper way to enable CTU in SPC56EC74? Another question is why the ME_PCTL57 is not shown in the SFR View?

Regards

Tim

#spc56xx #ctu- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-10 1:59 AM

Hello Tim ,

Your configuration on the PCTL is correct.

Maybe you should configure the trigger source in CTU part.

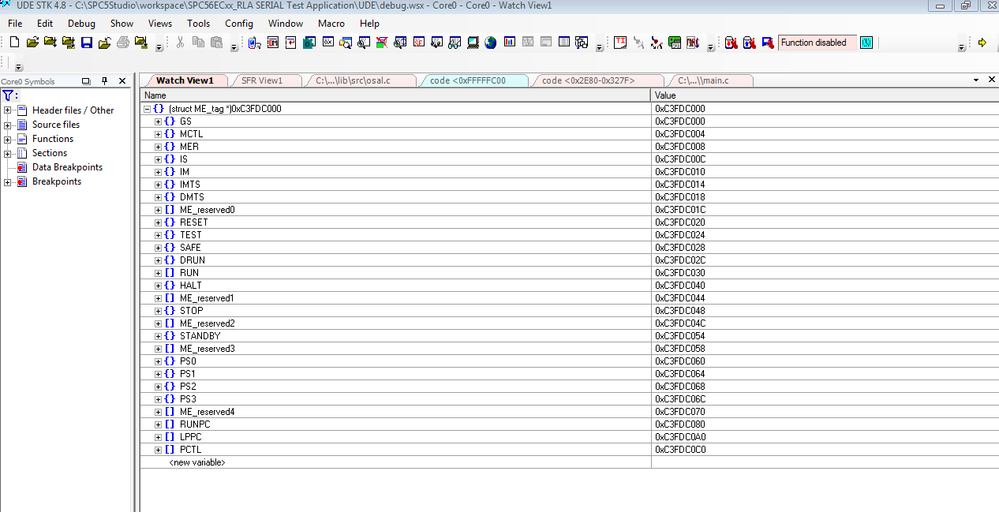

for the PCTL57 not visible on PLS UDE. it is an PLS issue for SFR View.

there is a workaround by using the Watch view in casting the good pointer (cf screenshot)

Best regards

Erwan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-10 3:50 AM