Turn on suggestions

Auto-suggest helps you quickly narrow down your search results by suggesting possible matches as you type.

Showing results for

- STMicroelectronics Community

- Knowledge base

- STM32 MPUs

- FAQ : STM32MP1 how to configure Ethernet PHY Clock...

Options

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Email to a Friend

- Printer Friendly Page

- Report Inappropriate Content

FAQ : STM32MP1 how to configure Ethernet PHY Clocks

Emmanuel COMBETTE DE RYMON

ST Employee

Options

- Subscribe to RSS Feed

- Mark as New

- Mark as Read

- Bookmark

- Subscribe

- Email to a Friend

- Printer Friendly Page

- Report Inappropriate Content

on 2021-07-13 9:45 AM

During ethernet bring-up with Linux you get the following error : "stm32-dwmac 5800a000.ethernet: Failed to reset the dma"

What does it mean ?

How to configure in Linux and in u-boot the STM32MP1 ethernet clocks for the Ethernet PHY ?

How to check the clock setting ?

Other issues for bring-up

https://community.st.com/s/article/FAQ-STM32MP1-bring-up-troubleshooting-guide

1 RMII with 25MHz with Crystal on PHY, REF_CLK from PHY ->AN5031rv3 figure 44

The ETH_CLK pad which provide a clock to the PHY and

clock-names = "stmmaceth","mac-clk-tx","mac-clk-rx","ethstp","syscfg-clk","eth-ck";

2/ TF-A device tree : ensure in the 'st,pkcs' property contains CLK_ETH_PLL4P or CLK_ETH_PLL3Q have a enabled 'ck_kern_eth' clock. This changes the bit RCC_ETHCKSELR.ETHSRC

3/Ensure the used PLL setting define a 25MHZ or 50MHZ

What does it mean ?

How to configure in Linux and in u-boot the STM32MP1 ethernet clocks for the Ethernet PHY ?

How to check the clock setting ?

Other issues for bring-up

https://community.st.com/s/article/FAQ-STM32MP1-bring-up-troubleshooting-guide

1. Symptom

[ 15.650981 ] dwmac4_dma_reset err

[ 15.652849] stm32-dwmac 5800a000.ethernet: Failed to reset the dma

[ 15.659006] stm32-dwmac 5800a000.ethernet eth0: stmmac_hw_setup: DMA engine initialization failed

[ 15.668518] stm32-dwmac 5800a000.ethernet eth0: stmmac_open: Hw setup failed

[ 15.652849] stm32-dwmac 5800a000.ethernet: Failed to reset the dma

[ 15.659006] stm32-dwmac 5800a000.ethernet eth0: stmmac_hw_setup: DMA engine initialization failed

[ 15.668518] stm32-dwmac 5800a000.ethernet eth0: stmmac_open: Hw setup failed

Solution Check Device tree for ethernet clocks (see below) and pin muxing

2. Explanation

Issue is due to the fact PHY does not provide the clock to GMAC, GMAC cannot reset at Ethernet start.

Depending on GMAC interface MII, GMII,RGMII, RMII the clocks are different.

The application note AN5031 §10.1.13 provides ethernet application examples with the different hardware possibilities :

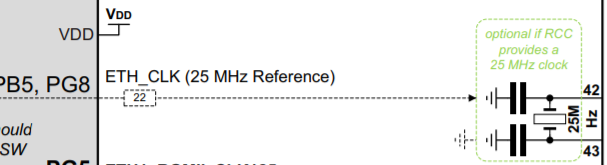

1 RMII with 25MHz with Crystal on PHY, REF_CLK from PHY ->AN5031rv3 figure 44

2 RMII with 25MHz on ETH_CLK pad from internal RCC (no PHY Crystal), REF_CLK from PHY ->AN5031rv3 figure 44

3 RMII with 50MHz on ETH_CLK pad (no PHY Crystal), internal REF_CLK from RCC -> AN5031rv3 figure 45

4 RGMII with Crystal on PHY, ETH_CLK125 from PHY -> AN5031rv3 figure 46

5 RGMII with 25MHz on ETH_CLK (no PHY Crystal), ETH_CLK125 from PHY -> AN5031rv3 figure 46

6 RGMII with 25MHz Crystal on PHY, internal CLK125 from RCC -> AN5031rv3 figure 49

For each configuration find the corresponding Linux and u-boot device tree configurations

https://wiki.st.com/stm32mpu/wiki/Ethernet_device_tree_configuration#DT_configuration

All practical information is explained in this wiki article.

From OpenSTlinux 3.0.1, the properties st,eth_ref_clk_sel or st,eth-ref-clk-sel are deprecated.

They are replaced by st,ext-phyclk. This property is the same for uboot and kernel.

3. Further background information

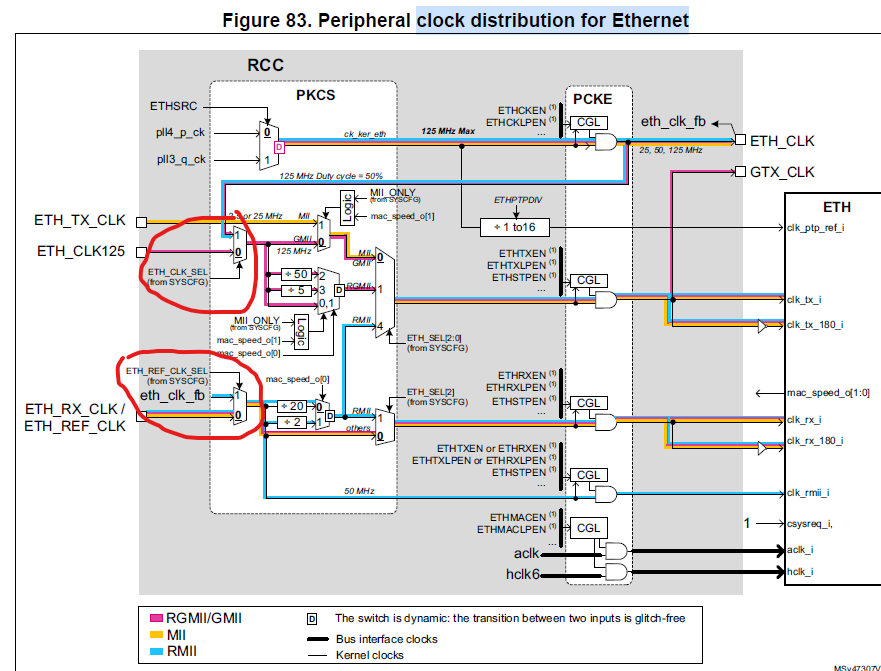

You can see the GMAC clock configuration for the PHY in the RCC reference manual 0436rv5 fig 83

§ RCC Peripheral clock distribution for Ethernet

3 main STM32MP1 pads are to be considered between STM32MP1 GMAC and PHY :

The ETH_CLK pad which provide a clock to the PHY and

The ETH_REF_CLK pad or ETH_CLK125 pad to get reference clock from the PHY.

Depending on the configuration of your design, you have to configure the device tree, then the ethernet driver controls the clock configuration via the below registers.

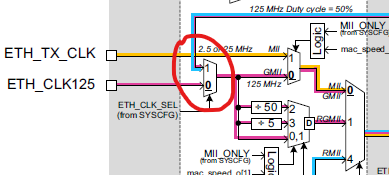

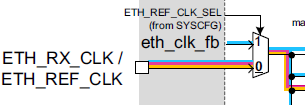

ETH_CLK_SEL, ETH_REF_CLK_SEL and ETH_SEL are controlled via the register SYSCFG_PMCSETR

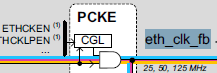

ETHMACEN,ETHRXEN,ETHTXEN,ETHCKEN controlled by RCC_MP_AHB6ENSETR

ETHSRC is controlled by RCC_ETHCKSELR

Linux device tree properties are define under

https://github.com/STMicroelectronics/linux/blob/v4.19-stm32mp/Documentation/devicetree/bindings/net/stm32-dwmac.txt

Further device tee properties explanations

-

"eth-ck" : when there is no crystal to feed the PHY, MP1 on Pad ETH_CLK provides the 25 or 50 MHZ clock to PHY In this case the clode (from ETH_clk fb) is provided by PLL4P or PLL3Q. We are in the AN5031 examples 3 and 6 (above)

1/ add the clock in DT ethernet node :

clock-names = "stmmaceth","mac-clk-tx","mac-clk-rx","ethstp","syscfg-clk","eth-ck";

clocks = <&rcc ETHMAC>,<&rcc ETHTX>,<&rcc ETHRX>,<&rcc ETHSTP>,<&rcc SYSCFG>,<&rcc ETHCK_K>;

<&rcc ETHCK_K> Enable the 'eth_clk_fb' Ethernet fig 83 top right corner

2/ TF-A device tree : ensure in the 'st,pkcs' property contains CLK_ETH_PLL4P or CLK_ETH_PLL3Q have a enabled 'ck_kern_eth' clock. This changes the bit RCC_ETHCKSELR.ETHSRC

3/Ensure the used PLL setting define a 25MHZ or 50MHZ

-

"st,eth-clk-sel "(boolean) : set this property in RGMII PHY when PHY does not provide 125Mhz clock to ETH_CLK125 pad

=>The input ETH_CLK125 pad is not used. The RCC provides 125MHZ clock to GMAC

-

"st,eth-ref-clk_sel" (kernel)/st,eth_ref_clk_sel (Uboot) : set this property in RMII mode when ETH_REF_CLK is not provided by PHY case

=> ETH_RX/REF_CLK pad is not used. Refclock for RMII is from RCC ( eth_clk_fb )

Do not set this property in RMII when the mp1 refclock comes from external PHY via ETH_REF_CLK pad

4. How to check the clock configuration

Dump the state of SYSCFG_PMCSETR

1/enable SYSCFG clk

devmem2 0x50000A10 w 0x10800

2/read SYSCFG_PMCSETR

devmem2 0x50020004

Dump the state of RCC_MP_AHB6ENSETR

devmem2 0x0x5000021C

in uboot md.l 0x5000021C 1

Dump the state of RCC_ETHCKSELR

devmem2 0x0x500008FC

Labels: