- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- TIM14 Period Measurement

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

TIM14 Period Measurement

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-12-22 8:36 AM

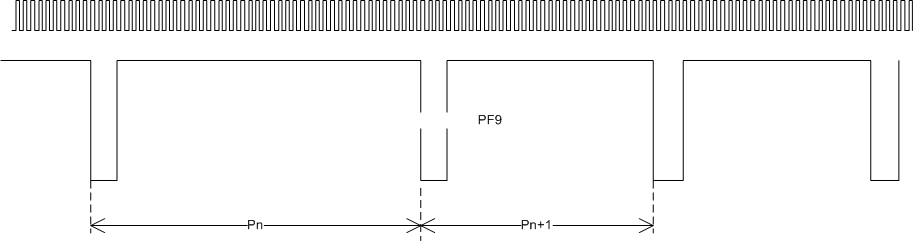

I have an existing STM32F407 family target that has a pulsed signal at PF9. I need to measure the period of this signal. This signal has a fixed low time followed by a variable high time. PF9 can serve as an input to TIM14. Ideally I would like TIM14 to count up based on an internal clock, capturing and clearing the count on an edge of PF9 (rising or falling but not both). The firmware would read the captured value for each cycle. TIM14 would count based on an internal clock. Any suggestions? Is this possible with TIMN14. I known TIM9/12 can measure PWM high and low times. My need is not to capture both as with PWM input, but a single period.

Presently I have an ISR attached to a falling edge of PF9. If necessary, I would read the contents of any freer unning timer each time the interrupt occurs and calculate the timer difference.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-12-22 8:44 AM

Doesn't PWM Input allow you to measure both period and duty using two channels (paired from a single input), and a single interrupt?

Not that it is materially different from input capture and computing a delta, the PWM Input typically resets the counter. If interrupts are unappealing, DMA could be used to take sequential period measurements.Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-12-22 10:07 AM

TIMS 9/12 will do the PWM input. They have two timer captures and that may be why. TIM14 does input capture and has a single capture register. There may well be a way to do a single repetitive period measurement with TIM14 although there does not seem to be a direct example where the count gets cleared to zero after each capture. If I have too, I can use my existing interrupt handler to read a second free running timer I set up. That may add some jitter because another interrupt may or may not occur at the same time.

- STM32G4: Using PC13 for calibrating RTC – how bad can it be, really? in STM32 MCUs Products

- RTC Temperature Calibration -- 20ppm all temperatures feasible? in STM32 MCUs Products

- STM32WB55 STOP2 + BLE advertising current stuck at ~1.1–1.4 mA (WeAct WB55CGU board) in STM32 MCUs Wireless

- Input timer setup halves period after 1st overflow and then remains in that state in STM32 MCUs Products

- UART RX DMA Implementation Issue in STM32 MCUs Products