- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- STM32G483 ADC Noise when connected to OPAMP PGA Ga...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32G483 ADC Noise when connected to OPAMP PGA Gain -3

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-10-06 1:41 AM - edited 2023-10-06 1:51 AM

Hello,

we use a STM32G483RE for analog sampling of downconverted RF signals. To maximize the signal-to-noise ratio in the digital domain we use one of the OPAMPs in inverting PGA mode with a voltage offset that is fed by a differential to single-ended amplifier with the same output common mode voltage as the PGA offset. The OPAMP is connected to the ADC internally. We did some characterization of the PGA noise density by applying no differential signal, i.e. the OPAMP in/out set to 1V DC common mode independent of the gain setting. A timer was used to trigger the ADC sampling at a fixed rate of 1 MHz.

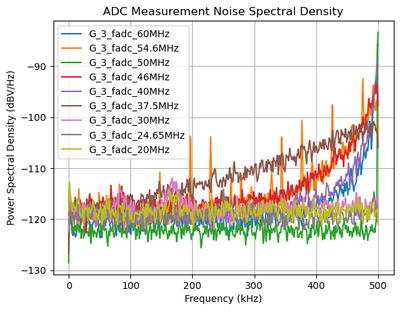

The results of this characterization seem to resemble the datasheet noise values for the ADC with one exception, gain -3. At this gain setting we measured very large noise values. Further investigation has revealed, that it is actually not noise but seems to be related to some clock (see attached plot). The peak is always at half the sample rate, so it is possibly related to the sample rate timer. It is only measurable for ADC clock frequencies above 30 MHz and only for OPAMP gain -3.

Is this a known issue, or can anyone reproduce this behavior?

- Labels:

-

ADC

-

STM32G4 Series

- AN5306,STM32G431: OPAMP output connected to both ADC's internal channels and external pins in STM32 MCUs Products

- STM32L476 OPAMP is not working as expected in STM32 MCUs Products

- STM32U5 OPAMP usage with sine wave with voltage offset in STM32 MCUs Boards and hardware tools

- OPAMP -> ADC continuous reads reduces value. Using STM32G473CCU in STM32 MCUs Products

- H723V + HS ULPI possible damage in STM32 MCUs Products