# STM32 Updates for technical development community

**Microcontrollers Division**

2012 – 2<sup>nd</sup> Issue (July)

### Contents 2

#### Documents Major Updates

- STM8

- STM32F1/L1

- STM32F2/F4

### Technical presentations

- F0 family updates Introduction

- Cortex-M0 CPU

- STM32F05x system parts

- STM32F05x peripherals

# **Documents Major Updates**

### Documents Major Updates Overview

- STM8S/A errata Sheet Rev3 (On Web)

- STM32F205x and STM32F207x datasheet Rev9 (On Web)

- STM32F215x and STM32F217x datasheet Rev7 (On Web)

- STM32F40xx and STM32F41xx datasheet Rev3 (On Web)

- STM32F103xFG and STM32F101xFG datasheet Rev4 (On Web Q3)

- STM32F20x and STM32F21x Errata sheet Rev3 (On Web Q3) STM32F40x STM32F41x Errata sheet - Rev3 (On Web Q3)

# New STM8A/S beCAN limitation - write in beCAN paged registers ignored -

### Introduction 6

- An issue was discovered in STM8S / STM8A beCAN peripheral

- STM8S208 and STM8AF52xx errata have been updated and published, including this new limitation

- Write in beCAN paged registers ignored

- A PIL number MMS-MIC/12/7189 has been issued to inform STM8A customers

- STM32 bxCAN and ST72F561 beCAN are NOT impacted at all by this issue

## Objective of this presentation 7

To be ready to help customer to do a code review (in C source code, and generated assembly code) to confirm the application is not impacted by the issue

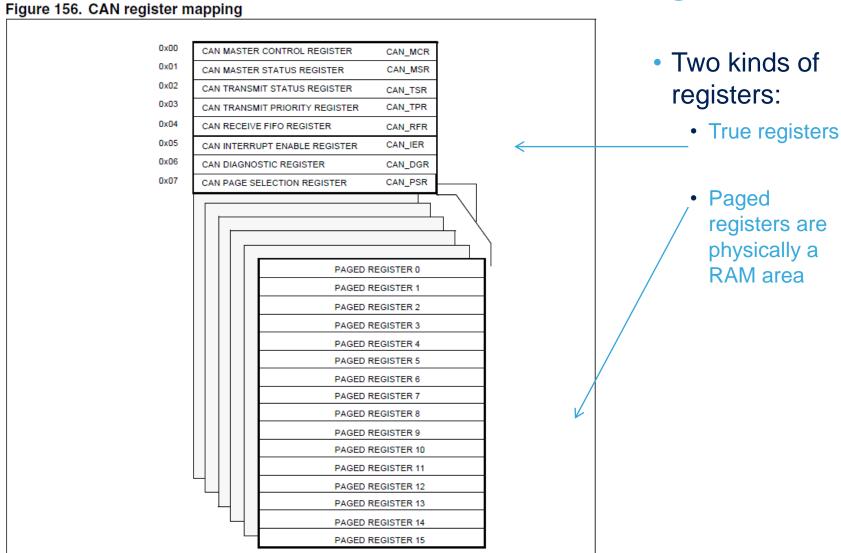

# beCAN registers

8

# beCAN paged registers

#### Figure 157. CAN page mapping

| -    |                                                     |                         |                       |                       |                       |

|------|-----------------------------------------------------|-------------------------|-----------------------|-----------------------|-----------------------|

|      | PAGE 0                                              | PAGE 1                  | PAGE 2                | PAGE 3                | PAGE 4                |

| 0×00 | CAN_MCSR                                            | CAN_MCSR                | CAN_FOR1              | CAN_F2R1              | CAN_F4R1              |

| 0x01 | CAN_MDLCR                                           | CAN_MDLCR               | CAN_F0R2              | CAN_F2R2              | CAN_F4R2              |

| 0x02 | CAN_MIDR1                                           | CAN_MIDR1               | CAN_F0R3              | CAN_F2R3              | CAN_F4R3              |

| 0x03 | CAN_MIDR2                                           | CAN_MIDR2               | CAN_F0R4              | CAN_F2R4              | CAN_F4R4              |

| 0x04 | CAN_MIDR3                                           | CAN_MIDR3               | CAN_F0R5              | CAN_F2R5              | CAN_F4R5              |

| 0x05 | CAN_MIDR4                                           | CAN_MIDR4               | CAN_FOR6              | CAN_F2R6              | CAN_F4R6              |

| 0x06 | CAN_MDAR1                                           | CAN_MDAR1               | CAN_F0R7              | CAN_F2R7              | CAN_F4R7              |

| 0x07 | CAN_MDAR2                                           | CAN_MDAR5               | CAN_F0R8              | CAN_F2R8              | CAN_F4R8              |

| 0x08 | CAN_MDAR3                                           | CAN_MDAR6               | CAN_F1R1              | CAN_F3R1              | CAN_F5R1              |

| 0×09 | CAN_MDAR4                                           | CAN_MDAR4               | CAN_F1R2              | CAN_F3R2              | CAN_F5R2              |

| 0x0A | CAN_MDAR5                                           | CAN_MDAR5               | CAN_F1R3              | CAN_F3R3              | CAN_F5R3              |

| 0x0B | CAN_MDAR6                                           | CAN_MDAR6               | CAN_F1R4              | CAN_F3R4              | CAN_F5R4              |

| 0x0C | CAN_MDAR7                                           | CAN_MDAR7               | CAN_F1R5              | CAN_F3R5              | CAN_F5R5              |

| 0x0D | CAN_MDAR8                                           | CAN_MDAR8               | CAN_F1R6              | CAN_F3R6              | CAN_F5R6              |

| 0x0E | CAN_MTSRL                                           | CAN_MTSRL               | CAN_F1R7              | CAN_F3R7              | CAN_F5R7              |

| 0x0F | CAN_MTSRH                                           | CAN_MTSRH               | CAN_F1R8              | CAN_F3R8              | CAN_F5R8              |

|      | Tx Mailbox 0                                        | Tx Mailbox 1            | Acceptance Filter 0:1 | Acceptance Filter 2:3 | Acceptance Filter 4:5 |

|      | PAGE 5                                              | PAGE 6                  | PAGE 7                |                       |                       |

| 0×00 | CAN_MCSR                                            | CAN_ESR                 | CAN_MFMIR             |                       |                       |

| 0x01 | CAN_MDLCR                                           | CAN_EIER                | CAN_MDLCR             | •                     |                       |

| 0x02 | CAN_MIDR1                                           | CAN_TECR                | CAN_MIDR1             |                       |                       |

| 0x03 | CAN_MIDR2                                           | CAN_RECR                | CAN_MIDR2             |                       |                       |

| 0x04 | CAN_MIDR3                                           | CAN_BTR1                | CAN_MIDR3             |                       |                       |

| 0x05 | CAN_MIDR4                                           | CAN_BTR2                | CAN_MIDR4             |                       |                       |

| 0x06 | CAN_MDAR1                                           | Reserved                | CAN_MDAR1             |                       |                       |

| 0x07 | CAN_MDAR2                                           | Reserved                | CAN_MDAR2             |                       |                       |

| 0x08 | CAN_MDAR3                                           | CAN_FMR1                | CAN_MDAR3             |                       |                       |

| 0x09 | CAN_MDAR4                                           | CAN_FMR2                | CAN_MDAR4             |                       |                       |

| 0x0A | CAN_MDAR5                                           | CAN_FCR1                | CAN_MDAR5             |                       |                       |

| 0x0B | CAN_MDAR6                                           | CAN_FCR2                | CAN_MDAR6             |                       |                       |

| 0x0C | CAN_MDAR7                                           | CAN_FCR3                | CAN_MDAR7             |                       |                       |

| 0x0D | CAN_MDAR8                                           | Reserved                | CAN_MDAR8             |                       |                       |

| 0x0E | CAN_MTSRL                                           | Reserved                | CAN_MTSRL             |                       |                       |

| 0x0F | CAN_MTSRH                                           | Reserved                | CAN_MTSRH             |                       |                       |

|      | Tx Mailbox 2<br>(if TXM2E=1<br>in CAN_DGR register) | Configuration/Diagnosti | ic Receive FIFO       |                       |                       |

### Paged registers consist of

- TX mailbox 0, 1, 2

- RX filters

- Config / diag

- RX FIFO

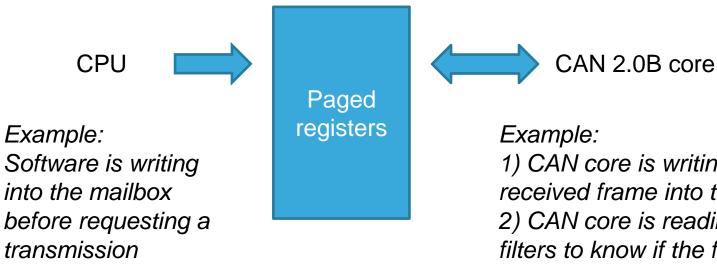

- Paged register (RAM) can be accessed concurrently by the CPU (software) or by the CAN core

- An HW arbitration mechanism is handling concurrent access

## Issue conditions & description 10

- In very specific conditions, a write to the beCAN paged registers may be ignored. This • occurs when the **CPU is writing twice or more** into beCAN paged registers in consecutive master clock cycles, and during the second or further writes, the CAN 2.0B active core is accessing (read or write) one of the paged registers.

- A typical case is when the CPU is writing constants into paged registers (typically a mailbox for transmission) while the CAN 2.0B active core is reading the filters during a frame reception, or writing the FIFO after a frame reception. The beCAN paged registers range is from address 0x5428 to address 0x5437.

- Note: CAN 2.0B active core does not access the paged registers as long as the beCAN is in initialization mode. Therefore the issue can not occur while the software is writing into the paged registers to initialize the beCAN (filters configuration for example).

- The CPU write into two paged registers in two consecutive master clock cycles may only happen in case of consecutive single-cycle load and transfer instructions or single-cycle bit operation instructions, when the destination is an address within the range 0x5428 to 0x5437 inside the beCAN peripheral. The instructions are single-cycle if the source is a constant (embedded in instruction opcode) or in the A accumulator when the same value has to be stored in two or more CAN registers).

## Impact on application & workaround 11

- Impact on application

- When all the specific conditions are met, a corrupted frame may be sent on the CAN bus

- Workaround

- In case you need to write constants consecutively into paged registers, insert a NOP instruction in between each write. You can make use of inline assembly in C code.

## Issue conditions & description 12

1) CAN core is writing a received frame into the FIFO 2) CAN core is reading the filters to know if the frame must be stored or not in the FIFO

# Instructions able to generate consecutive write operations (critical case)<sup>1</sup>

- MOV longmem, #byte ; LD longmem, A ; CLR longmem

- Consecutive MOV instructions with immediate addressing mode

- MOV 0x5429, #0x08

- MOV 0x542a, #0x0d

- MOV 0x542b, #0x40

#### • Consecutive LD instructions with A register as source

- LD 0x542d, A

- LD 0x542e, A

#### • CLR instruction followed by another single-cycle instruction

- CLR 0x542d MOV 0x542e, #0x40

- Mix of single-cycle instructions

- LD 0x5429, A MOV 0x542a, #0x0d

#### Only **single cycles instructions** may generate the critical case

Destination must be a **beCAN paged register** address

Source must be **constant** or **A**

# Other very unlikely instructions able to generate consecutive write operations

- Another very unlikely case is indirect or indexed addressing with beCAN address loaded in X or Y registers, which also generates single-cycle instructions.

- LD (X), A; LD (shortoff,X),A; LD (longoff,X),A; LD (Y), A; LD (shortoff,Y); LD (longoff, Y); CLR (X); CLR (shortoff,X); CLR (longoff,X); CLR(Y); CLR (shortoff,Y); CLR (longoff,Y); CLR (shortoff, SP)

- This can also happen with a single 2-cycle LDW instruction, if two consecutive registers are written with a 16-bit data, with X or Y register as source.

- List of instructions: LDW longmem, X ; LDW longmem, Y

- LDW 0x542a, X ; with X containing 0x0d40.

14

## Example of critical code 15

#### C code with constants usage

#define MSG\_ID 0x0350

CAN\_P1 = 0x08;

CAN\_P2 = (MSG\_ID >> 6) & 0x1F;

CAN\_P3 = (MSG\_ID << 2) & 0xFC;</pre>

#### Generated assembly code

| 35085429 | mov | _CAN_P1,#8  |

|----------|-----|-------------|

| 350d542a | mov | _CAN_P2,#13 |

| 3540542b | mov | _CAN_P3,#64 |

### Workaround 16

### Insert NOP in C code in case of constants usage

```

#define MSG_ID 0x0350

CAN_P1 = 0x08;

asm("NOP");

CAN_P2 = (MSG_ID >> 6) & 0x1F;

_asm("NOP");

```

```

CAN_P3 = (MSG_ID << 2) & 0xFC;

```

### Example of safe code 17

#### C code with variables usage

MyBuffer1 = 0x08; MyBuffer2 = (MSG\_ID >> 6) & 0x1F; MyBuffer3 = (MSG\_ID << 2) & 0xFC; CAN\_P1 = MyBuffer1; CAN\_P2 = MyBuffer2; CAN\_P3 = MyBuffer3;

#### Generated assembly code

| 35080003   | mov | _MyBuffer1,#8      |

|------------|-----|--------------------|

| 350d0004   | mov | _MyBuffer2,#13     |

| 35400005   | mov | _MyBuffer3,#64     |

| 5500035429 | mov | _CAN_P1,_MyBuffer1 |

| 550004542a | mov | _CAN_P2,_MyBuffer2 |

| 550105542b | mov | _CAN_P3,_MyBuffer3 |

### CAN software drivers 18

- CAN drivers from Vector (third party) and STM8S/A standard peripheral software library should not be impacted by the issue, because some intermediate buffers are used to fill the mailboxes

- Nevertheless, it's recommended to crosscheck inside the C code and especially in generated assembly code

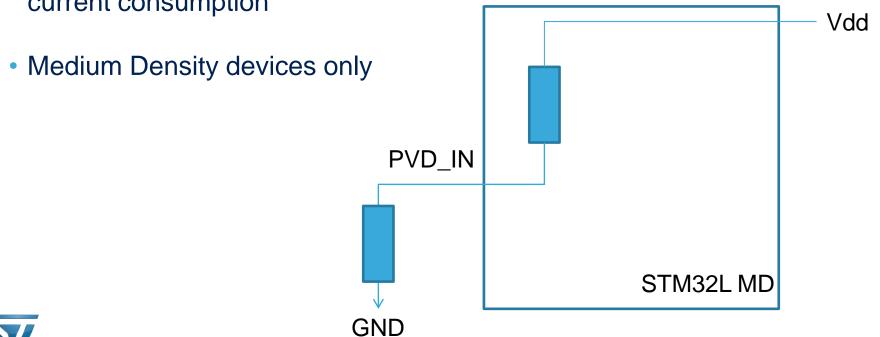

# STM32L MD Errata: PVD\_IN pull-up resistor is always active

- Once PB7 (PVD\_IN) is configured in the analog input mode and PVD level selection PLS[2:0] = 111

External input analog voltage is compared internally to VREFINT

- The internal pull-up resistor is activated even if the Programmable Voltage Detector (PVD) is disabled by PVDE bit causing unwanted current consumption

19

### STM32F2/F4xx datasheets Update 20

### STM32F205x and STM32F207x

Starting from rev "Y" on STM32F205x and STM32F215x devices, the USB 2.0 fullspeed device/host/OTG controller with on-chip PHY peripheral is now available.

#### STM32F405x and STM32F407x

- Starting from rev "Z" on STM32F405x and STM32F415x devices, the USB 2.0 fullspeed device/host/OTG controller with on-chip PHY peripheral is now available.

- Full information on WLCSP90 package added with corresponding part numbers

- A PIL will be sent to our customers in Q3/2012

# STM32F2/4 Errata Sheet Update (1/8) 21

- AHB2APB Bridge could lock the master if APB clock is slowing down during the transfer:

- Description :

- A limitation could appear in case of a master (CPU or DMA) modify the APB clock (slow down the clock) while another master is performing write access to the same APB. In case of an APB prescaler modification (1-> 2, 1 -> 4, 1 -> 8, 1 -> 16) while another master is performing a write access to this target APB, the AHB2APB Bridge could lock the master as a consequence the master performing the write access will freeze and stop his current access.

- Workaround

- Avoid clock slow down on APB while a master is performing write access to this APB peripheral when AHB/APB prescaler is equal to 1.

# STM32F2/4 Errata Sheet Update (2/8) 22

- Non bufferable access to RTC and IWDG could be managed as bufferable access:

- Description

- A limitation could appear in case of the CPU performs non bufferable access to the RTC or IWDG register, the access could be treated as bufferable if there is no APB prescaler configured (AHB/APB prescaler is equal to 1).

- In case of an APB prescaler modification (1-> 2, 1 -> 4, 1 -> 8, 1 -> 16) while another master is performing a write access to this target APB, the AHB2APB Bridge could lock the master. If consecutive accesses are performed only the last one is impacted.

- Workaround

- If the non bufferable attribute is required on this register the user could perform a read after the write to guaranty the completion of the write access.

# STM32F2/4 Errata Sheet Update (3/8) 23

- DMA2 could corrupt data when it managed AHB and APB peripherals in a concurrent way

- Description

- A limitation could appear when the DMA2 managed in a concurrent way AHB (only peripherals embedding FIFOs) and APB transfer. This will generate data corruption (multiple DMA access). When this limitation occurs, the data transferred by the DMA to the AHB peripherals could be corrupted in case of FIFO target,

- For memory the impact is a multiple access (not visible by the user) and the data is not corrupted. For DCMI a multiple unacknowledged request could be generated that imply an unknown behavior of the DMA. AHB Peripherals embedding FIFO are DCMI, CRYPT, and HASH. On sales types without CRYPTO only the DCMI is impacted. External FIFO controlled by the FSMC is also impacted.

- Workaround

- Avoid concurrent AHB (DCMI, CRYPT, HASH, FSMC with external FIFO) and APB transfer management using DMA2.

# STM32F2/4 Errata Sheet Update (4/8) 24

### Flash noise impacting ADC accuracy

- Description

- Embedded Flash noise generated on VDD supplies may impact ADC accuracy; this noise is always active whatever the power mode of the product.

- Workaround

- Two steps could be applied to adapt accuracy level to the application requirements:

- Configure the Flash ART as Prefetch OFF and (Data + Instruction) cache ON

- Use averaging and filtering algorithms on ADC output codes

- For more workaround details of this limitation, please refer to AN4073. (On Web Q3-2012)

# STM32F2/4 Errata Sheet Update (5/8) 25

### Battery charge monitoring limitation

#### Description

- A limitation could appear in case VDD = VDDA is <= 2.4V, Vbat conversion correctness is</li> not guaranteed in full range because: When Vbat is set, the voltage divider bridge is enabled and Vbat/2 is connected to the ADC. In order to monitor the battery charge correctly, the input of the ADC must not be higher than (Vdda-0.6V). It means Vbat/2 < Vdd – 0.6v  $\rightarrow$  VDD > 2,4,

- Workaround

- None, VDD = VDDA should be more than 2.4V

# STM32F2/4 Errata Sheet Update (6/8) 26

### SDIO clock divider BYPASS mode is not working properly

- Description

- For High speed communication mode, when SDIOCLK is equal to 48MHz (PLL48\_output = 48MHz), BYPASS bit equal to '1' and NEGEDGE bit equal to '0' (respectively bit 10 and bit 13 in SDIO\_CLKCR register) hold timing at the chip I/O pin is not inline with SD/MMC specs

- Workaround

- When not using USB nor RNG, PLL48 output (respectively SDIOCLK) frequency can be raise up to 75MHz, allowing to reach 37.5 MHz on SDIO\_CK in High Speed mode. With BYPASS bit equal to '0', CLKDIV bits equal to '0', and NEGEDGE bit equal to '0'.

### SDIO clock dephasing (NEGEDGE) is not working properly

- Description

- When NEGEDGE bit is set to '1' it may leads to invalid data, command response read.

- Workaround

- No workaround available, NEGEDGE bit equal to '1' configuration should not be used.

# STM32F2/4 Errata Sheet Update (7/8) 27

### Delay between RCC write and peripheral enable takes effect

- Description

- A Delay between RCC peripheral clock enable and the effective peripheral enable should be taking into account in order to manage the peripheral read/write. This delay depends on the peripheral mapping:

- If the peripheral is mapped on AHB: delay should be equal to 2 AHB cycle,

- If the peripheral is mapped on APB: delay should be equal to 1 + AHB\_2\_APB prescaler

- Workaround

- Use DSB instruction to stall pipeline until instruction is completed

- Insert two NOPs between RCC enable bit write and peripheral register write

# STM32F2/4 Errata Sheet Update (8/8) 28

### DAC, DMA Underrun flag : management issue

- Description

- A limitation could appear if DMA was not fast enough to input the next digital data to the DAC, As a consequence, the same digital data is converted twice. In these conditions, DMAUDR flag is set which lead normally to disable of DMA data transfers.

- This is not the case: DMA is not disabled by DMAUDR=1 and keeps servicing the DAC,

- Workaround

- None

### DAC, DMA request is not automatically cleared by DMAEN=0

- Description

- A limitation could appear if the application want to stop the current DMA to DAC transfer: DMA request is not automatically cleared by DMAEN=0, or by DACEN=0, If the application stops the DAC operation while the DMA request is high, DMA request will keep pending while DAC is re-initialized and re-started. With the risk that a spuriousunwanted DMA request is serviced as soon as DAC is re-enabled.

- Workaround

- Ensure that the current DMA stream is completed before of stopping DAC operation with DMA.

### Contents 29

- Documents Major Updates

- STM8

- STM32F1/L1

- STM32F2/F4

### Technical presentations

- F0 family updates Introduction

- Cortex-M0 CPU

- STM32F05x system parts

- STM32F05x peripherals

# STM32 F-0 Series For Cost-sensitive applications

日日

**Technical Updates**

June '12

STM32 Releasing your creativity

## Cortex-M processors 31

- Forget traditional 8/16/32-bit classifications

- Seamless architecture across all applications

- Every product optimised for ultra low power and ease of use

| Cortex-M0               | Cortex-M3                | Cortex-M4                 |

|-------------------------|--------------------------|---------------------------|

| "8/16-bit" applications | "16/32-bit" applications | "32-bit/DSC" applications |

|                         |                          |                           |

### **Binary and tool compatible**

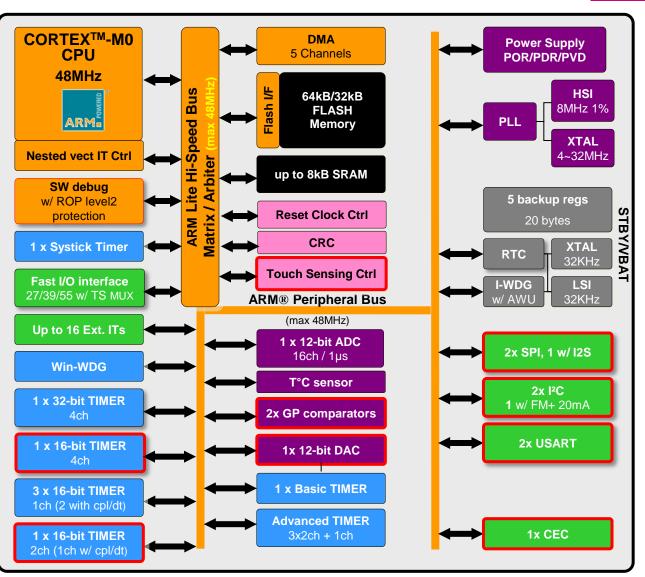

### STM32F05x For Cost-sensitive applications

#### • ARM® Cortex<sup>™</sup> - M0

- Low cost, low power core

- 0.9 DMIPS/MHz at 48 MHz max

- DMA on all products

#### Enhanced features for appliances, consumer and industrial

- Eleven PWM 16-bit timers including motor control timer

- Full analog set fast 1.0 µs 12-bit ADC, 12-bit DAC, comparators

- Consumer Electronic Control (CEC) hardware function

- From 16-Kbyte up to 64-Kbyte Flash

- From 28-pin to 64-pin packages

32

## Class B compliance 33

### Home appliance market regulation requires Class B certification

- Our safety features are ready to support Class B (EN/IEC 60335-1) certification requirements

- Due to HW implementation, some SW checks could be removed or simplified

- CRC FLASH check at startup CRC block available

- HW parity on RAM instead SW run time checks

- CSS clock monitoring

- We provide a library for Class B applications (similar to STM32F1 / STM8)

- Certification to be performed soon on STM32F0

### STM32F0x Series 64KB STM32F051

#### ARM 32-bit Cortex-M0 CPU

- Operating Voltage:

- VDD = 2.0 V to 3.6 V

- VBAT = 1.65 V to 3.6 V

- Safe Reset System (Integrated Power On Reset (POR)/Power Down Reset (PDR) + Programmable voltage detector (PVD))

- Embedded Memories:

- FLASH: up to 64 Kbytes

- SRAM: up to 8 Kbytes

- CRC calculation unit

- 5 Channels DMA

life, augmented

- Power Supply with software configurable internal regulator and low power modes.

- Low Power Modes with Auto Wake-up

- Low power calendar RTC with 20 bytes of backup registers

- Up to 48 MHz frequency managed & monitored by the Clock Control w/ Clock Security System

- Rich set of peripherals & IOs

- 1 x 12-bit DAC with output buffer

- 2 low power comparators (Window mode and wakeup)

- Dual Watchdog Architecture

- 11 Timers w/ advanced control features (including Cortex SysTick, RTC and WDGs)

- 7 communications Interfaces

- Up to 55 fast I/Os all mappable on external interrupts/event

- 1x12-bits 1Msps ADC w/ up to 16 external channels + Temperature sensor/ voltage reference/VBAT measurement

Note: Features outlined in red are not present on STM32F050 product (just one I<sup>2</sup>C,SPI & USART) 2012 Technical Update 34

life.auamente

### STM32F05x Documents Major Updates

- STM32F05x Reference Manual Rev1 (on web)

- STM32F05x Cortex-M0 Programming Manual Rev1 (on web)

- STM32F051 Datasheet Rev1 (on web)

- STM32F050 Datasheet Rev1 (on web)

- STM32F051 Erratasheet Rev1 (On Web Q3)

- STM32F050 Erratasheet Rev1 (On Web Q3)

36

## STM32F0x Core and System Technical Introduction

### M0 – a low cost Cortex-M processor

#### • Address "low end" applications, as a 8/16-bit MCU replacement

- Similar gate count to 16-bit processors

- For high end/processing intensive applications, the global MCU price point is lower than most of 8/16-bit processors due to lower code memory footprint (similar, in a few percent range to the Cortex-M3)

- High performance, only 25-30% lower than the standard Cortex-M3 32-bit architecture

- Very good power and area optimization

- Designed for low cost and low power

- Automatic state saving on interrupt and exceptions

- Low software overhead on exception entry and exit

- Deterministic instruction execution timing

- Instructions always take same time to execute, from a deterministic memory system

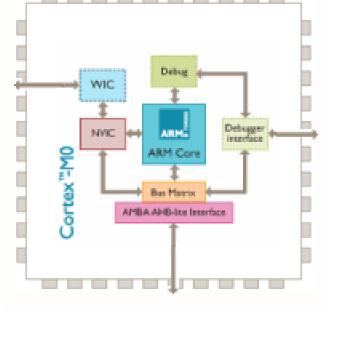

## Cortex-M0 processor microarchitecure

#### ARMv6M Architecture

- Thumb-2 Technology

- Integrated configurable NVIC

- Compatible with Cortex-M3

#### Microarchitecture

- 3-stage pipeline with branch speculation

- 1x AHB-Lite Bus Interfaces

#### Configurable for ultra low power

• Deep Sleep Mode, Wakeup Interrupt Controller (Not available for STM32F05)

#### Flexible configurations for wider applicability

- Configurable Interrupt Controller (1-32 Interrupts and Priorities)

- No Memory Protection Unit

- Optional Debug & Trace

39

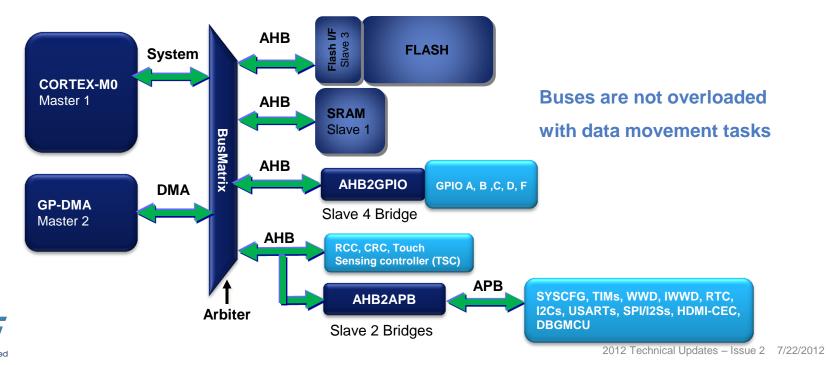

## System Architecture 40

- Multiply possibilities of bus accesses to SRAM, Flash, Peripherals, DMA

- BusMatrix added to allow parallel access

- Efficient DMA and Rapid data flow

- Direct path to SRAM through arbiter, guarantees alternating access

- Von Neumann + BusMatrix allows Flash execution in parallel with DMA transfer

#### **Increase Peripherals Speed for better performance**

- Advanced Peripheral bus (APB) architecture up to 48MHz

- Allows to optimize use of peripherals (18MBits/s SPI, 6Mbps USART, 48MHz GP-Timer, 12MHz toggling I/Os)

### Cortex-M feature set comparison 41

|                               | Cortex-M0                             | Cortex-M3       | Cortex-M4                         |

|-------------------------------|---------------------------------------|-----------------|-----------------------------------|

| Architecture Version          | V6M                                   | v7M             | v7ME                              |

| Instruction set architecture  | Thumb, Thumb-2<br>System Instructions | Thumb + Thumb-2 | Thumb + Thumb-2,<br>DSP, SIMD, FP |

| DMIPS/MHz                     | 0.9                                   | 1.25            | 1.25                              |

| Bus interfaces                | 1                                     | 3               | 3                                 |

| Integrated NVIC               | Yes                                   | Yes             | Yes                               |

| Number interrupts             | 1-32 + NMI                            | 1-240 + NMI     | 1-240 + NMI                       |

| Interrupt priorities          | 4                                     | 8-256           | 8-256                             |

| Breakpoints, Watchpoints      | 4/2/0, 2/1/0                          | 8/4/0, 2/1/0    | 8/4/0, 2/1/0                      |

| Memory Protection Unit (MPU)  | No                                    | Yes (Option)    | Yes (Option)                      |

| Integrated trace option (ETM) | No                                    | Yes (Option)    | Yes (Option)                      |

| Fault Robust Interface        | No                                    | Yes (Option)    | No                                |

| Single Cycle Multiply         | Yes (Option)                          | Yes             | Yes                               |

| Hardware Divide               | No                                    | Yes             | Yes                               |

| WIC Support                   | Yes                                   | Yes             | Yes                               |

| Bit banding support           | No                                    | Yes             | Yes                               |

| Single cycle DSP/SIMD         | No                                    | No              | Yes                               |

| Floating point hardware       | No                                    | No              | Yes (Option)                      |

| Bus protocol                  | AHB Lite                              | AHB Lite, APB   | AHB Lite, APB                     |

| CMSIS Support                 | Yes                                   | Yes 2012 Tec    | chnical Updates – 🌾 🕫 2 7/22/2012 |

## Cortex-M0 differences vs Cortex-M3 42

- Less Breakpoints/Watchpoints (4/2)

- Only Serial-Wire-Debug (SWD) to save JTAG pins but on same 20pins connector

- Only one I/F (AHB lite bus) to connect memories, external bus Matrix, etc....

- Cortex-M0 does not support different privilege levels, Software execution is always privileged, meaning software can access all the features of the processor.

- No Bit-Banding

- No support of un-aligned data

### Cortex-M processors binary compatible 43

| РКН                   | QADD                 | QADD16     | QADD8      | QASX    | QDADD    | QDSUB                | QSAX    | QSUB                        |

|-----------------------|----------------------|------------|------------|---------|----------|----------------------|---------|-----------------------------|

| QSUB16                | QSUB8                | SADD16     | SADD8      | SASX    | SEL      | SHADD16              | SHADD8  | SHASX                       |

| SHSAX                 | SHSUB16              | SHSUB8     | SMLABB     | SMLABT  | SMLATB   | SMLATT               | SMLAD   | SMLALBB                     |

|                       |                      |            |            |         |          |                      | SMLALBT | SMLALTB                     |

| ADC                   | ADD                  | ADR        | AND        | ASR     | В        | CLZ                  | SMLALTT | SMLALD                      |

| BFC                   | BFI                  | BIC        | CDP        | CLREX   | CBNZ CBZ | CMN                  | SMLAWB  | SMLAWT                      |

| СМР                   |                      |            |            | DBG     | EOR      | LDC                  | SMLSD   | SMLSLD                      |

| LDMIA                 | BKPT BLX             | ADC ADD    | ADR        | LDMDB   | LDR      | LDRB                 | SMMLA   | SMMLS                       |

| LDRBT                 | BX CPS               | AND ASR    | ) <b>B</b> | LDRD    | LDREX    | LDREXB               | SMMUL   | SMUAD                       |

| LDREXH                | ОМВ                  | BL         | BIC        | LDRH    | LDRHT    | LDRSB                | SMULBB  | SMULBT                      |

| LDRSBT                | DSB                  | CMN CMP    | EOR        | LDRSHT  | LDRSH    | LDRT                 | SMULTB  | SMULTT                      |

| MCR                   | ISB                  |            | ) LDM      | LSL     | LSR      | MLS                  | SMULWB  | SMULWT                      |

| MCRR                  | MRS                  | LDRH LDRSB | ) (LDRSH)  | MLA     | MOV      | MOVT                 | SMUSD   | SSAT16                      |

| MRC                   | MSR                  |            | ) MOV      | MRRC    | MUL      | MVN                  | SSAX    | SSUB16                      |

| NOP                   | NOP REV              | MUL MVN    | ORR        | ORN     | ORR      | PLD                  | SSUB8   | SXTAB                       |

| PLDW                  | REV16 REVSH          | POP PUSH   | ) ROR      | PLI     | РОР      | PUSH                 | SXTAB16 | SXTAH                       |

| RBIT                  | SEV SXTB             | RSB SBC    | ) STM      | REV     | REV16    | REVSH                | SXTB16  | UADD16                      |

| ROR                   | SXTH UXTB            | STR STRB   | ) STRH     | RRX     | RSB      | SBC                  | UADD8   | UASX                        |

| SBFX                  | UXTH WFE             | SUB SVC    | ) TST      | SDIV    | SEV      | SMLAL                | UHADD16 | UHADD8                      |

| SMULL                 | WFI YIELD            | CORTEX-    | M0/M1      | SSAT    | STC      | STMIA                | UHASX   | UHSAX                       |

| STMDB                 |                      |            |            | STR     | STRB     | STRBT                | UHSUB16 | UHSUB8                      |

| STRD                  | STREX                | STREXB     | STREXH     | STRH    | STRHT    | STRT                 | UMAAL   | UQADD16                     |

| SUB                   | SXTB                 | SXTH       | твв        | ТВН     | TEQ      | TST                  | UQADD8  | UQASX                       |

| UBFX                  |                      | UMLAL      | UMULL      | USAT    | UXTB     | UXTH                 | UQSAX   | UQSUB16                     |

| WFE                   | WFI C                | YIELD      | T          |         | С        | ORTEX-M3             | UQSUB8  | USAD8                       |

|                       |                      |            |            |         |          |                      | USADA8  | USAT16                      |

| USAX                  | USUB16               | USUB8      | UXTAB      | UXTAB16 | UXTAH    | UXTB16               | )       | Cortex-M4                   |

|                       |                      |            |            |         |          |                      |         |                             |

|                       |                      |            |            |         |          |                      |         |                             |

| VABS                  |                      | VCMP       | VCMPE      |         |          |                      |         | VLDR                        |

| VABS                  |                      |            |            |         |          |                      |         |                             |

| VABS<br>VMLA<br>VNMUL | VADD<br>VMLS<br>VPOP |            |            |         |          | VDIV<br>VNEG<br>VSUB |         | VLDR<br>VNMLS<br>Cortex-M4F |

## Cortex-M0 differences vs Cortex-M3

- V6M Architecture : Only 56 Instructions

- 46 instructions (generally generated by a C compiler)

- 10 instructions for System & special usage

- Can run a Traditional ARM7/9 THUMB instructions

- 8/16/32-bits data transfers possible on One Instruction

- No Hardware Divide

- No IT (If-Then-Else) blocks to avoid small Branches

- All instructions are 16-bits Thumb to save code memory,

- Except the 32-bit Thumb instructions BL, DMB,

- DSB, ISB, MRS and MSR.

- Load/Store instructions takes 2cycles each

- Most of MOV, ADD, SUBTRACT, Compare, Logical, SHIFT instructions take 1 cycle

- Branches takes from 1 to 4 cycles (depends if conditional, not or with link)

- "MULS" instruction provides a 32-bit x 32-bit multiply that yields the least significant 32-bits : 1 cycle !

## Cortex-M – firmware compatibility(1/2)

### • Cortex M processors are FW and binary compatible

- Migrating path M0->M3->M4 is straight forward

- Instruction set of Cortex-Mx is strictly included in the instruction set of Cortex-My (for x<y), allowing direct migration, while taking advantage of higher MCU clock speed and von Neumann to Harvard performance increase

- Re-compilation of the code is recommended

- from Cortex-M0 to Cortex-M3, in order to fully take advantage of the higher performance ISA (e.g. HW division)

- From M0/M3 to M4 w/ FPU, in order to generate the FPU code

- For a given STM32 family, a full peripheral set compatibility is guaranteed in order to allow this simple migration path

## Cortex-M – firmware compatibility(2/2)

#### Cortex M processors are FW and binary compatible

- When moving from M0/M3 to M4, some part of the code might be re-coded using intrinsics, taking advantage of the advanced DSP/SIMD instructions

- When moving backwards M3/M4 -> M0, the code needs to be recompiled in order to use only M0 instruction codes

- Code density is equivalent on the different Cortex-M implementations

- Code size differences for usual codes are bellow few percents, provided that the same optimizations options are chosen in the compiler

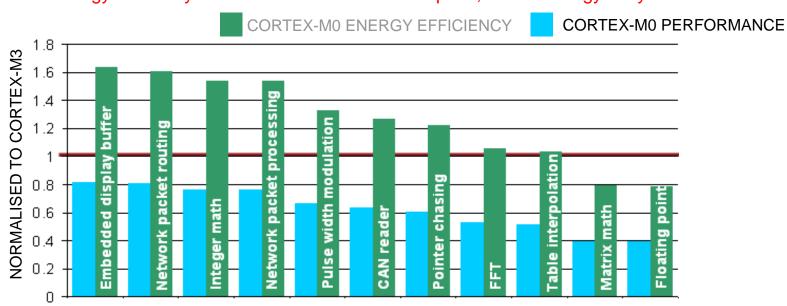

## Cortex-M0 complements Cortex-M3 47

- Cortex-M3 is flagship MCU processor, offering higher performance

- Delivers a performance efficiency advantage

- Cortex-M0 better suited for simpler control and communications

- Delivers an energy efficiency and cost advantage

Note: Energy efficiency ONLY refers to CPU consumption, similar energy at system level

Normalised Cortex-M3 performance and energy efficiency vs. Cortex-M0 for algorithm types. Energy efficiency based on Cortex-M3 and Cortex-M0 processor power estimates – ONLY reffers to CPU consumption, similar energy at system level

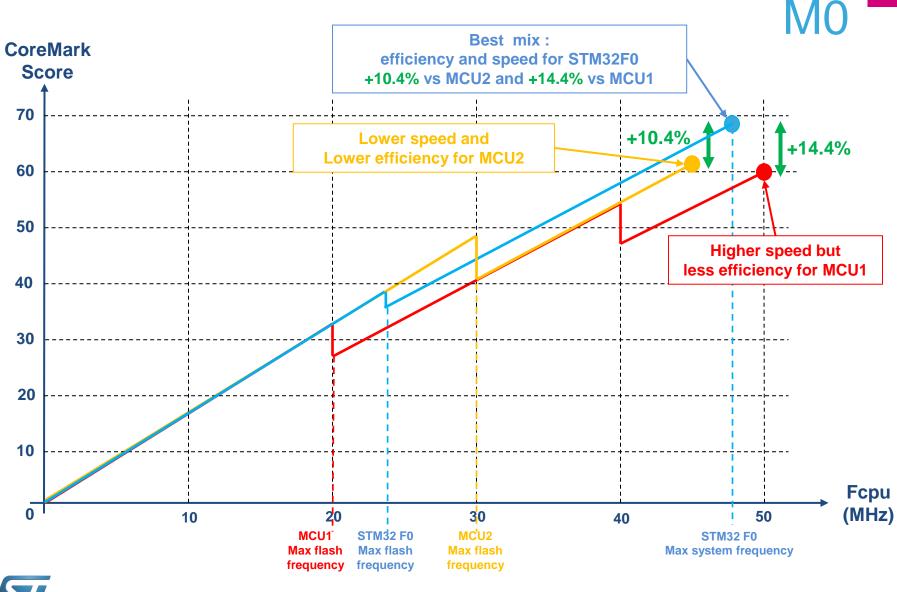

### CoreMark score vs. Competitors on

\* Relative results based on ARM-MDK v4.50 compiler and in same conditions 48

## Simplified Register Set 49

| <ul> <li>Very simple, linear 4GByte address space</li> </ul>                       |           |

|------------------------------------------------------------------------------------|-----------|

| Very compiler friendly                                                             | R0        |

| • very complier menuly                                                             | R1        |

| <ul> <li>All registers are 32-bit wide</li> </ul>                                  | R2        |

|                                                                                    | R3<br>R4  |

| <ul> <li>Registers R0 –R7 (Low registers)</li> </ul>                               | R5        |

| <ul> <li>Registers R8 –R12 (High registers)</li> </ul>                             | R6        |

| <ul> <li>3 registers with special usage</li> </ul>                                 | R7        |

| S Tegisters with special usage                                                     | <b>R8</b> |

| <ul> <li>Stack Pointer (SP) –R13</li> </ul>                                        | R9        |

|                                                                                    | R10       |

| <ul> <li>Link Register (LR) –R14</li> </ul>                                        | R11       |

| <ul> <li>Program Counter (PC) –R15</li> </ul>                                      | R12       |

|                                                                                    | R13(SP)   |

| <ul> <li>Special-purpose register</li> </ul>                                       | R14(LR)   |

|                                                                                    | R15 (PC)  |

| <ul> <li>xPSR : Application and Exception Program status bits and flags</li> </ul> |           |

Vector Table contains Addresses

| life.augmented |

|----------------|

**xPSR**

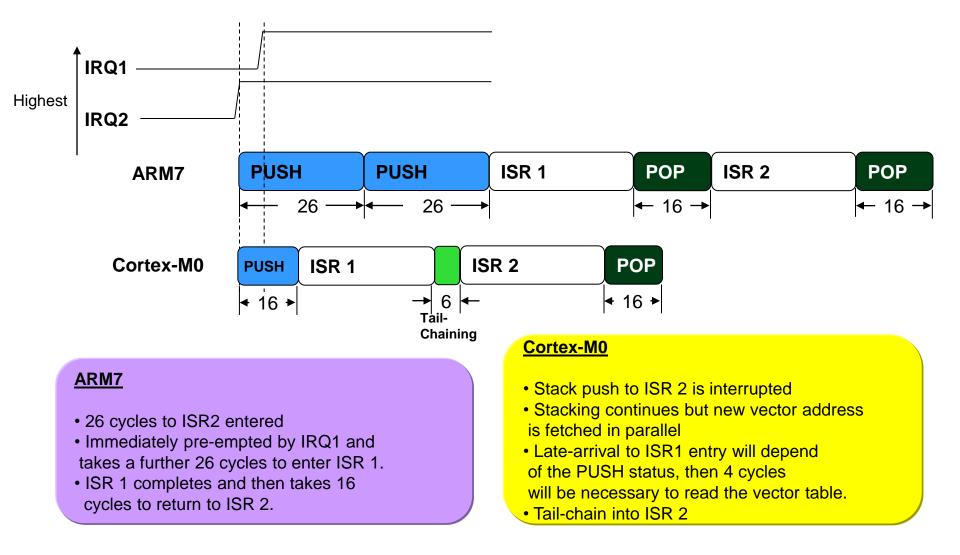

## Exception/Interrupt Handling

#### Very low latency interrupt processing

- Interruptible LDM/STM for low interrupt latency (Load/store multiples)

- Automatic processor state save and restore

- Provides low latency ISR entry and exit

- Allows handler to be written entirely in 'C'

- The Cortex-M0 processor integrates an advanced Nested Vectored Interrupt Controller (NVIC)

- The NVIC supports up to 32 dynamically reprioritizable interrupts each with up to 4 levels of priority

- Allows early processing of interrupts

- Supports advanced features for next generation real-time applications

- Tail-chaining of pending interrupts

- Late-arrival interrupt handling and priority boosting / inversion

#### **Exceptional Control Capabilities Through Integrated Interrupt Handling**

50

## Interrupt Handling Method 51

• Interrupt handling is micro-coded. No instruction overhead

#### • Entry

- Processor state automatically saved to the stack over the bus.

- {PC, xPSR, R0-R3, R12, LR}

- Then, ISR ready to start executing as soon as stack PUSH complete.

- Late arriving interrupt will restart ISR fetching, but state saving does not need to be repeated.

#### • <u>Exit</u>

- Processor state is automatically restored from the stack.

- Then interrupted instruction is executed upon completion of stack POP.

- Stack POP can be interrupted, allowing new ISR to be immediately executed without the overhead of state saving.

### Interrupt Response – Late Arriving

52

## Cortex-M0 Exception Types 53

| No.   | Exception Type | Priority     | Type of<br>Priority | Descriptions                                     |

|-------|----------------|--------------|---------------------|--------------------------------------------------|

| 1     | Reset          | -3 (Highest) | fixed               | Reset                                            |

| 2     | NMI            | -2           | fixed               | Non-Maskable Interrupt                           |

| 3     | Hard Fault     | -1           | fixed               | Default fault if other hander not<br>implemented |

| 4-10  | Reserved       | N.A.         | N.A.                |                                                  |

| 11    | SVCall         | Programmable | settable            | System Service call                              |

| 12-13 | Reserved       | N.A.         | N.A.                |                                                  |

| 14    | PendSV         | Programmable | settable            | Pendable request for System Device               |

| 15    | SYSTICK        | Programmable | settable            | System Tick Timer                                |

| 16    | Interrupt #0   | Programmable | settable            | External Interrupt #0                            |

|       |                |              | settable            |                                                  |

| 47    | Interrupt#31   | Programmable | settable            | External Interrupt #31                           |

## Vector Table 54

| • | Vector | Table | starts | at | location 0 |  |

|---|--------|-------|--------|----|------------|--|

|---|--------|-------|--------|----|------------|--|

- In the code section of the memory map

- Vector Table contains addresses (vectors)

- of exception handlers and ISRs

- Not instructions

- Table size (in words) is = number of IRQ inputs + 16 •

- Minimum size ( case of 1 IRQ) : 17 words

- Maximum size ( case of 32 IRQs) 48 words

- Main stack pointer initial value in location 0 •

- Set up by hardware during Reset

- Vector Table can not be relocated

- The vector table is always seen at address 0x00000000,

- Different Boot option or memory remap function, allow user to alias at this direction, SRAM, FLASH or System Memory

| Address   | Vector          |

|-----------|-----------------|

| 0x00      | Initial Main SP |

| 0x04      | Reset           |

| 0x08      | NMI             |

| 0x0C      | Hard Fault      |

| 0x10-0x28 | Reserved        |

| 0x2C      | SVCall          |

| 0x30-0x34 | Reserved        |

| 0x38      | PendSV          |

| 0x3C      | Systick         |

| 40        | IRQ0            |

|           | More IRQs       |

# System Timer (SysTick) 55

- Flexible system timer

- 24-bit self-reloading down counter with end of count interrupt generation

- 2 configurable Clock sources (HCLK or HCLK/8)

- Suitable for Real Time OS or other scheduled tasks

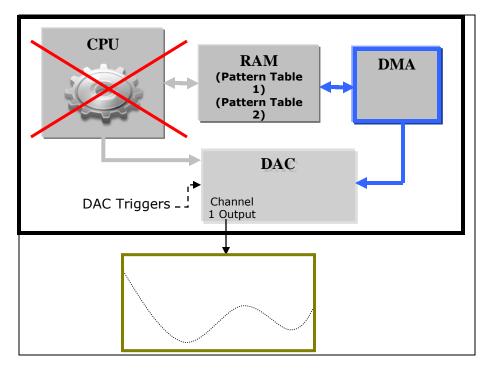

## DIRECT MEMORY ACCESS (DMA)

### DMA Features 57

- 5 independently configurable channels (requests)

- 4 levels of priority settable by software consisting of very high, high, medium, low

- Independent source and destination transfer size (byte, half word, word)

- Support for circular buffer management

- 3 event flags (DMA Half Transfer, DMA Transfer complete and DMA Transfer Error)

- Peripheral-to-memory, memory-to-peripheral, peripheral-to-peripheral & Memory-tomemory transfers

- Access to Flash, SRAM, APB and AHB peripherals as source and destination

- Programmable number of data to be transferred: up to 65536

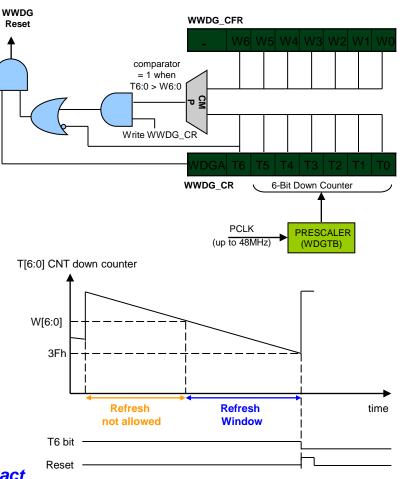

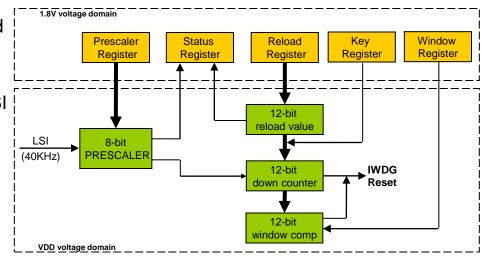

#### **System Peripherals**

## **RESET AND CLOCK CONTROL (RCC)**

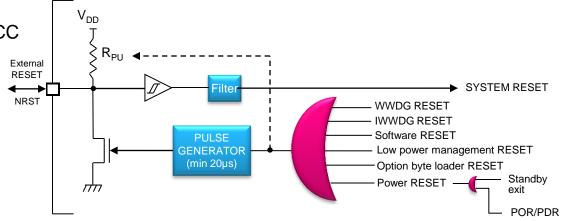

# **RESET Sources**

- System RESET

- Resets all registers except some RCC registers and Backup domain

- Sources

- Low level on the NRST pin (External Reset)

- WWDG end of count condition

- IWWDG end of count condition

- A software reset (through NVIC)

- Low power management reset

- Option byte loader reset (FORCE\_OBL bit)

- Power RESET

- Resets all registers except the Backup domain

- Sources

- Power On/Power down Reset (POR/PDR)

- Exit from STANDBY

- Backup domain RESET

- Resets in the Backup domain: RTC registers + Backup Registers + RCC\_BDCR register

- Sources

- BDRST bit in RCC\_BDCR register

- POWER Reset

60

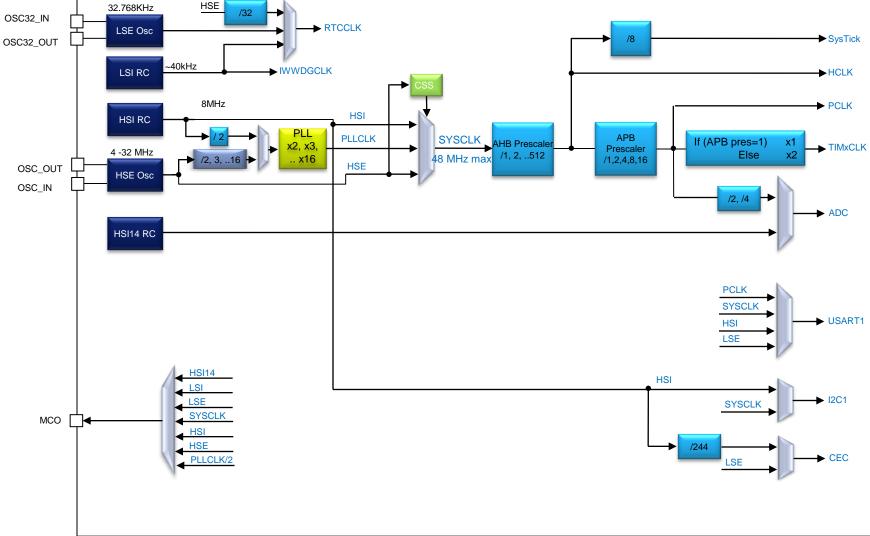

## Clock Features 61

- System Clock (SYSCLK) sources:

- HSE (High Speed External osc) 4MHz to 32MHz, can be bypassed by user clock

- HSI (High Speed Internal RC): factory trimmed internal RC oscillator 8MHz +/- 1%

- PLL x2, x3, .. x16 (16MHz min. output freq.)

- Additional clock sources:

- LSI (Low Speed Internal RC): ~40kHz internal RC

- LSE (Low Speed External oscillator): 32.768kHz, can be bypassed by user clock

- configurable driving strength (power/robustness compromise)

- HSI14 (High Speed Internal RC 14MHz): dedicated oscillator for ADC

- Clock-out capability on the MCO (HSI14, LSI, LSE, SYSCLK, HSI, HSE, PLL/2)

- Clock Security System (CSS) to switch to backup clock in case of HSE clock failure

- Enabled by SW w/ interrupt capability linked to Cortex NMI

- RTC Clock sources: LSE, LSI and HSE clock divided by 32

- USART, I2C & CEC have multiple possible clock sources

### Clock Scheme 62

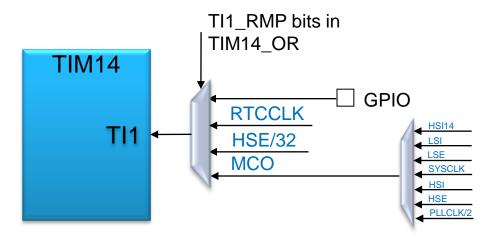

## Internal/External clock measurement using TIM14

- TIM14 input capture can be triggered by an I/O or by RTCCLK, HSE/32 or MCO signal → Purpose:

- Use the precise LSE clock to measure HSI frequency; HSI used as system clock, knowing the LSE frequency we can determine the HSI frequency (w/ the precision of the LSE)

- Measure the LSI frequency (w/ the precision of the HSE or HSI) to fine tune IWWDG and/or RTC timing

- Have rough indication of the external crystal frequency by comparing HSI (used as a system clock) and HSE/32

# POWER CONTROL (PWR)

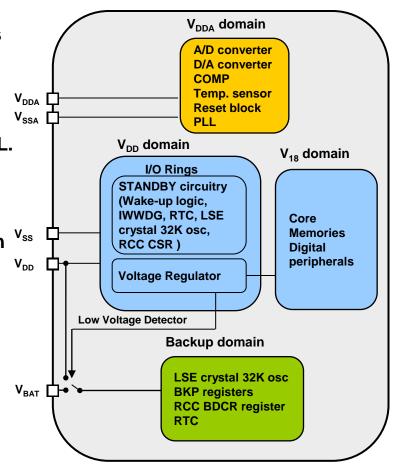

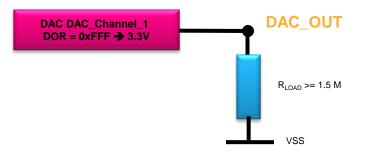

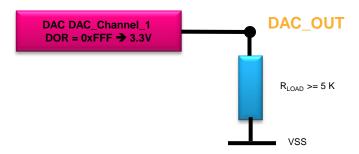

## Power Supply

65

- Power Supply Schemes

- VDD = 2.0 to 3.6 V: External Power Supply for I/Os and the internal regulator.

- VDDA = 2.0 to 3.6 V: External Analog Power supplies for ADC,DAC, Reset blocks, RCs and PLL.

- → ADC or DAC working only if VDDA >=2.4 V

- → VDDA could be higher than VDD

- Full analog performance at low consumption

- VBAT = 1.65V to 3.6 V: For Backup domain when VDD is not present.

- Power pins connection:

- VDD and VDDA can be provided by a separated power supply source.

- VSS and VSSA must be tight to ground

### Power Sequence

66

When VDD power supply source is different from VDDA power supply source (VDD < VDDA)</li>

- The VDDA voltage **level must be always greater or equal** to the VDD voltage

- During power-on, the VDDA must be provided first (before VDD)

- During power-off, it is allowed to have temporarily VDD > VDDA, but the voltage difference must be <0.4V</li>

- could be maintained by an external Schottky diode

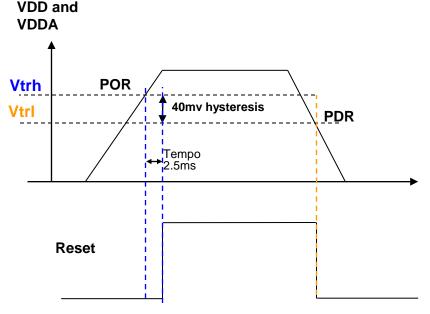

### Power On Reset / Power Down Reset

- Two Integrated POR / PDR circuitries guarantees proper product reset when voltage is not in the product guaranteed voltage range (2V to 3.6V)

- No need for external reset circuit

POR and PDR have a typical hysteresis of 40mV

Vtrl min 1.8V / Vtrh max 2V

68

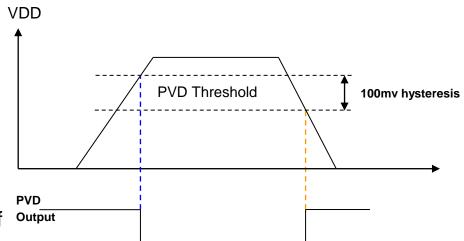

## Programmable Voltage Detector (PVD)

- Programmable Voltage Detector

- Enabled by software

- Monitor the VDD power supply by comparing it to a threshold

- Threshold configurable from 2.1V to 2.9V by step of 90mV

- Generate interrupt through EXTI Line16 (if enabled) when VDD < Threshold and/or VDD > Threshold

- Can be used to generate a warning message and/or put the MCU into a safe state

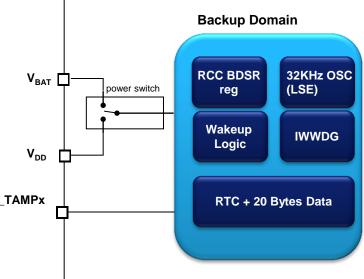

## Backup Domain 69

- Backup Domain contains

- Low power calendar RTC (Alarm, periodic wakeup from Stop/Standby)

- 20 Bytes Data RTC registers

- Separate 32kHz Osc (LSE) for RTC

- RCC BCSR register: RTC clock source selection and enable + LSE config

- → Reset only by RTC domain RESET

- VBAT independent voltage supply

- Automatic switch-over to VBAT when VDD goes lower RTC\_TAMPx than PDR level

- No current sunk on VBAT when VDD present

- Tamper event detection: resets all user backup registers

- TimeStamp event detection.

## Power Management 70

#### 8bit Microcontroller like power mode management

- SLEEP NOW

- "Wait for Interrupt" instructions to enter low power mode

- No more dedicated control register settings sequence

- "Wait for Event" instructions to enter low power mode

- No need of Interrupt to wake-up from sleep

- Rapid resume from sleep

- SLEEP on EXIT

- Sleep request done in interrupt routine

- Low power mode entered on interrupt return

- Very fast wakeup time without context saving (6 cycles)

#### • DEEP SLEEP

- Long duration sleep

- From product side: PLL can be stopped or shuts down the power to digital parts of the system

- Enables low power consumption

### STM32F05x Low Power modes 71

| Mode name                                      | Entry                                                         | Wakeup                                                                                                  | Effect on<br>1.8V<br>domain<br>clocks                                   | Effect on<br>VDD<br>domain<br>clocks | Voltage<br>regulator                                           | IO state                               | Wakeup latency                                                          |

|------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------------------|----------------------------------------|-------------------------------------------------------------------------|

|                                                | WFI                                                           | Any interrupt                                                                                           | CPU CLK                                                                 |                                      |                                                                |                                        |                                                                         |

| SLEEP,<br>SLEEP now<br>or<br>SLEEP on-<br>exit | WFE                                                           | Wake-up event                                                                                           | OFF<br>no effect on<br>other<br>clocks or<br>analog<br>clock<br>sources | None                                 | ON                                                             | All I/O pins<br>keep the<br>same state | None                                                                    |

| STOP                                           | PDDS,<br>LPSDSR<br>bits +<br>SLEEPDEEP<br>bit +<br>WFI or WFE | Any EXTI line<br>(configured<br>in the EXTI registers,<br><u>internal</u> and <u>external</u><br>lines) | All 1.8V<br>domain                                                      | II 1.8V HSI and<br>Iomain HSE and    | ON, in low<br>power<br>mode<br>(dependin<br>g<br>on<br>PWR_CR) | as in the<br>Run mode                  | HSI RC wakeup time<br>+ regulator wakeup<br>time from Low-power<br>mode |

| STANDBY                                        | PDDS bit +<br>SLEEPDEEP<br>bit +<br>WFI or WFE                | WKUP pin rising edge,<br>RTC alarm, RTC tamper<br>event, external reset in<br>NRST pin, IWDG reset      | domain oscillator<br>clocks s<br>OFF OFF                                | OFF                                  | all I/O pins<br>are high<br>impedance<br>(1)                   | Reset phase                            |                                                                         |

Note (1): Standby mode: all I/O pins are high impedance except:

- Reset pad (still available)

- RTC pins, PC14 and PC15 if configured in the RTC registers.

- WKUP pin 1 (PA0) and WKUP pin 2(PC13), if enabled.

### Low Power Modes – typical consumption

- STM32F05x Low Power modes: uses CortexM0 Sleep modes

- SLEEP, STOP and STANDBY

| Feature                                                                                                                    | STM32F05x typ<br>IDD/IDDA (*) |

|----------------------------------------------------------------------------------------------------------------------------|-------------------------------|

| <b>RUN</b> mode w/ execute from <b>Flash</b> on <b>48MHz</b><br>(HSE bypass 8MHz x 6 PLL = 48MHz) All peripherals clock ON | 22.9 / 0.166 (mA)             |

| <b>RUN</b> mode w/ execute from <b>Flash</b> on <b>24MHz</b><br>(HSE bypass 8MHz x 3 PLL = 24MHz) All peripherals clock ON | 11.7 / 0.088 (mA)             |

| <b>RUN</b> mode w/ execute from <b>Flash</b> on <b>8MHz</b><br>(HSI) All peripherals clock ON                              | 4.15 / 0.079 (mA)             |

| Sleep mode w/ execute from Flash at 48MHz<br>(HSI 8MHz / 2 x 12 PLL = 48MHz) All peripherals clock ON                      | 12.9 / 0.243 (mA)             |

| <b>STOP</b> w/ Voltage Regulator in low power<br>All oscillators OFF, PDR on VDDA is OFF                                   | 3.6 / 1.34 (µA)               |

| <b>STANDBY</b> w/ LSI and IWWDG OFF<br>PDR on VDDA is OFF                                                                  | 1.1 / 1.21 (µA)               |

Typical values are measured at TA = 25 °C, VDD = 3.3V VDDA= 3.3 V.

72

System Peripherals

Flash memory

#### Flash Features Overview 74

#### • Flash general features:

- Up to 64KBytes

- 64 pages of 1KBytes size and 16 Sectors of 4KBytes size (4 pages)

- Endurance: 10k cycles

- Access time: 35ns

- Half word (16-bit) program time: 52.5µs (Typ)

- Page erase time and Mass erase time: 20ms (Min), 40ms (Max)

#### • Flash interface features:

- Read Interface with pre-fetch buffer

- Option Bytes loader

- Flash program/erase operations

- Types of Protection:

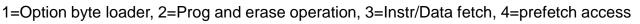

- Readout Protection: Level 0, Level 1 and Level 2 (No debug)

- Write Protection

- Memory organization:

- Main Program memory block (or Main Flash memory)

- Information block : 3KBytes of System memory + 6 Option Bytes (12 with complements)

- 2 option bytes for write protection and 1 for Readout protection

- 1 option byte for device configuration : VDDA supervisor, BOOT1, Reset w/ STDBY/STOP, IWWG HW

- 2 option bytes reserved for user data

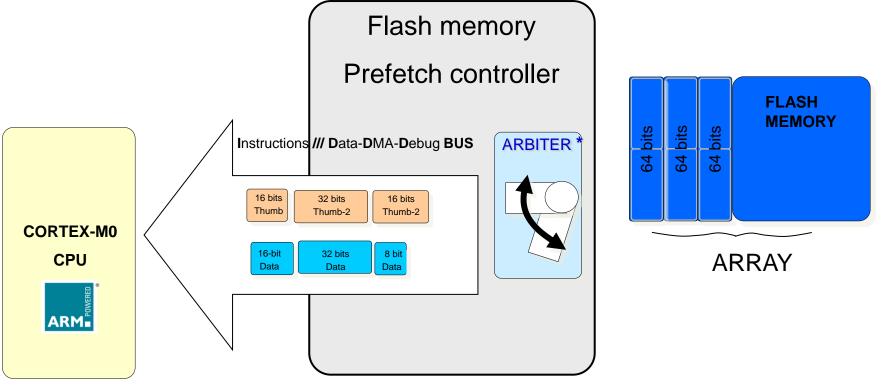

#### Flash memory prefetch controller 75

- Mission: Support 48 MHz operation directly from Flash memory

- Flash with Prefetch based on 3 × 64bits buffers

\* The read requests are managed with following priority order :

Option byte write (RDP level increase) includes: Option byte erase and New option byte programming Option byte write (RDP level decrease) includes: Option byte erase, New option byte programming and Mass Erase Option byte write (RDP level identical) includes : Option byte erase and New option byte programming

### Flash Protections (2/2) 77

#### • Access status versus protection level and execution modes :

| Area                | Protection<br>level | User execution |       | Debug, boot from RAM or<br>boot from system memory<br>(loader) |      |       |       |

|---------------------|---------------------|----------------|-------|----------------------------------------------------------------|------|-------|-------|

|                     |                     | Read           | Write | Erase                                                          | Read | Write | Erase |

| Main                | 1                   | Yes            | Yes   | Yes                                                            | No   | No    | No    |

| memory              | 2                   | Yes            | Yes   | Yes                                                            | N/A  | N/A   | N/A   |

| System              | 1                   | Yes            | No    | No                                                             | Yes  | No    | No    |

| memory              | 2                   | Yes            | No    | No                                                             | N/A  | N/A   | N/A   |

| Option              | 1                   | Yes            | Yes   | Yes                                                            | Yes  | Yes   | Yes   |

| bytes               | 2                   | Yes            | Yes   | No                                                             | N/A  | N/A   | N/A   |

| Backup<br>registers | 1                   | Yes            | Yes   | N/A                                                            | No   | No    | N/A   |

|                     | 2                   | Yes            | Yes   | N/A                                                            | N/A  | N/A   | N/A   |

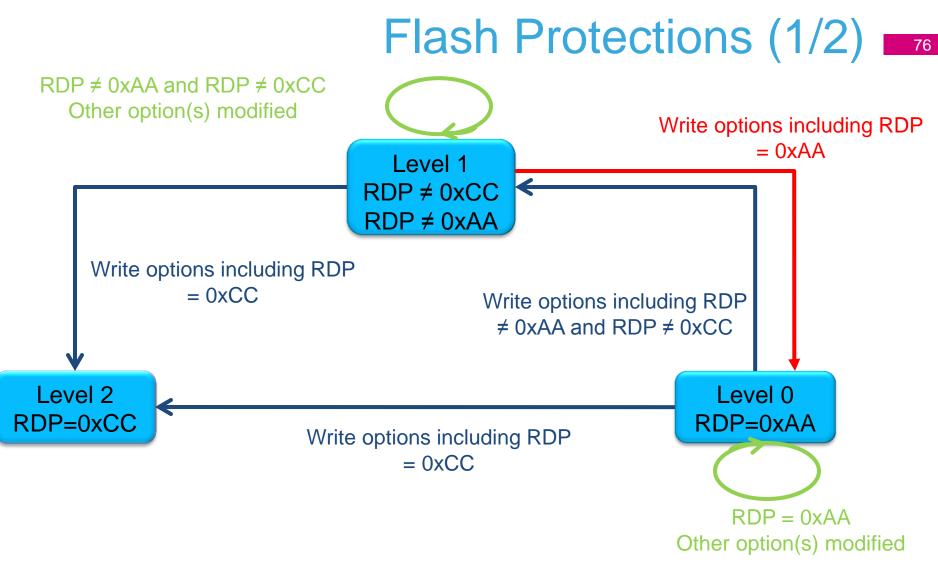

#### Memory Mapping and Boot Modes 78

- Addressable memory space of 4 Gbytes

- FLASH : up to 64 Kbytes

- RAM : up to 8 Kbytes with parity check

- 4 bits per word for parity check

- Automatic check when reading

- NMI/BRK\_IN of TIM1 w/ SRAM\_PARITY\_LOCK bit

- + SRAM\_PEF Error Flag both in SYSCFG register 2

#### **Boot modes**

Depending on the Boot configuration, Embedded Flash memory, System memory or Embedded SRAM memory is aliased at @0x00. Even when aliased, these memories are still accessible from their original memory space.

#### The boot configuration is defined with **BOOT0 pin** and **nBOOT1 bit** from USER option byte.

| BOOT Mode<br>Selection |       | Boot Mode                                                 | Aliasing                                |  |

|------------------------|-------|-----------------------------------------------------------|-----------------------------------------|--|

| nBOOT1                 | воото |                                                           |                                         |  |

| x                      | 0     | User Flash                                                | User Flash is selected as boot space    |  |

| 1                      | 1     | System<br>memorySystemMemory is<br>selected as boot space |                                         |  |

| 0                      | 1     | Embedded<br>SRAM                                          | Embedded SRAM is selected as boot space |  |

System memory : contains the Bootloader used to re-program the FLASH through USART1 (same pins configuration as for STM32 products).

**Boot from SRAM**: The relocation of the vector table is not allowed on the Cortex M0. When Booting from SRAM, System memory or User Flash, the vector table will be aliased at direction 0x00000000

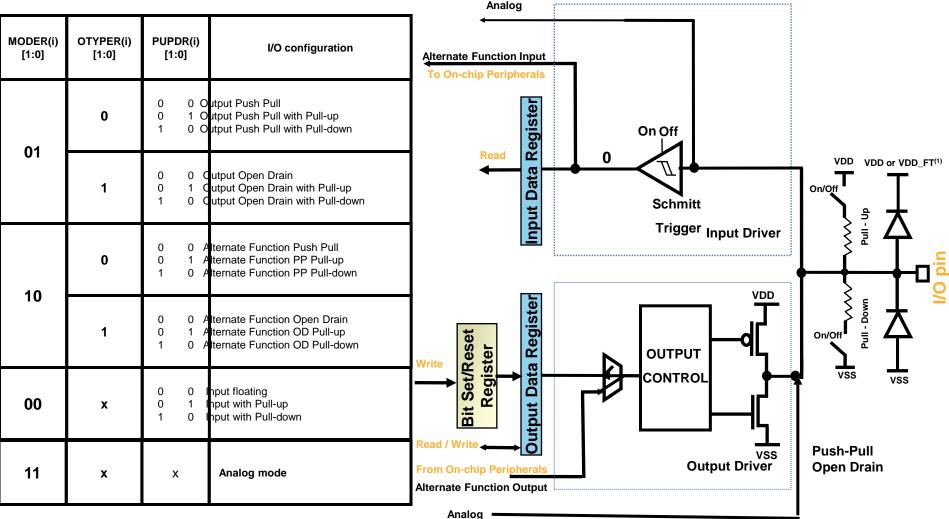

#### GPIO features

80

- Up to 55 multifunction bi-directional I/O ports available on biggest package 64 pin. (86% ratio versus 80% STM32F1 series)

- Almost all standard I/Os are 5V tolerant (except ADC pins)

- All Standard I/Os are shared in 5 ports: GPIOA [0..15], GPIOB[0..15], GPIOC[0..15], GPIOD[2], GPIOF[0,1,4..7]

- Atomic Bit Set and Bit Reset using BSRR and BRR registers

- GPIO connected to AHB bus: max toggling frequency 12 MHz

- Configurable Output slew rate speed up to 50MHz

- Locking mechanism (GPIOx\_LCKR) provided to freeze the I/O configuration on ports A and B

- Up to 55 GPIOs can be set-up as external interrupt (up to 16 lines at time) able to wake-up the MCU from low power modes

### GPIO Configuration Modes 11

\* In output mode, the I/O speed is configurable through OSPEEDR register: 2MHz. 10MHz or 50MHz

(1) VDD\_FT is a potential specific to five-volt tolerant I/Os and different from VDD.

# Analog Peripherals Touch Sensing controller (TSC) Not available on STM32F050x products

### TSC Features (1/2)

- Proven and robust surface charge transfer acquisition principle

- One sampling capacitor for up to 3 capacitive sensing channels to reduce the system components

- Supports up to **18 capacitive sensing channels** split over 6 analog I/O groups

- Up to 6 capacitive sensing channels can be acquired in parallel offering a very good response time

- 1 counter per analog I/O group to store the current acquisition result

- Full hardware management of the charge transfer acquisition sequence

- No CPU load during acquisition

- Spread spectrum feature to improve system robustness in noisy environments (minimum step of 20.8ns)

### TSC Features (2/2)

- Programmable charge transfer frequency (up to 6.8 MHz)

- Programmable sampling capacitor I/O pin and channel I/O pins

- Any GPIO of an analog IO group can be used for the sampling capacitor

- Any GPIO of an analog IO group can be used for the channel

- Programmable max count value to avoid long acquisition when a channel is faulty

- Dedicated end of acquisition and max count error flags with interrupt ۲ capability

- Compatible with proximity, touchkey, linear and rotary touch sensor implementation

- Designed to operate with STMTouch touch sensing firmware library

### STMTouch Touch Sensing Library 55

- Complete free C source code library with firmware examples

- Multifunction capability to combine capacitive sensing functions with traditional MCU features

- Enhanced processing features for optimized sensitivity and immunity

- Calibration, environment control system (ECS), debounce filtering , detection exclusion system (DxS), etc

- Complete and simple API for status reporting and application configuration

- Touchkey, proximity, linear and rotary touch sensors support

- Compliance with MISRA and with all STM32 C compilers

- STM32F051 support planned for end Q2 2012

Similar set as STM32F100x

functionality like STM32F2x

Standard Peripherals

TIMERS (TIM)

#### Timers overview

| Timer | Width<br>&<br>Direction | CAPCOM<br>+<br>COMPL. | Prescaler<br>&<br>Max clock | DMA<br>features | Synch.<br>Module | External<br>trigger | Break | Repetition counter |

|-------|-------------------------|-----------------------|-----------------------------|-----------------|------------------|---------------------|-------|--------------------|

| TIM1  | 16bit<br>UP/DOWN        | 4 + 3                 |                             | All             | Yes              | Yes                 | Yes   | Yes                |

| TIM2  | 32bit<br>UP/DOWN        | 4 + 0                 |                             | All             | Yes              | Yes                 | No    | No                 |

| TIM3  | 16bit<br>UP/DOWN        | 4 + 0                 |                             | All             | Yes              | Yes                 | No    | No                 |

| TIM6  | 16bit<br>UP only        | 0                     | Linear<br>16-bit            | 1 DMA<br>req.   | Yes              | No                  | No    | No                 |

| TIM14 | 16bit<br>UP only        | 1 + 0                 | 48 MHz                      | No              | No               | Yes<br>LSE          | No    | No                 |

| TIM15 | 16bit<br>UP only        | 2 + 1                 |                             | All             | Yes              | No                  | Yes   | Yes                |

| TIM16 | 16bit<br>UP only        | 1 + 1                 |                             | All             | No               | No                  | Yes   | Yes                |

| TIM17 | 16bit<br>UP only        | 1 + 1                 |                             | All             | No               | No                  | Yes   | Yes                |

Only SPI1 available on STM32F050x products

#### SPI Features (1/2)

- Full duplex synchronous transfers (3 lines)

- Half duplex/Simplex synchronous transfers (2 lines, bi-directional data line at half duplex)

- Programmable clock polarity & phase, data MSB/LSB first

- Master/multi Master/Slave operation

- Dynamic software/hardware NSS management (Master/Slave)

- Hardware CRC feature (8-bit & 16-bit data frames checking)

- Flags with IT capability (TxE, RxNE, MODF, OVR, CRCERR)

- Programmable bit rate: up to f<sub>PCLK</sub>/2

- BSY flag (ongoing communication check)

- DMA capability (separated Rx/Tx channels, automatic CRC & <u>Tx/Rx access/threshold handling</u>)

Up to 18 MHz

bit\_rate

#### SPI Features (2/2)

- New enhanced NSS control:

- NSS pulse mode (NSSP)

- TI mode

- Programmable data frame from 4-bit to 16-bit

- Two 32-bit Tx/Rx FIFO buffers with DMA capability

- Data packed mode control

- (I2S mode)

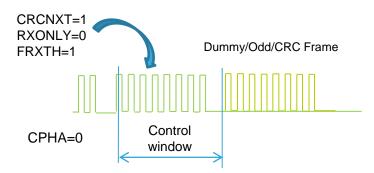

#### Be careful! 91

#### When data packed mode is used

- Keep Rx threshold & read access of Rx FIFO always in line (8-bit/16-bit)

- Change Rx threshold just before last odd data frame is received

#### When go to Halt or when disable the SPI

• check read FIFO occupancy and bus activity (FxLVL[1:0] = 00 & BSY = 0)

#### When communication is continuous (e.g. master Rx-only)

• Perform Rx threshold, change/CRC control or Stop at "Control window"

#### When CRC is enabled at slave

• CRC clock input is sensitive for SCK signal even in case SPIE=0

**Communication Peripherals**

# INTER-INTEGRATED CIRCUIT INTERFACE (I2C)

Only I2C1 available on STM32F050x products

#### I2C Features (1/2)

- I2C specification rev03 compatibility

- SMBus 2.0 HW support

- PMBus 1.1 Compatibility

- Multi Master and slave capability

- Controls all I<sup>2</sup>C bus specific sequencing, protocol, arbitration and timing

- Standard, fast and fast mode + I<sup>2</sup>C mode (up to 1MHz)

- 20mA output drive capability for FM+ mode

### I2C Features (2/2) 94

- 7-bit and 10-bit addressing modes

- Multiple 7-bit Addressing Capability with configurable mask

- Programmable setup and hold time

- Easy to use event management

- Programmable analog and digital noise filter

- Wakeup from STOP mode on address match

- Optional clock stretching

- Independent clock

- 1-byte buffer with DMA capability

#### **I2C Implementation**

- I2C1 supports all features

- I2C2 supports a smaller set of features

| I2C features      | I2C1 | I2C2 |

|-------------------|------|------|

| Independent clock | YES  | NO   |

| SMBUS HW support  | YES  | NO   |

| Wakeup from STOP  | YES  | NO   |

| 20mA output drive | YES  | NO   |

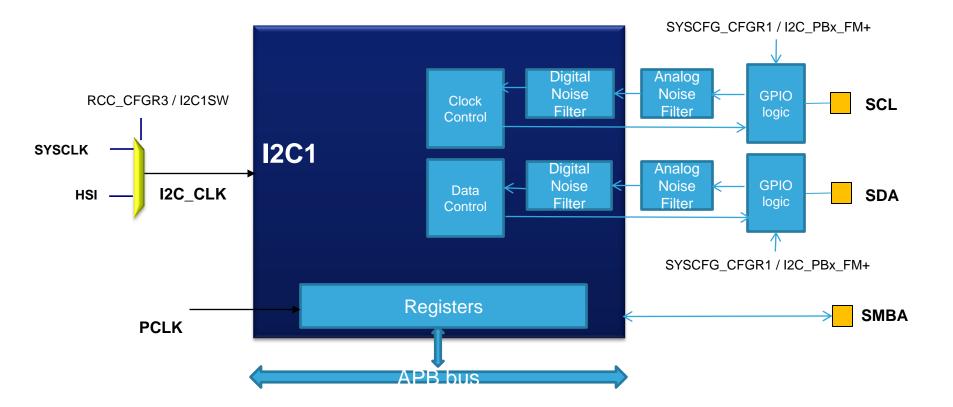

### I2C1 Block Diagram

#### I2C SDA and SCL noise filter

- Analog noise filter in SDA and SCL I/O

- Can filter spikes with a length up to 50ns

- This filter can be enabled or disabled by SW (enabled by default)

- Digital noise filter for SDA and SCL

- Suppress spikes with a programmable length from 0 to 15 I2C\_CLK periods.

- Only analog filter can be enabled when Wakeup from STOP feature is enable.

- Filters configuration must be programmed when the I2C is disable.

### I2C Programmable timings

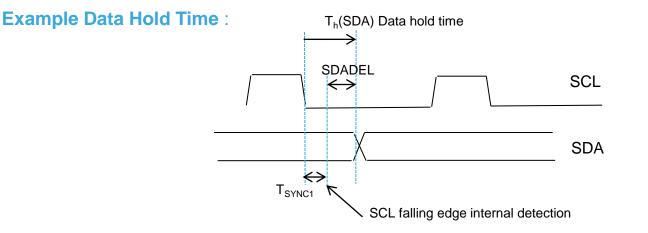

- Setup and Hold timings between SDA and SCL in transmission are programmable by SW with PRESC, SDADEL and SCLDEL fields in I2C Timing Register (I2Cx\_TIMINGR).

- SDADEL is used to generate Data Hold time. T<sub>SDADEL</sub> = SDADEL \* (PRESC+1) \* T<sub>I2C\_CLK</sub>

- SCLDEL is used to generate Data Setup time. T<sub>SCLDEL</sub> = (SCLDEL+1) \* (PRESC+1) \* T<sub>I2C\_CLK</sub>

- The Setup and Hold configuration must be programmed when the I2C is disable.

- I2C\_Timing\_Config\_Tool is available in FWLib to calculate I2C\_TIMINGR value for your application.

98

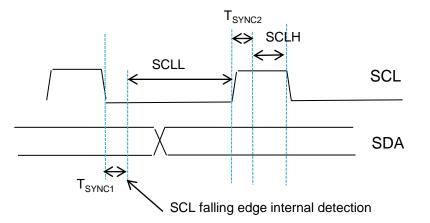

#### I2C Master clock generation

- SCL Low and High duration are programmable by SW with PRESC, SCLL and SCLH fields in I2C Timing Register (I2Cx\_TIMINGR).

- SCL Low counter is (SCLL+1) \* (PRESC+1) \* T<sub>I2C\_CLK</sub>. It starts counting after SCL falling edge internal detection. After counting, SCL is released.

- SCL High counter is (SCLH+1) \* (PRESC+1) \* T<sub>I2C\_CLK</sub>. It starts counting after SCL rising edge internal detection. After counting SCL is driven low.

- The total SCL period is :

TSYNC1 + TSYNC2 + [(SCLL+1) + (SCLH+1)] \* (PRESC+1) \* T<sub>I2C\_CLK</sub>

SCL Period:

- The SCLL and SCLH configuration must be programmed when the I2C is disable.

- I2C\_Timing\_Config\_Tool is available in FWLib to calculate I2C\_TIMINGR value for your application.

#### Slave Addressing Mode 100

- I2C can acknowledge several slave addresses. 2 address registers :

- I2Cx\_OAR1 : 7-bit or 10-bit mode.

- I2Cx\_OAR2 : 7-bit mode only. OA2MSK[2:0] allow to mask from 0 to 7

LSB of OAR2 :

| OA2MSK[2:0] | Address match condition                                       |

|-------------|---------------------------------------------------------------|

| 000         | address[7:1] = OA1[7:1]                                       |

| 001         | address[7:2] = OA1[7:2] (Bit 1 is don't care)                 |

| 010         | address[7:3] = OA1[7:3] (Bit 2:1 are don't care)              |

|             |                                                               |

| 111         | All addresses are acknowledged except I2C reserved addresses. |

### Wakeup from STOP on address match

- When I2C\_CLK clock is HSI, the I2C is able to wakeup MCU from STOP when it receives its slave address. All addressing mode are supported.

- During STOP mode and no address reception : HSI is switched off.

- On START detection, I2C enables HSI, used for address reception.

- Wakeup from STOP is enabled by setting WUPEN in I2C1\_CR1.

- Clock stretching must be enabled to ensure proper operation: NOSTRETCH=0.

101

#### 12C events 102

| Interrupt flag |

|----------------|

| RXNE           |

| TXIS           |

| STOPF          |

| TCR            |

| TC             |

| ADDR           |

| NACKF          |

|                |

#### Easy Master mode management

#### • For payload <= 255 bytes : **only 1 write action needed** !! (apart data rd/wr)

- START=1

- I2Cx\_CR2 is written w/ :

- SADD : slave address

- RD\_WRN : transfer direction

- NBYTES = N : number of bytes to be transferred

- **AUTOEND** =1 : STOP automatically sent after N data.

#### AUTOEND

| 0 : Software end mode  | <ul> <li>End of transfer SW control after NBYTES data transfer :</li> <li>TC flag is set. Interrupt if TCIE=1.</li> <li>TC is cleared when START or STOP is set by SW</li> <li>➢ If START=1 : RESTART condition is sent</li> </ul> |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        |                                                                                                                                                                                                                                    |

| 1 : Automatic end mode | STOP condition sent after NBYTES data transfer                                                                                                                                                                                     |

Data transfer managed by Interrupts (TXIS / RXNE) or DMA

#### Easy to use event management 104

• For payload > 255 : in addition, **RELOAD** must be set in I2Cx\_CR2.

| RELOAD          |                                                                                                                                                                                                               |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0 : No reload   | NBYTES data transfer is followed by STOP or ReSTART                                                                                                                                                           |  |

| 1 : Reload mode | <ul> <li>NBYTES is reloaded after NBYTES data transfer (data transfer will continue) :</li> <li>TCR flag is set. Interrupt if TCIE=1.</li> <li>TCR is cleared when I2Cx_CR2 is written w/ NBYTES≠0</li> </ul> |  |

• AUTOEND = 0 has no effect when RELOAD is set.

## Slave mode

105

• By default : I2C slave uses clock stretching .

➤This can be disabled by setting NOSTRETCH=1

- Reception : Acknowledge control can be done on selected bytes in Slave Byte Control (SBC) mode with RELOAD=1

- SBC = 1 enables the NBYTES counter in slave mode (Tx and Rx modes).

- SBC = 1 is allowed only when NOSTRETCH=0.

|                                   | SBC                                                                                                                                                                                                                                         |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 : Slave Byte<br>Control disable | All received bytes are acknowledged.                                                                                                                                                                                                        |

| 1 : Slave Byte<br>Control enable  | <pre>If RELOAD=1, after NBYTES data are transferred : • TCR set &amp; SCL stretched before ACK pulse in reception. • TCR is cleared when I2Cx_CR2 is written w/ NBYTES≠0 &gt; if I2Cx_CR2/NACK = 1: received byte is NOT Acknowledged</pre> |

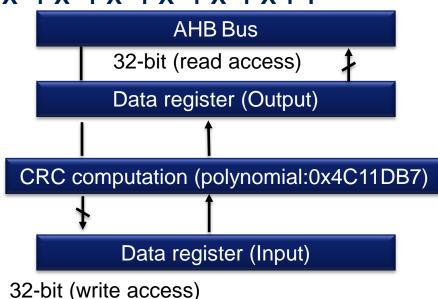

# CRC Features (1/3)

107

- CRC-based techniques are used to verify storage integrity or data transmission

- In functional safety standards (such as EN/IEC 60335-1), CRC peripheral offers a means of verifying the embedded Flash memory integrity

- Uses CRC-32 (Ethernet) polynomial: 0x4C11DB7 :

#### $X^{32}$ + $X^{26}$ + $X^{23}$ + $X^{22}$ + $X^{16}$ + $X^{12}$ + $X^{11}$ + $X^{10}$ + $X^8$ + $X^7$ + $X^5$ + $X^4$ + $X^2$ + X + 1

- Single input/output 32-bit data register, but handles 8,16 and 32-bits data size

- CRC Peripheral is mapped to AHB bus for fast operation, CRC computation done in 4 AHB clock cycles (HCLK) maximum

- Computation duration depends on data size

- 4 HCLK cycles for 32-bit

- 2 HCLK cycles for 16-bit

- 1 HCLK cycles for 8-bit

# CRC Features (2/3) 108

- The Input register can be accessed for write operations either :

- by Cortex-M0 CPU or

- In back-to-back with DMA in Memory to Memory transfer mode, keeping CPU free for other tasks or even in sleep mode (for power optimization)

- A **new Input buffer** is available to avoid AHB bus stall during computation time, thus freeing AHB1 bus for others concurrent operations

- It has also a general-purpose 8-bit register (can be used for temporary storage)

#### **New Modes**

- Programmable <u>CRC initial value</u>, very useful when the CRC computation is stopped then continued without re-start again in the application ( Interrupts with higher priorities, several CRC computations etc.)

- Initial value is re-loaded from CRC\_INIT (32-bits register) each time a CRC reset is applied, the default value is 0xFFFF\_FFFF to keep compatibility with STM32F1xx series

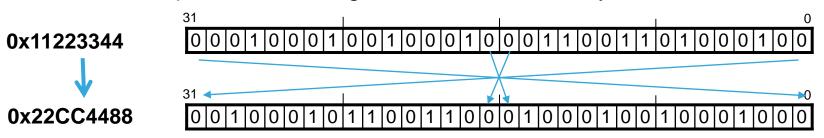

# CRC Features (3/3)

- New Modes (Continued)

- Reversibility on Input and Output data without extra cycles