# STM32 Updates for technical development community

**Microcontrollers Division**

2012 - 1<sup>st</sup> Issue

# Contents 2

- Documents Major Updates

- STM32 (Errata, Datasheets, Reference Manual, Application notes)

- STM32 technical presentations

- DSP and FPU Application Notes & Demo presentation

- STM32F4xx Memories and Bus Matrix

- Support Status and Major Requests/Hits

- AMR (Absolute Maximum Ratings) and current injection

- ADC : how to choose the right sampling time ?

- PC Software (Flash Loader & DFuSe) update

- Conclusion With the Hits/Tips of the last period

# Contents 3

- Documents Major Updates

- STM32 (Errata, Datasheets, Reference Manual, Application notes)

- STM32 technical presentations

- DSP and FPU Application Notes & Demo presentation

- STM32F4xx Memories and Bus Matrix

- Support Status and Major Requests/Hits

- AMR (Absolute Maximum Ratings) and current injection

- ADC : how to choose the right sampling time ?

- PC Software (Flash Loader & DFuSe) update

- Conclusion With the Hits/Tips of the last period

# **Documents Major Updates**

# Documents Major Updates Overview

- STM32F205x and STM32F207x datasheet Rev8 (On Web)

- STM32F215x and STM32F217x datasheet Rev6 (On Web)

- STM32F40xx and STM32F41xx datasheet Rev2 (On Web)

- STM32F103xFG datasheet Rev3 (On Web)

- STM32F100BDIE STM32 value line die Specification Rev2 (On Web)

- STM32F20x and STM32F21x Errata sheet Rev2 (On Web) STM32F40x STM32F41x Errata sheet - Rev2 (On Web) STM32F105/107xx Errata sheet - Rev8 (On Web)

- AN2606 "STM32 microcontroller system memory boot mode" Rev13 AN2586 "STM32F10xxx hardware getting started" Rev7 (On Web)

### STM32 Documents Major Updates (1/11)

### STM32F20xx Datasheet Rev8 STM32F21xx Datasheet Rev6 (On Web)

- Add FSMC, SDIO, ULPI, Ethernet MII and RMII setup/hold timings

- OTG FS external PHY was removed.

- OTG\_FS\_SDA, OTG\_FS\_SCL and OTG\_FS\_INTN alternate functions removed.

- NEW: Added maximum power consumption at TA=25 °C for STOP mode.

|        |                                                                                  |                                                                                                                                                  | Тур                       |                           | Max                       |                            |      |

|--------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------------|---------------------------|----------------------------|------|

| Symbol | Parameter                                                                        | Conditions                                                                                                                                       | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |

|        | Supply current<br>in Stop mode                                                   | Flash in Stop mode, low-speed and high-speed<br>internal RC oscillators and high-speed oscillator<br>OFF (no independent watchdog)               | 0.55                      | 1.2                       | 11.00                     | 20.00                      |      |

|        | with main<br>regulator in<br>Run mode                                            | Flash in Deep power down mode, low-speed<br>and high-speed internal RC oscillators and<br>high-speed oscillator OFF (no independent<br>watchdog) | 0.50                      | 1.2                       | 11.00                     | 20.00                      | mA   |

|        | Supply current<br>in Stop mode<br>with main<br>regulator in<br>Low Power<br>mode | Flash in Stop mode, low-speed and high-speed<br>internal RC oscillators and high-speed oscillator<br>OFF (no independent watchdog)               | 0.35                      | 1.1                       | 8.00                      | 15.00                      | ma   |

|        |                                                                                  | Flash in Deep power down mode, low-speed<br>and high-speed internal RC oscillators and<br>high-speed oscillator OFF (no independent<br>watchdog) | 0.30                      | 1.1                       | 8.00                      | 15.00                      |      |

Table 20. Typical and maximum current consumptions in Stop mode<sup>(1)</sup>

# STM32 Documents Major Updates (2/11) 7

### STM32F4xxx Datasheet Rev2 (On Web)

- Add New WLCSP90 Package (Pinout will be described in Rev3)

- New pins table definitions:

|        | Pir     | n nur   | nber       |         | <b>D</b> .                                           | 0        | ure            |       |                                                    |                      |

|--------|---------|---------|------------|---------|------------------------------------------------------|----------|----------------|-------|----------------------------------------------------|----------------------|

| LQFP64 | LQFP100 | LQFP144 | UFBGA176   | LQFP176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I/ O structure | Notes | Alternate functions                                | Additional functions |

|        |         |         |            |         |                                                      |          |                |       |                                                    |                      |

| -      | 1       | 1       | <b>A</b> 2 | 1       | PE2                                                  | I/O      | FT             |       | TRACECLK/ FSMC_A23 /<br>ETH_MII_TXD3 /<br>EVENTOUT |                      |

STM32F41x pin and ball definitions Table 6.

- "Notes" column : handle special pins and exceptions

- Differentiate

- Alternate functions: Functions selected through GPIOx\_AFR registers

- Additional functions : Functions directly selected/enabled through peripheral registers

# STM32 Documents Major Updates (3/11)

### STM32F4xxx Datasheet Rev2 (On Web)

- Some important Highlights in datasheet versus F2 series

- Table 12 : Limitations depending on the operating power supply range

- Prefetch is not available for VDD=1.8 to 2.1Volt range Refer to AN3430 application note for details on how to adjust performance and power.

- HSE in bypass mode can have an external Frequency up to 50MHz instead of 26MHz

| Symbol               | Parameter                                              | Conditions | Min | Тур | Max | Unit |

|----------------------|--------------------------------------------------------|------------|-----|-----|-----|------|

| f <sub>HSE_ext</sub> | External user clock source<br>frequency <sup>(1)</sup> |            | 1   | 8   | 50  | MHz  |

#### High-speed external user clock characteristics Table 26.

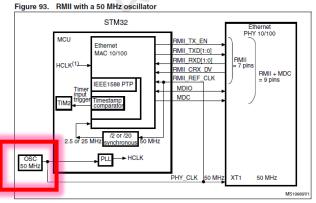

Ethernet Interface with External PHY for RMII mode ۲

1. fHCLK must be greater than 25 MHz.

# STM32 Documents Major Updates (4/11)

### STM32F4xxx Datasheet Rev2 (On Web)

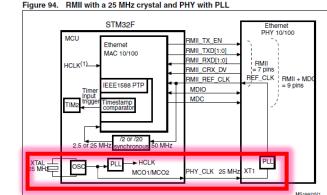

- Most of Parametrics are now available

- Typical and maximum current consumption in RUN/Sleep, STOP, Standby and VBAT modes

- · Exception with Max in Standby and VBAT mode when RTC and LSE is ON, still TBD, but new curves added for temperature variation on typical devices

# STM32 Documents Major Updates (5/11) 10

### STM32F4xxx Datasheet Rev2 (On Web)

#### Most of Parametric are now available

New section added "I/O dynamic current consumption", When an I/O pin switches, it uses the current from the MCU supply voltage to supply the I/O pin circuitry and to charge/discharge the capacitive load (internal or external) connected to the pin:

#### $I = VDD^* Fsw^* C$

Where

- I is the current sunk by a switching I/O to charge/discharge the capacitive load

- VDD is the MCU supply voltage

- **F**<sub>sw</sub> is the I/O switching frequency

- C is the total capacitance seen by the I/O pin:  $C = C_{INT} + C_{FXT}$

The test pin is configured in push-pull output mode and is toggled by software at a fixed frequency

#### Table 23. Switching output I/O current consumption

| Symbol | Parameter                | Conditions <sup>(1)</sup>                                                | I/O toggling<br>frequency (f <sub>SW</sub> ) | Тур  | Unit        |

|--------|--------------------------|--------------------------------------------------------------------------|----------------------------------------------|------|-------------|

|        |                          |                                                                          | 2 MHz                                        | 0.02 |             |

|        |                          | V <sub>DD</sub> = 3.3 V <sup>(2)</sup>                                   | 8 MHz                                        | 0.14 | ţ           |

|        |                          | $C = C_{INT}$                                                            | 25 MHz                                       | 0.51 | Ī           |

|        |                          |                                                                          | 50 MHz                                       | 0.86 | Ī           |

|        |                          |                                                                          | 60 MHz                                       | 1.30 | Ι           |

|        |                          |                                                                          | 2 MHz                                        | 0.10 |             |

|        |                          | V <sub>DD</sub> = 3.3 V                                                  | 8 MHz                                        | 0.38 | Ι           |

|        |                          | C <sub>EXT</sub> = 0 pF                                                  | 25 MHz                                       | 1.18 |             |

|        | I/O switching<br>current | $C = C_{INT} + C_{EXT} + C_S$                                            | 50 MHz                                       | 2.47 | -           |

|        |                          |                                                                          | 60 MHz                                       | 2.86 |             |

|        |                          | $V_{DD} = 3.3 V$ $C_{EXT} = 10 \text{ pF}$ $C = C_{INT} + C_{EXT} + C_S$ | 2 MHz                                        | 0.17 | I           |

|        |                          |                                                                          | 8 MHz                                        | 0.66 | mA          |

| IDDIO  |                          |                                                                          | 25 MHz                                       | 1.70 |             |

|        |                          |                                                                          | 50 MHz                                       | 2.65 |             |

|        |                          |                                                                          | 60 MHz                                       | 3.48 |             |

|        |                          |                                                                          | 2 MHz                                        | 0.23 | Ī           |

|        |                          | V <sub>DD</sub> = 3.3 V                                                  | 8 MHz                                        | 0.95 | -<br>-<br>- |

|        |                          | C <sub>EXT</sub> = 22 pF                                                 | 25 MHz                                       | 3.20 |             |

|        |                          | $C = C_{INT} + C_{EXT} + C_{S}$                                          | 50 MHz                                       | 4.69 |             |

|        |                          |                                                                          | 60 MHz                                       | 8.06 | Ī           |

# STM32 Documents Major Updates (6/11) 11

### STM32F4xxx Datasheet Rev2 (On Web)

- Most of Parametrics are now available

- Typical Peripherals Current consumption at 168MHz and 144MHz are added ( AHB1,AHB2, AHB3, APB1 and APB2).

- Analog Parametric :

- ADC : Frequency up to 36MHz, but characterization is done and provided only for 30MHz as F2. still on-going to get new data.

- Digital Parametric:

- USB ULPI : added

- Ethernet RMII : added

- FSMC : added

- SPI/I2S/SDIO and Ethernet MII/SMI are planned for Rev3

## STM32 Documents Major Updates (7/11) 12

- STM32F103xFG Datasheet Rev3 (On Web)

- Added FSMC and SDIO timings characterization

- STM32F105/7xx Errata sheet Rev8 (On Web)

- Bootloader limitations moved to AN2606 in "Bootloader version" section

- AN2586 "STM32F10xxx hardware getting started" Rev7 (On Web)

- Added support of STM32F103xFG devices

# STM32 Documents Major Updates (8/11) 13

### AN2606 "STM32 microcontroller system memory boot mode" Rev13

- Add support for STM32F100xxx and STM32F4xxx devices

- New bootloader limitation added in "Bootloader version" section for bootloader V2.0

- New bootloader version V2.1 is available

- Title : PA9 excessive power consumption when **USB** cable is plugged in bootloader V2.0

- Description

- When connecting an USB cable after booting from System-Memory mode, PA9 pin (connected to VBUS=5 V) is also shared with USART TX pin which is configured as alternate push-pull and forced to 0 since the USART peripheral is not yet clocked.

- As a consequence, a current higher than 25 mA is drained by PA9 I/O and may affect the I/O pad reliability.

- Workaround

- None.

- Limitation fixed in STM32F105xx/107xx bootloader V2.1. A PIL was sent to our customers

# STM32 Documents Major Updates (9/11) 14

### STM32F20x and STM32F21x Errata sheet Rev2 (on web)

- Title : ART Accelerator prefetch queue instruction is not supported

- Description ٠

- The ART Accelerator prefetch queue instruction is not supported when VDD is lower than 2.1V. This limitation does not prevent the ART Accelerator from using the cache enable/disable capability and the selection of the number of wait states according to the system frequency.

- Workaround

- None. Refer to application note AN3430 for details on how to adjust performance and power consumption.

# STM32 Documents Major Updates (10/11) 15

### STM32F40x STM32F41x Errata sheet Rev2 (on web)

- Title : ART Accelerator prefetch queue instruction is not supported

- Description ٠

- The ART Accelerator prefetch queue instruction is not supported on revision A devices. This limitation does not prevent the ART Accelerator from using the cache enable/disable capability and the selection of the number of wait states according to the system frequency..

- Workaround :

- Revision A devices: None

- Revision Z devices: Fixed.

## STM32 Documents Major Updates (11/11) 16

### STM32F20x and STM32F21x Errata sheet Rev2 (on web) STM32F40x STM32F41x Errata sheet Rev2 (on web)

- Title : Configuration of PH10 and PI10 as external interrupts is erroneous

- Description :

- PH10 or PI10 are selected as source for EXTI10 external interrupt by setting bits EXTI10[3:0] of SYSCFG\_EXTICR3 register to 0x0111 or 0x1000, respectively. However, this operation erroneous enables PH2 and PI2 as external interrupt inputs.

- As a result, it is not possible to use PH10/PI10 as interrupt sources if PH2/PI2 are not selected as interrupt source. as well. This means that bits EXTI10[3:0] of SYSCFG\_EXTICR3 register and bits EXTI2[3:0] of SYSCFG\_EXTICR1 should be programmed to the same value:

- 0x0111 to select PH10/PH2

- 0x1000 to select PI10/PI2

- Workaround

- None.

# Contents 17

- Documents Major Updates

- STM32 (Errata, Datasheets, Reference Manual, Application notes)

### STM32 technical presentations

- DSP and FPU Application Notes & Demo presentation

- STM32F4xx Memories and Bus Matrix

- Support Status and Major Requests/Hits

- AMR (Absolute Maximum Ratings) and current injection

- ADC : how to choose the right sampling time ?

- PC Software (Flash Loader & DFuSe) update

- Conclusion With the Hits/Tips of the last period

2012 STM32 Technical Updates - Issue 1 28/05/2012

# AN4044 : STM32F4 FPU Application Note and Demo

# FPU usage

# Overview 20

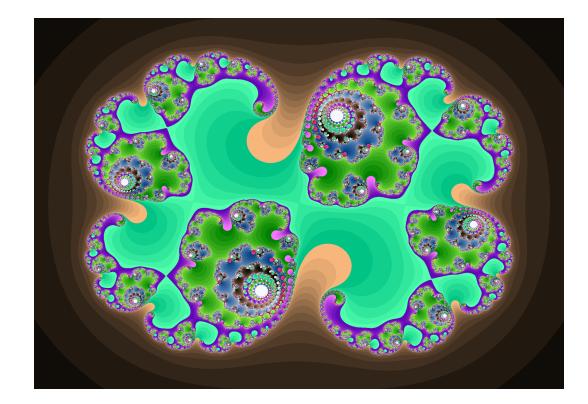

- The demonstration shows the benefit of FPU on a simple algorithm computing the Julia set fractal

- It consists in computing a mathematical sequence for each point of the complex plan and show the speed of divergence for each point

- The mathematical sequence is a complex square elevation with the addition of a constant

# Graphical results 21

Associating a color with the divergence speed creates some very nice graphics we all know

# FPU efficiency

- The FPU permits a x11.5 acceleration for a complete image calculation

- The calculation takes for the complete image 222ms with the FPU used and 2.597s without !

- Any application using floats can benefit of such an acceleration (audio decoding/processing, loop control, digital filtering...etc....)

Measures done with MDK-ARM (4.22a) toolchain Level 3(-O3) for time optimization without MicroLib

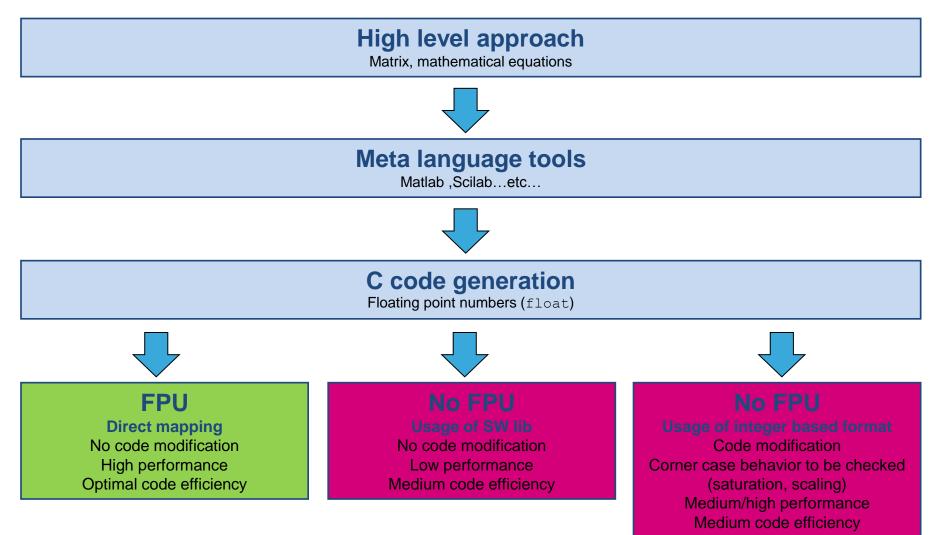

# AN4004: Using STM32F2 & STM32F4 in DSP applications

# AN4004 Scope & Overview

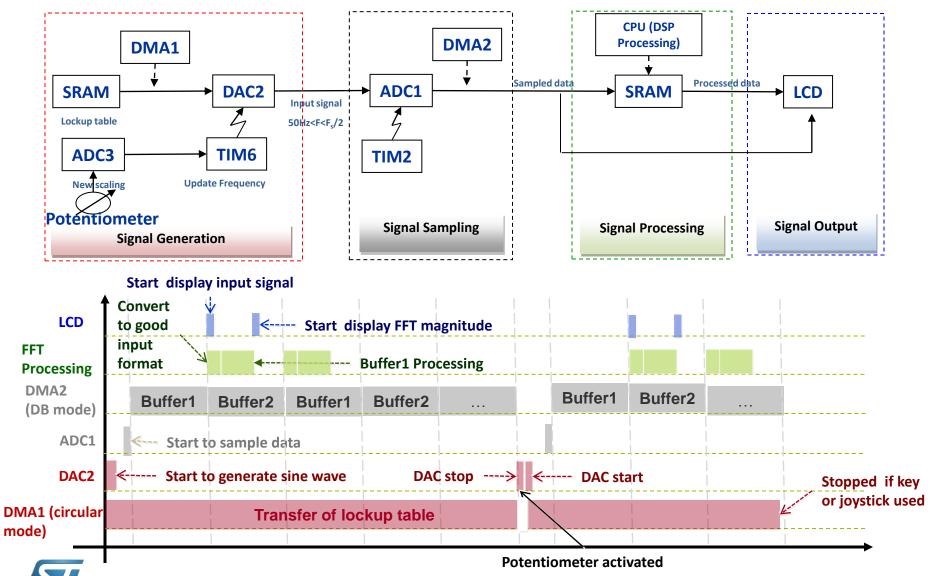

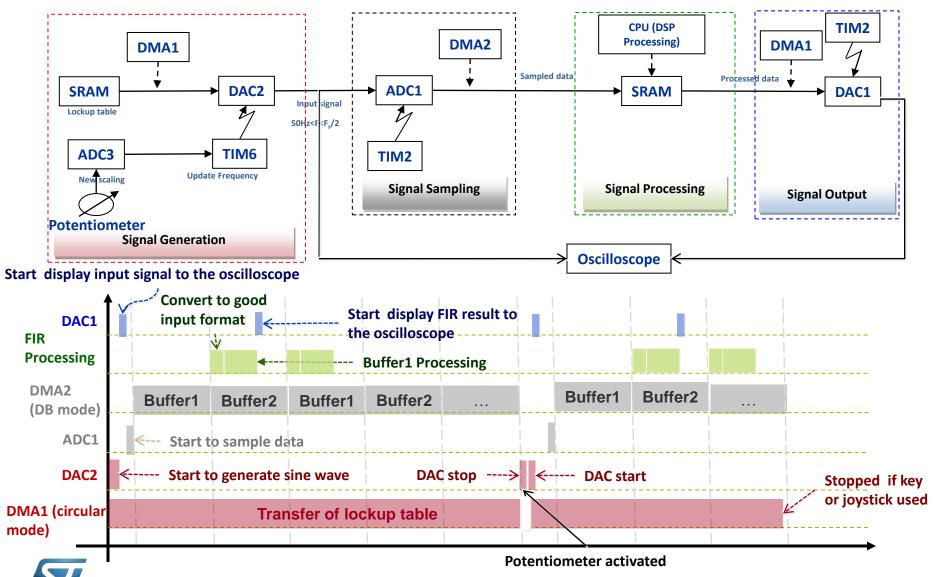

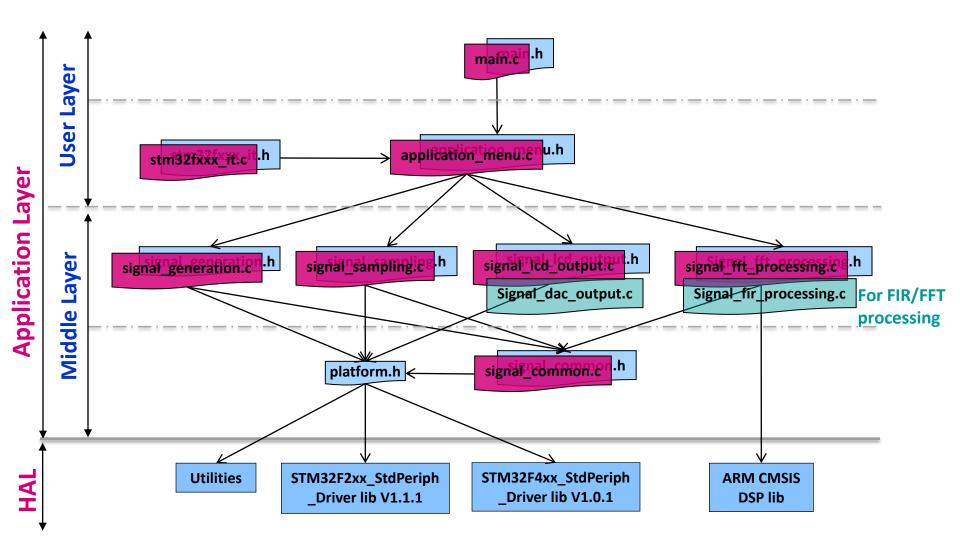

This application note (To be published on web : June 2012) describes how to take advantage of the new ARM DSP CMSIS library & use it with STM32F2 or STM32F4. It provides a firmware implementing FIR (Finite impulse response) filtering and FFT (Fast Fourier transform) as DSP examples with Fixed & Floating point data as input.

### The following items are described in this AN

- Overview of main features of STM32F4xx compared to STM32F2xx

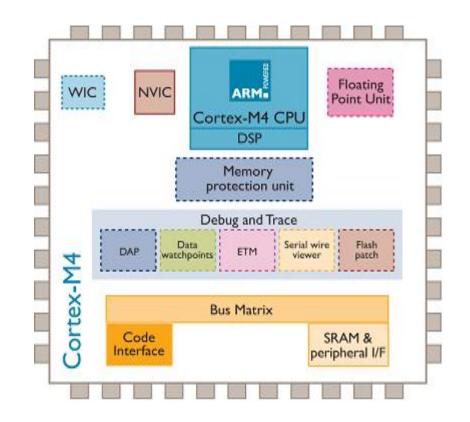

- Cortex-M4F Architecture & main features

- Overview of the CMSIS DSP library

- FIR & FFT Examples

- A small description

- The hardware setup

- The firmware architecture

- The benchmarking results

# Cortex-M4F main features 25

- FPU

- Single-cycle SIMD instructions

- Saturated arithmetic

- Barrel shifter

- 8-bit & 16-bit packed data types

# FFT: Hardware setup & data flow

life.augmented

2012 STM32 Technical Updates - Issue 1 28/05/2012

# FIR: Hardware setup & data flow

life.augmented

# Firmware architecture 28

# FFT Benchmarking results Setup

| Input signal characteristics |                                                                  |  |  |  |

|------------------------------|------------------------------------------------------------------|--|--|--|

| Input signal                 | a sine wave with a frequency F<br>50Hz <f<4khz< th=""></f<4khz<> |  |  |  |

| Sampling frequency           | 8KHz                                                             |  |  |  |

Measures done with MDK-ARM (4.23.00.0) toolchain Level 3(-O3) for time optimization without MicroLib

29

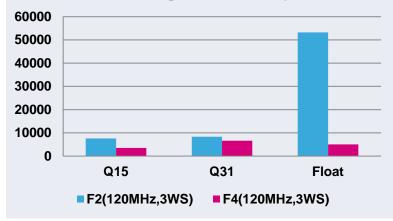

# FFT Benchmarking results Cortex-M3 vs Cortex-M4F

# FFT 64-points average processing time (# cycles)

# FFT 1024-points average processing time (# cycles)

|                      |       | F2(120MHz,3WS)<br>(#cycles) | F4(120MHz,3WS)<br>(#cycles) | Gain   |                       |

|----------------------|-------|-----------------------------|-----------------------------|--------|-----------------------|

|                      | Q15   | 7613                        | 3537                        | x 2.15 | F2: SW Floating Point |

| FFT<br>(64-points)   | Q31   | 8362                        | 6656                        | x 1.25 | F4: HW FPU used       |

| (0 . po              | Float | 53233                       | 5038                        | x 10   | r4. HVV PPO useu      |

|                      | Q15   | 192008                      | 82174                       | x 2.33 |                       |

| FFT<br>(1024-points) | Q31   | 219077                      | 169484                      | x 1.3  |                       |

|                      | Float | 1550715                     | 121801                      | x 12   |                       |

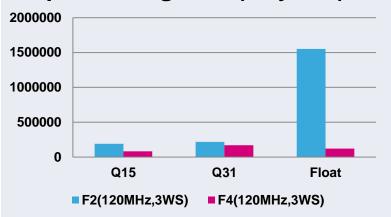

# FFT Benchmarking results F2 vs F4

# FFT 64-points average processing time (µs)

# FFT 1024-points average processing time (µs)

|                       |       | F2(120MHz,3WS)<br>(μs) | F4(168MHz,5WS)<br>(μs) | Gain   |                       |

|-----------------------|-------|------------------------|------------------------|--------|-----------------------|

|                       | Q15   | 63.442                 | 22.101                 | x 2.9  |                       |

| FFT (64-<br>points)   | Q31   | 69.683                 | 40.679                 | x 1.7  | F2: SW Floating Point |

| pointoj               | Float | 443.608                | 30.988                 | x 14.3 | F4: HW FPU used       |

| FFT (1024-<br>points) | Q15   | 1600.067               | 496.952                | x 3.22 |                       |

|                       | Q31   | 1825.642               | 1021.208               | x 1.7  |                       |

| P                     | Float | 12922.625              | 737.333                | x 17.5 |                       |

# FIR benchmarking results Setup

| Filter & input signal characteristics |                                                                  |  |  |  |  |

|---------------------------------------|------------------------------------------------------------------|--|--|--|--|

| Filter type                           | Stop Band                                                        |  |  |  |  |

| Filter order                          | 165                                                              |  |  |  |  |

| Filter coefficients                   | 166                                                              |  |  |  |  |

| Cut-off frequency                     | F <sub>STOP1</sub> =1.9KHz, F <sub>STOP2</sub> =2.1KHz           |  |  |  |  |

| Sampling frequency                    | 48KHz                                                            |  |  |  |  |

| Number of samples                     | 128                                                              |  |  |  |  |

| Input signal                          | a sine wave with a frequency F<br>50Hz <f<4khz< td=""></f<4khz<> |  |  |  |  |

Measures done with MDK-ARM (4.23.00.0) toolchain Level 3(-O3) for time optimization without MicroLib

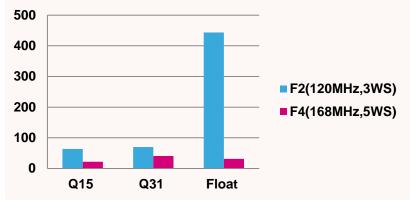

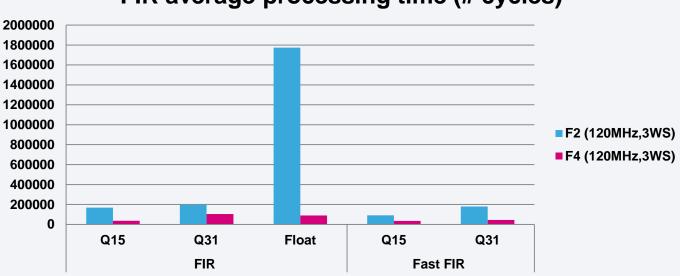

### FIR Benchmarking results Cortex-M3 vs Cortex-M4F

### FIR average processing time (# cycles)

|          |       | F2(120MHz,3WS)<br>(#cycles) | F4(120MHz,3WS)<br>(#cycles) | (gain)  |

|----------|-------|-----------------------------|-----------------------------|---------|

|          | Q15   | 167639                      | 36620                       | ~ x 4.5 |

| FIR      | Q31   | 196399                      | 104105                      | ~ x 1.9 |

|          | Float | 1773901                     | 89439                       | ~ x 19  |

| Eact EID | Q15   | 91281                       | 35293                       | ~ x 2.5 |

| Fast FIR | Q31   | 178595                      | 45034                       | ~ x 4   |

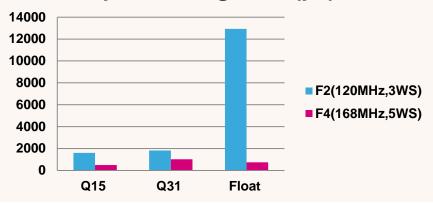

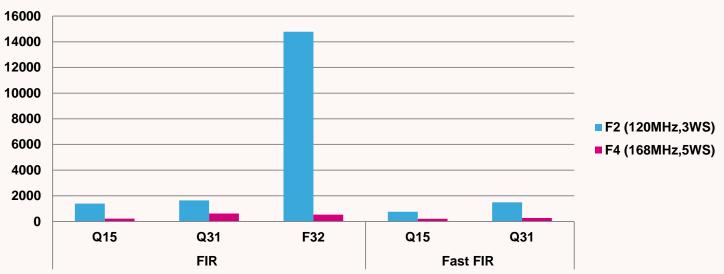

# FIR Benchmarking results F2 vs F4

### FIR average processing time (µs)

|          |       | F2(120MHz,3WS)    | Processing time per Tap | F4(168MHz,5WS)     | Processing time per Tap |

|----------|-------|-------------------|-------------------------|--------------------|-------------------------|

|          | Q15   | 1396.992 μs       | 66ns                    | <b>218.280</b> μs  | 10 ns                   |

| FIR      | Q31   | 1636.658 μs       | <b>77ns</b>             | 618.273 μs         | <b>29 ns</b>            |

|          | Float | 14782.510 μs      | 696ns                   | 531.160 μs         | 25 ns                   |

| Eact EID | Q15   | <b>760.675</b> μs | 36ns                    | <b>209.761 μ</b> s | <b>10 ns</b>            |

| Fast FIR | Q31   | 1488.292 μs       | <b>70ns</b>             | <b>267.464 μ</b> s | <b>13</b> ns            |

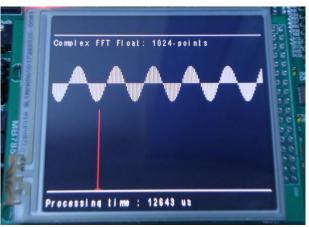

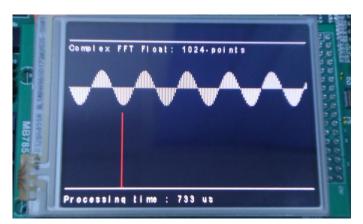

# Complex FFT-1024 points demos 35

Cortex-M3 running Cortex-M3 code

12927µs

Cortex-M4F running Cortex-M3 code 12643µs

### Cortex-M4F running Cortex-M4F code

733µs

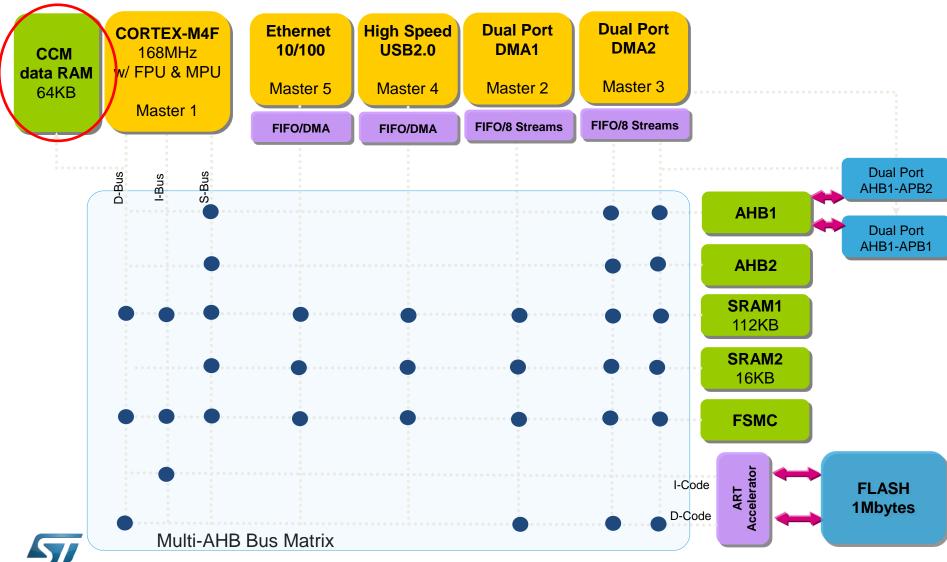

### STM32F4xx Memories & Bus Matrix Bus Matrix behavior, CCM and SRAM remap

This presentation aims to focus on STM32F4 system architecture, performance of some SRAM remapping configuration and Core Coupled Memory Advantages (CCM on CPU D-Bus).

## STM32F4xx system architecture 38

life.augmented

# CCM main advantages (1/2) 39

- Extends memory capacity with 64KB additional SRAM (Base address: 0x10000000). The CCM address space is not contiguous with main SRAM (SRAM1 & SRAM2).

- Allows to secure application:

- Kernel (privileged application) Heap and Stack on CCM

- Application will use SRAM1 & SRAM2

- → Avoid unauthorized accesses :

- No DMA access is possible,

- MPU can protect the full CCM memory range from unauthorized accesses.

# CCM main advantages (2/2) 40

- Ensures a good and efficient operation when several peripherals (high-speed peripherals) are working simultaneously :

- USB HS,

- Ethernet,

- Camera interface,

- FSMC

- Enhance CPU performances by avoiding (concurrency) to access the RAM

- In case of many masters requesting access to the SRAM1/2, Bus Matrix apply Round Robin policy to grant accesses.

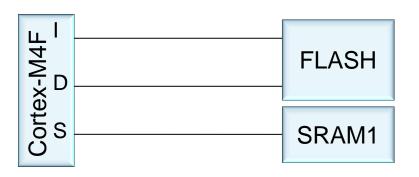

## Performance test example description 41

- For an example of application using only the memory with no usage of peripherals. Only the CPU is active (no DMAs transfer)

- We can test different system configuration : execution from FLASH, SRAM, remapped SRAM,...

- The test program is counting the number of iterations executed by CPU in a fixed period of time.

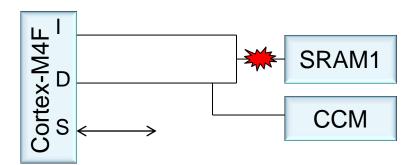

Performance test configuration (1/3) 42

#### Config 1

• In default configuration all accesses are 0-ws, each bus is connected to its default slave.

#### Config 2

- Access are penalized by:

- · Bus Matrix arbitration when switching between CCM and Flash for data accesses

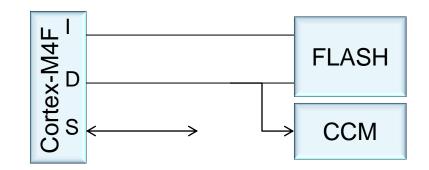

Performance test configuration (2/3)

Config 3

- Access are penalized by :

- Convergence of the 2 buses (I-&D- bus) on the same memory,

#### Config 4

No wait states inserted as bus are dedicated (no arbitration)

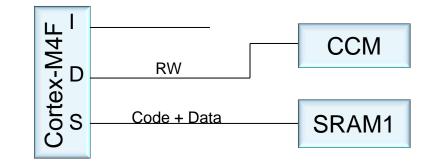

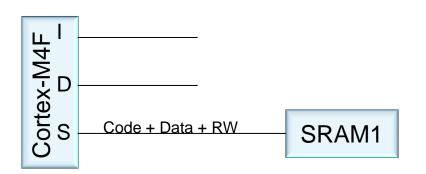

# Performance test configuration (3/3) 44

#### Config 5

- No wait states inserted, full SRAM bandwidth is dedicated to program execution

- Access is penalized if :

- CPU is managing peripherals,

- DMA transfers to SRAM.

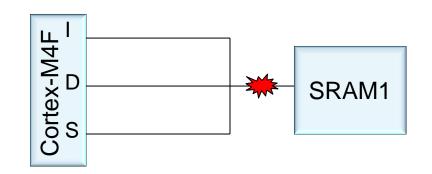

#### Config 6

- Access are penalized by :

- Convergence of the 3 buses on the same memory,

- Bus Matrix Arbitration

## Example execution results 45

- The best performance are achieved when :

- No arbitration is inserted,

- One memory dedicated for each bus.

| Configuration | Description                                     | Iterations |

|---------------|-------------------------------------------------|------------|

| Config 1      | Code : Flash<br>RAM: SRAM1                      | 106251     |

| Config 2      | Code : Flash<br>RAM: CCM                        | 89969      |

| Config 3      | Code : SRAM1 (remapped)<br>RAM: CCM             | 83624      |

| Config 4      | Code: SRAM1 (no remap)<br>RAM: CCM              | 83531      |

| Config 5      | Code: SRAM1 (no remap)<br>RAM: SRAM1            | 83531      |

| Config 6      | Code: SRAM1 (remapped)<br>RAM: SRAM1 (on S-Bus) | 68890      |

## Contents 46

- Documents Major Updates

- STM32 (Errata, Datasheets, Reference Manual, Application notes)

- STM32 technical presentations

- DSP and FPU Application Notes & Demo presentation

- STM32F4xx Memories and Bus Matrix

- Support Status and Major Requests/Hits

- AMR (Absolute Maximum Ratings) and current injection

- ADC : how to choose the right sampling time ?

- PC Software (Flash Loader & DFuSe) update

- Conclusion With the Hits/Tips of the last period

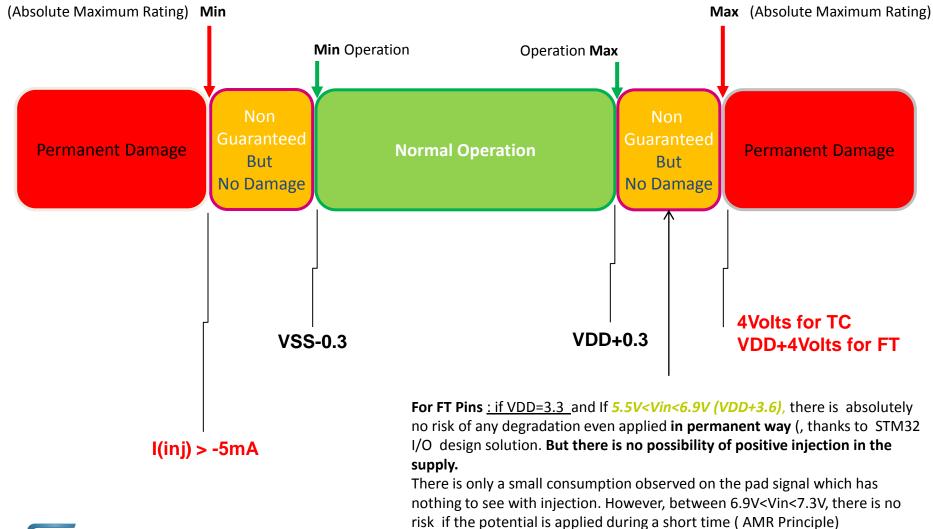

# AMR (Absolute Maximum Ratings)

### STM32 Datasheets Major update AMR "Absolute Maximum Rating"

Stresses above those listed as "absolute maximum ratings" may cause permanent damage to the device.

This is a stress rating only and **functional operation of the device under these conditions is not implied**. Exposure to maximum rating conditions for extended periods may affect **device reliability**.

AMR section updated to clearly separate voltage and current maximum ratings

### STM32 Datasheets Major update AMR "Absolute Maximum Rating"

| Symbol                                                                                          | Ratings                                                 | MIn                                                                         | Мах                   | Unit  |

|-------------------------------------------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------|-----------------------|-------|

| $V_{DD}-V_{SS}$ External main supply voltage (including $V_{DDA}$ and $V_{DD}$ ) <sup>(1)</sup> |                                                         | -0.3                                                                        | 4.0                   |       |

| V <sub>IN</sub> (2)                                                                             | Input voltage on five volt tolerant pin                 | V <sub>SS</sub> – 0.3                                                       | V <sub>DD</sub> + 4.0 | V     |

| VIN                                                                                             | Input voltage on any other pin                          | V <sub>SS</sub> – 0.3                                                       | 4.0                   |       |

| I∆V <sub>DDx</sub> I                                                                            | Variations between different V <sub>DD</sub> power pins |                                                                             | 50                    | mV    |

| $ V_{SSX} - V_{SS} $                                                                            | Variations between all the different ground pins        |                                                                             | 50                    | ····v |

| V <sub>ESD(HBM)</sub>                                                                           | Electrostatic discharge voltage (human body model)      | see Section 5.3.12:<br>Absolute maximum ratings<br>(electrical sensitivity) |                       |       |

#### Table 7. Voltage characteristics

1. All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

2. VIN maximum must always be respected. Refer to Table 8. for maximum allowed injected current values.

#### Only Max Must be always respected NOT Minimum

*That means we can have "Vin" lower than VSS-0.3Volts while not exceeding -5mA. !* This feature is interesting for mains powered applications to detect Zero Crossing

### STM32 Datasheets Major update AMR "Absolute Maximum Rating" - Voltage

The true voltage AMR is now given in the AMR voltage characteristics table. This voltage is the Absolute Voltage. However, user must also care about current injection and to refer to Current Injection Table.

50

### STM32 Datasheets Major update AMR "Absolute Maximum Rating" - Current

- The injection information is no table.

- The injection AND the maximu

- When possible, positive injecti

Note 3, 4 and 5 were updated.

| Symbol                                                                                         | Ratings                                                                                  | Max.  | Unit |

|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------|------|

| IVDD                                                                                           | Total current into V <sub>DD</sub> /V <sub>DDA</sub> power lines (source) <sup>(1)</sup> | 150   |      |

| IVSS                                                                                           | Total current out of V <sub>SS</sub> ground lines (sink) <sup>(1)</sup>                  |       | 1    |

|                                                                                                | Output current sunk by any I/O and control pin                                           | 25    | 1    |

| IIO                                                                                            | Output current source by any I/Os and control pin                                        | - 25  | mA   |

| . (2)                                                                                          | Injected current on five volt tolerant pins <sup>(3)</sup>                               | -5/+0 | 1    |

| I <sub>INJ(PIN)</sub> <sup>(2)</sup>                                                           | Injected current on any other pin <sup>(4)</sup>                                         | ± 5   | 1    |

| ΣI <sub>INJ(PIN)</sub> Total injected current (sum of all I/O and control pins) <sup>(5)</sup> |                                                                                          | ± 25  | 1    |

51

All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

Negative injection disturbs the analog performance of the device. See note in Section 5.3.19: 12-bit ADC characteristics.

3. Positive injection is not possible on these I/Os. A negative injection is induced by VIN<VSS. IINJ(PIN) must never be exceeded. Refer to *Table 7*. for maximum allowed input voltage values.

- A positive injection is induced by VIN>VDD while a negative injection is induced by VIN<VSS. IINJ(PIN) must never be exceeded. Refer to *Table 7.* for maximum allowed input voltage values.

- 5. When several inputs are submitted to a current injection, the maximum ΣIINJ(PIN) is the absolute sum of the positive and negative injected currents (instantaneous values).

- The AMR Vin must not be unders

- The allowed Vin operating condit characteristics table, with VIH p

| Table 46. I/O static characteristics |                                                                     |                                                                      |                                   |     |                                    |      |

|--------------------------------------|---------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------------------|-----|------------------------------------|------|

| Symbol                               | Parameter                                                           | Conditions                                                           | Min                               | Тур | Max                                | Unit |

| v                                    | Standard IO input low<br>level voltage                              |                                                                      | -0.3                              |     | 0.28*(V <sub>DD</sub> -2 V)+0.8 V  | ۷    |

| VIL                                  | IO FT <sup>(1)</sup> input low level<br>voltage                     |                                                                      | -0.3                              |     | 0.32*(V <sub>DD</sub> -2 V)+0.75 V | ۷    |

|                                      | Standard IO input high<br>level voltage                             |                                                                      | 0.41*(V <sub>DD</sub> -2 V)+1.3 V |     | V <sub>DD</sub> +0.3               | ۷    |

| VIH                                  | IO FT <sup>(1)</sup> input high level                               | V <sub>DD</sub> > 2 V                                                | 0.42*(V <sub>DD</sub> -2 V)+1 V   |     | 5.5                                | v    |

|                                      | voltage                                                             | V <sub>DD</sub> ≤2V                                                  | 0.42 (VDD-2 V)+1 V                |     | 5.2                                |      |

| V <sub>hys</sub>                     | Standard IO Schmitt<br>trigger voltage<br>hysteresis <sup>(2)</sup> |                                                                      | 200                               |     |                                    | mV   |

|                                      | IO FT Schmitt trigger<br>voltage hysteresis <sup>(2)</sup>          |                                                                      | 5% V <sub>DD</sub> <sup>(3)</sup> |     |                                    | mV   |

| l <sub>ikg</sub>                     | Input leakage current (4)                                           | V <sub>SS</sub> ≤ V <sub>IN</sub> ≤ V <sub>DD</sub><br>Standard I/Os |                                   |     | ±1                                 | μA   |

|                                      |                                                                     | V <sub>IN</sub> = 5 V, I/O FT                                        |                                   |     | 3                                  |      |

| R <sub>PU</sub>                      | Weak pull-up equivalent<br>resistor <sup>(5)</sup>                  | V <sub>IN</sub> -V <sub>SS</sub>                                     | 30                                | 40  | 50                                 | kΩ   |

| R <sub>PD</sub>                      | Weak pull-down<br>equivalent resistor <sup>(5)</sup>                | V <sub>IN</sub> - V <sub>DD</sub>                                    | 30                                | 40  | 50                                 | kΩ   |

| CIO                                  | I/O pin capacitance                                                 |                                                                      |                                   | 5   |                                    | pF   |

1. FT = Five-volt tolerant. In order to sustain a voltage higher than VDD+0.3 the internal pull-up/pull-down resistors must be disabled.

52

### STM32 Datasheets Major update New section added

#### 5.3.13 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard, 3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibilty to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (>5 LSB TUE), out of spec current injection on adjacent pins or other functional failure (for example reset, oscillator frequency deviation).

The test results are given in Table 45

|        |                                                            | Functional s          |                       |      |

|--------|------------------------------------------------------------|-----------------------|-----------------------|------|

| Symbol | Description                                                | Negative<br>injection | Positive<br>Injection | Unit |

|        | Injected current on OSC_IN32,<br>OSC_OUT32, PA4, PA5, PC13 | -0                    | +0                    |      |

| INJ    | Injected current on all FT pins                            | -5                    | +0                    | mA   |

|        | Injected current on any other pin                          | -5                    | +5                    |      |

#### Table 45. I/O current injection susceptibility

## Competition positioning AMR "Absolute Maximum Rating" Voltage

|           | Item description                                                                                                                                                                                                                  | Value                                                                                                                |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| STM32     | Input voltage on five volt tolerant pin<br>Input voltage on any other pin                                                                                                                                                         | V <sub>SS</sub> -0.3 to V <sub>DD</sub> +4V<br>V <sub>SS</sub> -0.3 to 4V                                            |

| CompetR6  | Input voltage (except for ports for 5V tolerant)<br>Input voltage (ports for 5V tolerant)                                                                                                                                         | -0.3 to VCC+0.3V<br>-0.3 to 5.8                                                                                      |

| CompetR2  | Input voltage (except for ports for 5V tolerant)<br>Input voltage (ports for 5V tolerant)                                                                                                                                         | -0.3 to VCC+0.3V<br>-0.3 to 6.5V                                                                                     |

| CompetN18 | <ul> <li>Input voltage (only valid when the VDD(IO) supply voltage is present)</li> <li>5V tolerant I/O pins</li> <li>ADC/DAC pins and digital I/O pins configured for an analog function</li> <li>USB pins</li> </ul>            | -0.5 to 5.5V<br>TBD to V <sub>DDA(3V3)</sub><br>TBD to TBD                                                           |

| CompetA32 | Voltage on Input Pin<br>with respect to Ground except<br>with respect to Ground for                                                                                                                                               | -0.3 to 5.5V<br>-0.3 to 3.6V                                                                                         |

| CompetF56 | Digital input voltage<br>Analog input voltage (XTAL)<br>Analog input voltage (ANA0-7,VREF)                                                                                                                                        | $V_{SSIO}$ -0.3 to $V_{SSIO}$ +5.5V<br>$V_{SSA}$ -0.3 to $V_{DDA}$ +0.3V<br>$V_{SSA ADC}$ -0.3 to $V_{SS ADC}$ +5.5V |

| CompetFK  | Digital input voltage (except RESET, XTAL)<br>Tamper input voltage<br>Analog, RESET, XTAL input voltage                                                                                                                           | -0.3 to 5.5V<br>-0.3 to V <sub>BAT</sub> +0.3V<br>-0.3 to V <sub>DD</sub> +0.3V                                      |

| CompetM32 | Voltage on any pin that is not 5V tolerant with respect to $V_{SS}$<br>Voltage on any 5V tolerant pin with respect to $V_{SS}$ when $V_{DD} \ge 3V$<br>Voltage on any 5V tolerant pin with respect to $V_{SS}$ when $V_{DD} < 3V$ | -0.3 to V <sub>DD</sub> +0.3V<br>-0.3 to 5.6V<br>-0.3 to 3.6V                                                        |

#### Often specific competitor notes makes this positioning better for STM32

### Synthesis 55

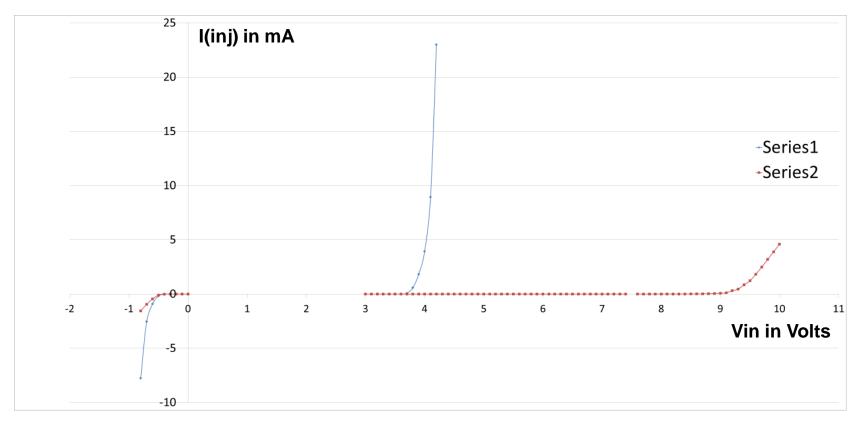

# Typical I/O behavior of two I/Os 56

STM32F1xx device : Vin is applied directly on the pad without serial limiting resistance

- Series1 (blue) = TC I/O

- Series2 (red) = FT I/O

# PA9, PB13 USB V<sub>BUS</sub> Sensing feature 57

- Customer case application: USB device peripheral application

- **I/O configuration:** V<sub>BUS</sub> PA9 should be left at default state (floating input), not as alternate function !

- **Observed behavior:** A current of about 200µA is seen on the pad

#### • Explanation:

- The current observed on  $V_{BUS}$  pad is normal and expected with the present design.

- This is indeed due to the V<sub>BUS</sub> sensing block where a current to voltage conversion is implemented to determine the different sessions.

- $\rightarrow$  This behavior is will be documented in future in our datasheets

## ADC How to choose the right sampling time ?

# Typical application case 59

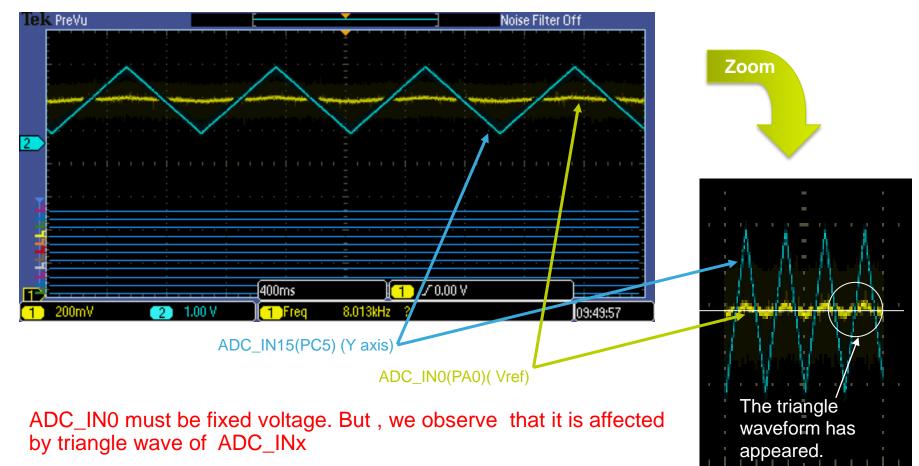

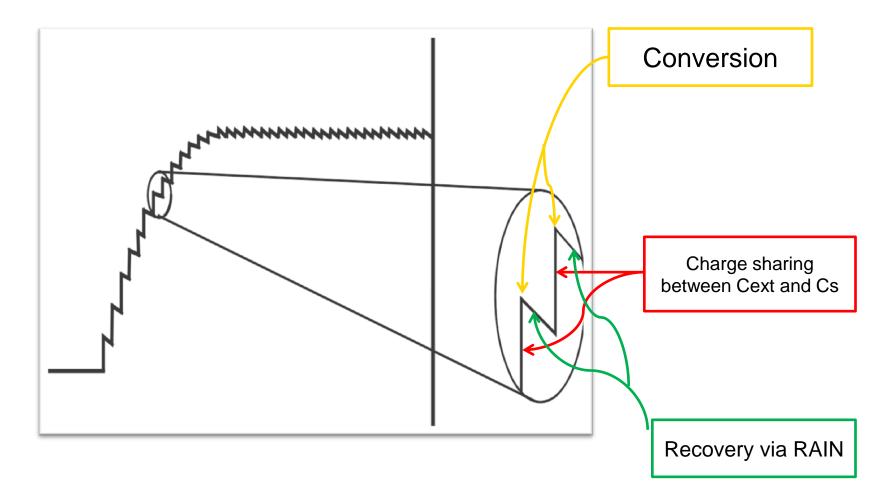

# Strange crosstalk behavior 60

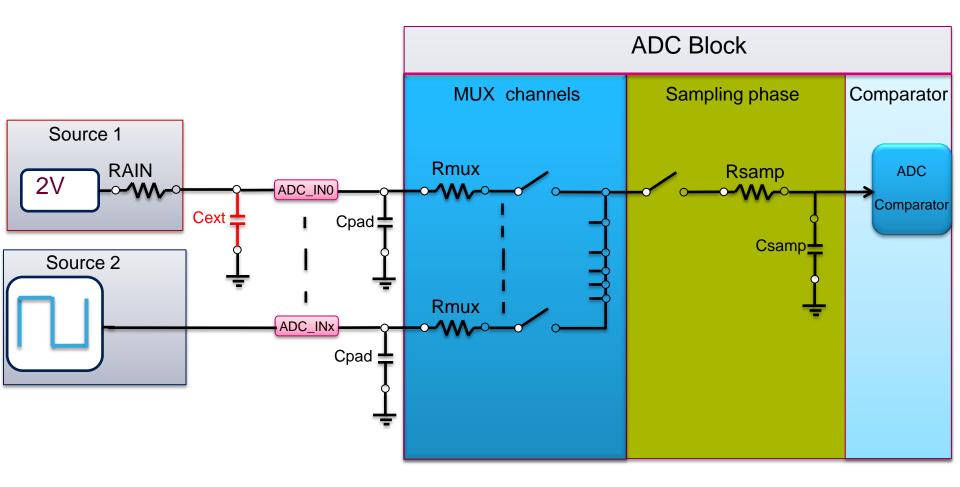

Both ADC\_IN0 and ADC\_INx are scanned by ADC in continuous mode  $R_{\text{AIN}}$  is 33 KOhm .

# Explanation (1/5)

- In STM32F1xx devices, we have a SAR ADC peripheral able to sustain up to 1Msps

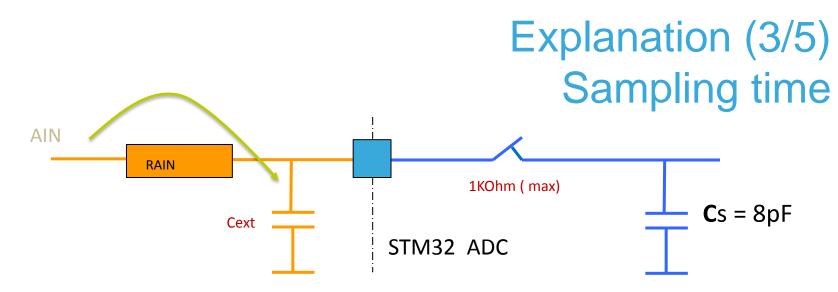

- The side effect of any SAR ADC is that the sample capacitor within the ADC is directly charged by the external signal (\*), that means if the sample time is insufficient, then the charge left on the sample capacitor by the previous conversion of a channel can affect the accuracy of the channel currently being converted.

- This phenomenon is referred to as channel-to-channel crosstalk and is exactly what has been observed by our experiments.

(\*) There is not discharge of sample and hold capacitor at the end of the conversion

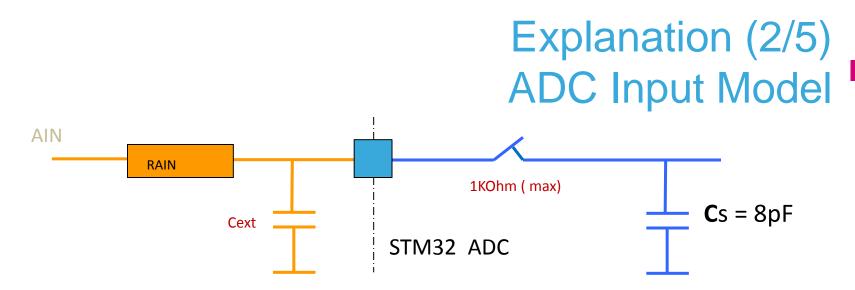

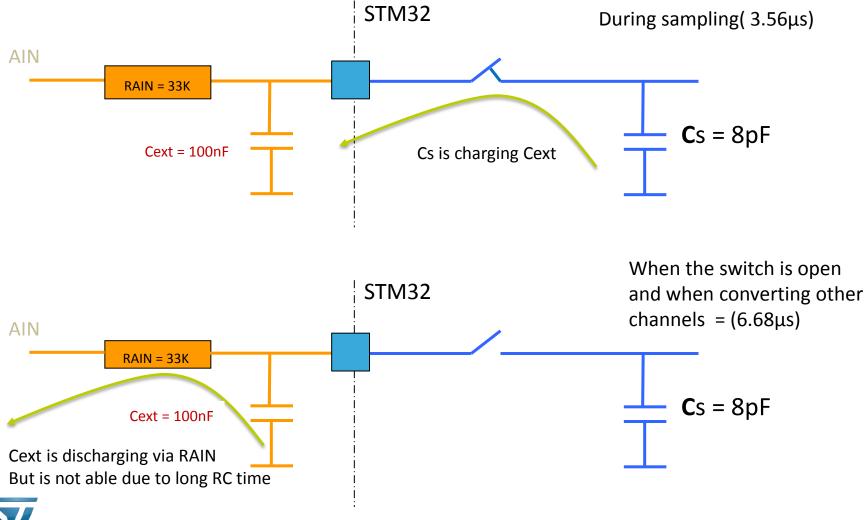

- The Block at right side is the Internal ADC input model and the block at left side is optional and done by the customer/user externally,

- Generally, some users place a large capacitor "Cext" [100nF in this case] from the ADC pin to ground, This capacitor is used to lower the source impedance of the channel as seen by the ADC so that the internal sample capacitor can be charged quickly.

- But this will create a charge-sharing process between Cext and Cs, whose RC time constant is primarily determined by the maximum ADC input resistance (1KOhm) and maximum sample capacitance (8pF) of the ADC.

- As RAIN is increased, the cutoff frequency created by RAIN and Cext will be lowered.

62

- The Time constant required for an RC circuit to settle to within 1/4 LSB with 12 bits resolution is :  $\partial = \ln (2 \text{ pow } (12+2)) = 9.7$  time constant ~ 10 time constant

- That means in our case, Cext=100nF and RAIN=33KOhm, that channel should sampled/converted not less than each : 10 x 100nF \* 33KOhm = **"33ms"**.

- Cext is repeated discharged/charged to Cs via the switch (1KOhm) during sampling time 28.5cycles at 8MHz = 3.56µs without having enough time to be recharged/discharged via RAIN for a whole 33ms.

## Explanation (4/5) Charge sharing

### Explanation (5/5) Charge transfer from previous conversion

ife.augmented

# Sampling time (if C<sub>ext</sub>=0)

- There is not discharge of sample and hold capacitor at the end of the conversion.

- Sampling is optimized if following rules are achieved.

| R <sub>AIN</sub> <sup>(2)</sup> | External input impedance              | See Equation 1 and<br>Table 47 for details |  | 50 | kΩ |

|---------------------------------|---------------------------------------|--------------------------------------------|--|----|----|

| R <sub>ADC</sub> <sup>(2)</sup> | Sampling switch resistance            |                                            |  | 1  | kΩ |

| C <sub>ADC</sub> <sup>(2)</sup> | Internal sample and hold<br>capacitor |                                            |  | 8  | pF |

#### Equation 1: RAIN max formula:

$$R_{AIN} < \frac{T_S}{f_{ADC} \times C_{ADC} \times \ln(2^{N+2})} - R_{ADC}$$

The formula above (*Equation 1*) is used to determine the maximum external impedance allowed for an error below 1/4 of LSB. Here N = 12 (from 12-bit resolution).

Table 47.  $R_{AIN}$  max for  $f_{ADC} = 14 \text{ MHz}^{(1)}$

| T <sub>s</sub> (cycles) | t <sub>S</sub> (μs) | R <sub>AIN</sub> max (kΩ) |

|-------------------------|---------------------|---------------------------|

| 1.5                     | 0.11                | 0.4                       |

| 7.5                     | 0.54                | 5.9                       |

| 13.5                    | 0.96                | 11.4                      |

| 28.5                    | 2.04                | 25.2                      |

| 41.5                    | 2.96                | 37.2                      |

| 55.5                    | 3.96                | 50                        |

| 71.5                    | 5.11                | NA                        |

| 239.5                   | 17.1                | NA                        |

66

# Recommendation & Conclusion 67

We can conclude that this issue is coming from inadequate selection of the right sampling time when converting that channel continuously in scan mode and we need to reduce that constant time by different means/methods:

$$T_{Samp} > In(2^{(12+2)}) * C_{ext} * R_{AIN}$$

$$C_{ext} \ge 2^{(12+2)} * C_{S} = 16384 * C_{S}$$

- 1. Put a very large  $C_{ext} > 132nF$

- 2. Reducing  $R_{AIN}$  to match the selected timing of conversion

- Removing  $C_{ext}$  (100nF) capacitor, so the new constant time will be only 3. [(R<sub>AIN</sub> +1KOhm) \* C<sub>S</sub>] \* 10

- 4. Increasing the sampling/conversion period of the channel in the total scan more (this may be not acceptable in the application)

- 5. Add in the scan sequence as sampling of a channel connected to VSSA/VREFso the C<sub>S</sub> will be discharged quickly after each conversion (this may be not acceptable for in some applications)

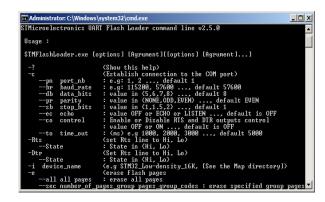

# PC Software update (Flash Loader & DFuSe)

# PC Software Misc updates

#### Flash Loader demonstrator v2.5.0 (On Web)

- Support of new devices

- Command line version manage automatic entry in System-Memory mode from PC & all sources files are provided now including DLLs.

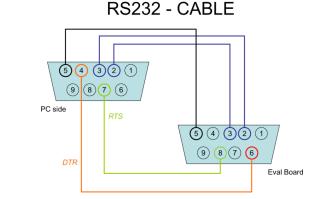

• RTS and DTR signals should **control Boot0 and Reset pins** on the evaluation board (see STM32F2/4 Evaluation board as reference)

#### • DFuSe v3.0.3 (On Web in June 2012)

- Support of new devices

- Add of new Command line version for Automatic update without GUI !

69

## Contents 70

- Documents Major Updates

- STM32 (Errata, Datasheets, Reference Manual, Application notes)

- STM32 technical presentations

- DSP and FPU Application Notes & Demo presentation

- STM32F4xx Memories and Bus Matrix

- Support Status and Major Requests/Hits

- AMR (Absolute Maximum Ratings) and current injection

- ADC : how to choose the right sampling time ?

- PC Software (Flash Loader & DFuSe) update

#### Conclusion - With the Hits/Tips of the last period

## Last Period Most interesting issue

- The customer is seeing on his board using STM32F2 series that sometimes a hard-fault is triggered and suspected that the Flash or ART has a limitation with a special assembly sequence.

- However on ST Evaluation board, he can not replicate the case.

- Root cause: After long investigations and simulations to reproduce the case, we found that Instead of putting 2.2µF caps on V<sub>CAP</sub> pins, we found 2.2nF !!

# END