Hi,

I am working on a custom board with the STM32F746IGT6. in witch is a FTDI Parallel-USB converter is connected to the FMC.

My problem is that when I try to read data to "fast" from the FMC (after a while, and only sometimes) the FMC reads twice for one cycle. And the read function returns the result from the last transfer. This error is only sometimes and I didn't find any relationship with the content of the data.

If I slow the velocity in them I pull data (> 2ms) then I have no more errors.

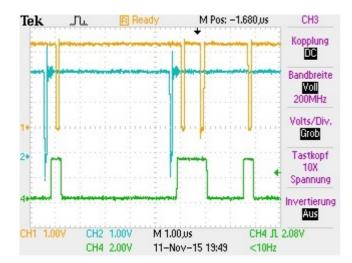

The following image shows the sporadically two reads at the same call.

The yellow line is the read trigger.

The blue line is the write trigger.

And the green line is an output pin that I trigger with software to recognize when the read function is called.

here is the code when I call a read:

```

01. static inline u8 FTDI_RX(void){

return (*(__IO u8*) (NOR_MEMORY_ADRESS3 + FSMC_ADD_FTDI)); // (uint32_t)0x68000000 + 8

02.

03.}

04.

05. char FTDI_READ(void){

96.

char tmp = 0;

07.

if (FTDI_canRead()) {

//READPIN(C, 14)

08.

SETPIN(H, 14);

//Green singal on

09.

tmp = FTDI_RX();

10.

RESETPIN(H, 14);

//Green singal off

11.

FTDI_mode = 1;

12.

return tmp;

13.

} else {

14.

return 0;

15.

16.}

```

The FMC configuration is based on the cube libraries:

```

01. NOR HandleTypeDef hnor1;

02. FMC_NORSRAM_TimingTypeDef Timing;

hnor1.Instance = FMC Bank1;

03.

hnor1.Extended = FMC NORSRAM EXTENDED DEVICE;

04.

//Duration of the address setup phase

05.

//0-15

4

06.

Timing.AddressSetupTime

= 7;

//Duration of the address hold phase

07.

= 7;

//1-15

3

08.

Timing.AddressHoldTime

09.

//Duration of the data setup phase

5

//1-255

10.

Timing.DataSetupTime

= 20;

```

```

11.

//Duration of the bus turnaround phase

= 5;

Timing.BusTurnAroundDuration

//0-15

12.

//Number of AHB clock cycles (HCLK) to build one memory clock cycle (CLK)

13.

Timing.CLKDivision

//2-16

14.

= 3;

15.

//Number of clock cycles to issue to the memory before the first data of the burst

//2-17

16.

Timing.DataLatency

= 3;

17.

Timing.AccessMode

= FMC_ACCESS_MODE_A;

18.

19.

- Data/Address MUX = Disable

20.

- Memory Type = SRAM

- Data Width = 16bit

21.

22.

- Write Operation = Enable

23.

Extended Mode = Enable

24.

- Asynchronous Wait = Disable

*/

25.

26. hnor1.Init.NSBank

= FMC NORSRAM BANK3;

= FMC DATA ADDRESS MUX DISABLE;

27. hnor1.Init.DataAddressMux

= FMC MEMORY TYPE SRAM;

28. hnor1.Init.MemoryType

= FMC NORSRAM MEM BUS WIDTH 16;

29. hnor1.Init.MemoryDataWidth

= FMC BURST ACCESS MODE DISABLE;

30. hnor1.Init.BurstAccessMode

= FMC_ASYNCHRONOUS_WAIT_DISABLE;

31. hnor1.Init.AsynchronousWait

= FMC WAIT SIGNAL POLARITY LOW;

32. hnor1.Init.WaitSignalPolarity

= FMC WAIT TIMING BEFORE WS;

33. hnor1.Init.WaitSignalActive

= FMC WRITE OPERATION ENABLE;

34. hnor1.Init.WriteOperation

35. hnor1.Init.WaitSignal

= FMC_WAIT_SIGNAL_DISABLE;

= FMC EXTENDED_MODE_DISABLE;

36. hnor1.Init.ExtendedMode

37. hnor1.Init.WriteBurst

= FMC_WRITE_BURST_DISABLE;

= FMC_CONTINUOUS_CLOCK_SYNC_ONLY;

38. hnor1.Init.ContinuousClock

39. hnor1.Init.WriteFifo

= FMC_WRITE_FIFO_DISABLE;

//

= FMC_PAGE_SIZE_NONE;

40. hnor1.Init.PageSize

41. // Initialize NOR control Interface

42. FMC_NORSRAM_Init(hnor1.Instance, &(hnor1.Init));

43. // Initialize NOR timing Interface

44. FMC_NORSRAM_Timing_Init(hnor1.Instance, &Timing, hnor1.Init.NSBank);

45. // Initialize NOR extended mode timing Interface

46. //FMC_NORSRAM_Extended_Timing_Init(hnor1.Instance, NULL, hnor1.Init.NSBank,

hnor1.Init.ExtendedMode);

47. // Enable the NORSRAM device

48. (hnor1.Instance)->BTCR[(hnor1.Init.NSBank)] |= FMC_BCR1_MBKEN;

```

I have already turned the D and I cache off, and got same results.

In the errata there is only an error for synchronous memories in burst mode. Witch I am not using.

## STM32F74xxx STM32F75xxx Errata sheet

## "2.5 FMC peripheral limitation

## 2.5.1 Dummy read cycles inserted when reading synchronous memories

## **Description**

When performing a burst read access to a synchronous memory, two dummy read accesses are performed at the end of the burst cycle whatever the type of AHB burst access. However, the extra data values which are read are not used by the FMC and there is no functional failure.

Workaround None. "

Does some one have an Idea what I am doing wrong?

I apologize for my rusty English.

Best regards.

Robert