# **SPIRIT1**

Datasheet - production data

### Low data rate, low power sub-1GHz transceiver

### Features

- Frequency bands: 150-174 MHz, 300-348 MHz, 387-470 MHz, 779-956 MHz

- Modulation schemes: 2-FSK, GFSK, MSK, GMSK, OOK, and ASK

- Air data rate from 1 to 500 kbps

- Very low power consumption (9 mA RX and 21 mA TX at +11 dBm)

- Programmable RX digital filter from 1 kHz to 800 kHz

- Programmable channel spacing (12.5 kHz min.)

- Excellent performance of receiver sensitivity (-118 dBm), selectivity, and blocking

- Programmable output power up to +16 dBm

- Fast startup and frequency synthesizer settling time (6 μs)

- Frequency offset compensation

- Integrated temperature sensor

- · Battery indicator and low battery detector

- RX and TX FIFO buffer (96 bytes each)

- Configurability via SPI interface

- Automatic acknowledgment, retransmission, and timeout protocol engine

- AES 128-bit encryption co-processor

- Antenna diversity algorithm

- Fully integrated ultra low power RC oscillator

- Wake-up on internal timer and wake-up on

- Flexible packet length with dynamic payload length

- Sync word detection

- Address check

- Automatic CRC handling

- FEC with interleaving

- Digital RSSI output

- Programmable carrier sense (CS) indicator

- Automatic clear channel assessment (CCA) before transmitting (for listen-before-talk systems). Embedded CSMA/CA protocol

- Programmable preamble quality indicator (PQI)

- Whitening and de-whitening of data

- Wireless M-BUS, EN 300 220, FCC CFR47 15 (15.205, 15.209, 15.231, 15.247, 15.249), and ARIB STD T-67, T93, T-108 compliant

- QFN20 4x4 mm RoHS package

- Operating temperature range from -40 °C to 105 °C

### **Applications**

- AMR (automatic meter reading)

- Home and building automation

- WSN (wireless sensors network)

- Industrial monitoring and control

- Wireless fire and security alarm systems

- Point-to-point wireless link

#### Table 1. Device summary

| Order code | Package | Packing       |

|------------|---------|---------------|

| SPIRIT1QTR | QFN20   | Tape and reel |

October 2016

DocID022758 Rev 10

1/104

## Contents

| 1 | Descr  | ription                                           |

|---|--------|---------------------------------------------------|

| 2 | Introd | duction                                           |

| 3 |        | al application diagram and pin description        |

|   | 3.1    | Typical application diagram11                     |

| 4 | Pinou  | ıt                                                |

| 5 | Abso   | lute maximum ratings and thermal data             |

| 6 | Chara  | acteristics                                       |

|   | 6.1    | General characteristics                           |

|   | 6.2    | Electrical specifications                         |

|   |        | 6.2.1 Electrical characteristics                  |

|   |        | 6.2.2 Digital SPI                                 |

|   |        | 6.2.3 RF receiver                                 |

|   |        | 6.2.4 RF transmitter                              |

|   |        | 6.2.5 Crystal oscillator                          |

|   |        | 6.2.6 Sensors                                     |

| 7 | Opera  | ating modes                                       |

|   | 7.1    | Reset sequence                                    |

|   | 7.2    | Timer usage                                       |

|   | 7.3    | Low duty cycle reload mode                        |

|   |        | 7.3.1 LDC mode with automatically acknowledgement |

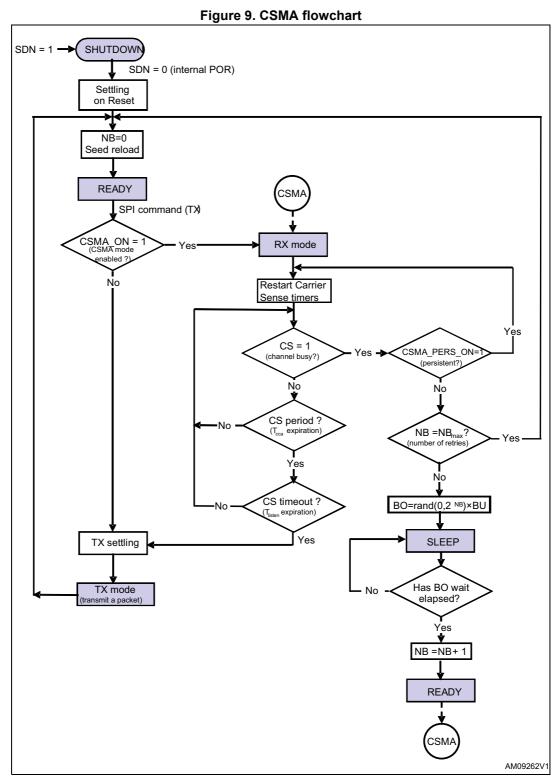

|   | 7.4    | CSMA/CA engine                                    |

| 8 | Block  | description                                       |

|   | 8.1    | Power management 42                               |

|   |        | 8.1.1 Switching frequency                         |

|   | 8.2    | Power-on-reset (POR) 42                           |

|   | 8.3    | Low battery indicator                             |

|   | 8.4    | Voltage reference                                 |

DocID022758 Rev 10

9

| 8.5   | Oscilla | tor and RF synthesizer 43                  |

|-------|---------|--------------------------------------------|

| 8.6   | RCO: f  | eatures and calibration                    |

|       | 8.6.1   | RC oscillator calibration                  |

| 8.7   | AGC .   |                                            |

| 8.8   | AFC .   |                                            |

| 8.9   | Symbo   | I timing recovery                          |

|       | 8.9.1   | DLL mode                                   |

|       | 8.9.2   | PLL mode                                   |

| 8.10  | Receiv  | er                                         |

| 8.11  | Transm  | nitter                                     |

| 8.12  | Tempe   | rature sensors (TS)                        |

| 8.13  | AES er  | ncryption co-processor                     |

|       |         |                                            |

| Trans | smissio | n and reception                            |

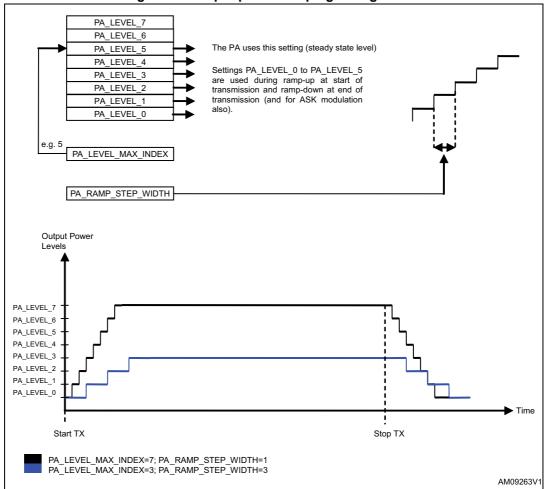

| 9.1   | PA con  | figuration                                 |

| 9.2   | RF cha  | nnel frequency settings 54                 |

| 9.3   | RX tim  | eout management                            |

| 9.4   | Interme | ediate frequency setting                   |

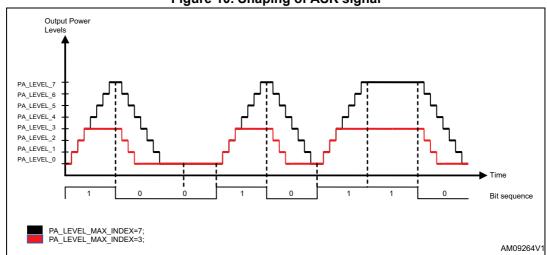

| 9.5   | Modula  | tion scheme                                |

|       | 9.5.1   | Data rate                                  |

|       | 9.5.2   | RX channel bandwidth60                     |

| 9.6   | Data co | oding and integrity check process61        |

|       | 9.6.1   | FEC                                        |

|       | 9.6.2   | CRC                                        |

|       | 9.6.3   | Data whitening                             |

|       | 9.6.4   | Data padding62                             |

| 9.7   | Packet  | handler engine                             |

|       | 9.7.1   | STack packet                               |

|       | 9.7.2   | Wireless M-Bus packet (W M-BUS, EN13757-4) |

|       | 9.7.3   | Basic packet                               |

|       | 9.7.4   | Automatic packet filtering                 |

|       | 9.7.5   | Link layer protocol                        |

| 9.8   | Data m  | odes                                       |

| 9.9   | Data F  | IFO                                        |

| 9.10  | Receiv  | er quality indicators                      |

|       |         |                                            |

|    |       | 9.10.1    | RSSI                 | 71   |

|----|-------|-----------|----------------------|------|

|    |       | 9.10.2    | Carrier sense        | 72   |

|    |       | 9.10.3    | PQI                  | 72   |

|    |       | 9.10.4    | SQI                  | 73   |

|    | 9.11  | Antenna   | a diversity          | . 73 |

|    | 9.12  | Freque    | ncy hopping          | . 74 |

| 10 | MCU   | interfac  | e                    | . 75 |

|    | 10.1  | Serial p  | peripheral interface | . 75 |

|    | 10.2  | Interrup  | ots                  | . 77 |

|    | 10.3  | GPIOs     |                      | . 78 |

|    | 10.4  | MCU cl    | lock                 | . 80 |

| 11 | Regi  | ster tabl | le                   | . 82 |

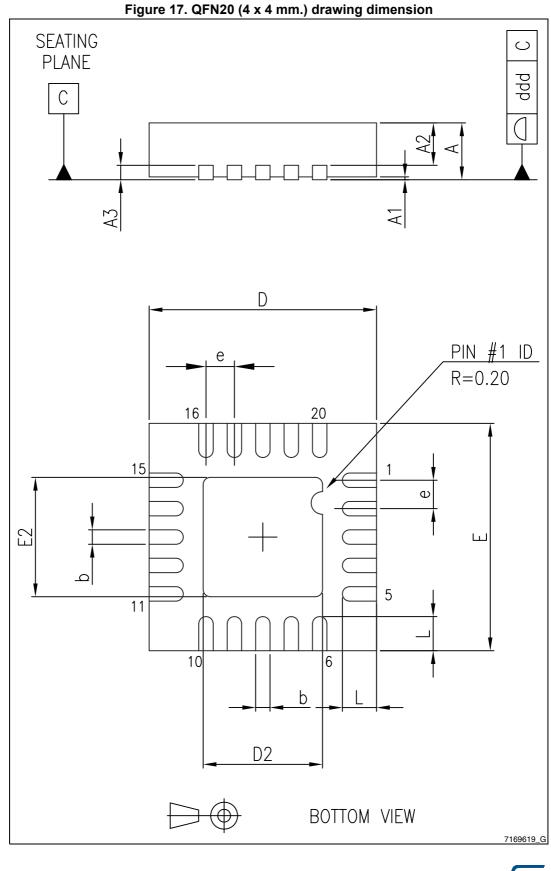

| 12 | Pack  | age me    | chanical data        | 101  |

| 13 | Revis | sion his  | tory                 | 103  |

## List of tables

| Table 1.  | Device summary                                                                        |      |

|-----------|---------------------------------------------------------------------------------------|------|

| Table 2.  | Description of the external components of the typical application diagram             | . 13 |

| Table 3.  | BOM for different bands                                                               | . 14 |

| Table 4.  | Pinout description                                                                    | . 15 |

| Table 5.  | Absolute maximum ratings                                                              | . 16 |

| Table 6.  | Thermal data                                                                          |      |

| Table 7.  | Recommended operating conditions                                                      |      |

| Table 8.  | General characteristics                                                               |      |

| Table 9.  | Power consumption static modes                                                        |      |

| Table 10. | Power consumption                                                                     |      |

| Table 11. | Digital SPI input and output (SDO, SDI, SCLK, CSn, and SDN) and GPIO specification (G |      |

|           | O_1-4).                                                                               |      |

| Table 12. | RF receiver characteristics                                                           |      |

| Table 13. | RF receiver characteristics - sensitivity.                                            |      |

| Table 14. | RF transmitter characteristics                                                        |      |

| Table 15. | Crystal oscillator characteristics                                                    |      |

| Table 15. | Ultra low power RC oscillator                                                         |      |

| Table 10. | N-Fractional $\Sigma\Delta$ frequency synthesizer characteristics.                    |      |

|           |                                                                                       |      |

| Table 18. | Analog temperature sensor characteristics                                             |      |

| Table 19. | Battery indicator and low battery detector                                            |      |

| Table 20. | States                                                                                |      |

| Table 21. | Commands list                                                                         |      |

| Table 22. | POR parameters.                                                                       |      |

| Table 23. | SPIRIT1 timers description and duration                                               |      |

| Table 24. | SMPS configuration settings.                                                          |      |

| Table 25. | Programmability of trans-conductance at startup                                       |      |

| Table 26. | CP word look-up                                                                       |      |

| Table 27. | RC calibrated speed                                                                   |      |

| Table 28. | PA_level                                                                              |      |

| Table 29. | Frequency threshold                                                                   |      |

| Table 30. | RX timeout stop condition configuration                                               |      |

| Table 31. | IF_OFFSET settings                                                                    | . 57 |

| Table 32. | CHFLT_M and CHFLT_E value for channel filter bandwidth (in kHz, for fclk = 24 MHz).   | . 60 |

| Table 33. | CHFLT_M and CHFLT_E value for channel filter bandwidth (in kHz, for fclk = 26 MHz).   |      |

| Table 34. | Packet configuration                                                                  | . 67 |

| Table 35. | SPI interface timing requirements                                                     | . 77 |

| Table 36. | Interrupts                                                                            | . 77 |

| Table 37. | Digital outputs                                                                       | . 78 |

| Table 38. | Digital inputs                                                                        |      |

| Table 39. | MCU_CK_CONF configuration register                                                    | . 80 |

| Table 40. | MCU clock vs. state                                                                   |      |

| Table 41. | General configuration registers.                                                      |      |

| Table 42. | Radio configuration registers (analog blocks).                                        | . 85 |

| Table 43. | Radio configuration registers (digital blocks)                                        |      |

| Table 44. | Packet/protocol configuration registers.                                              | . 89 |

| Table 45. | Frequently used registers                                                             |      |

| Table 46. | General information                                                                   |      |

| Table 47. | QFN20 (4 x 4 mm.) mechanical data                                                     |      |

|           |                                                                                       |      |

| Table 48. | Document revision history | <br>103 |

|-----------|---------------------------|---------|

|           | -                         |         |

# List of figures

| Figure 1.  | SPIRIT1 block diagram                 | . 9 |

|------------|---------------------------------------|-----|

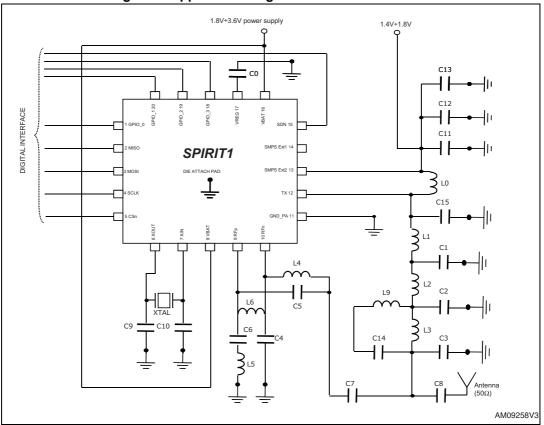

| Figure 2.  | Suggested application diagram         | 11  |

| Figure 3.  | Application diagram for Tx boost mode |     |

| Figure 4.  | Application diagram for SMPS OFF mode | 13  |

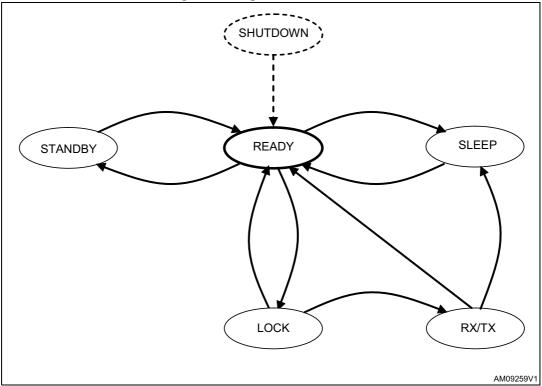

| Figure 5.  | Diagram and transition                | 32  |

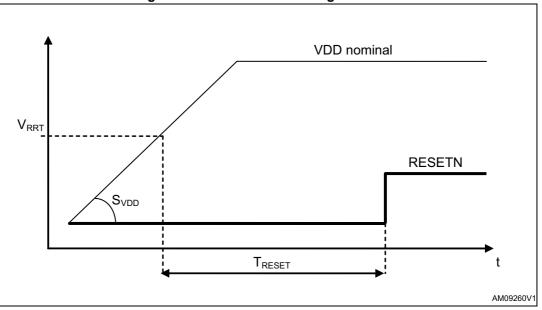

| Figure 6.  | Power-on reset timing and limits      | 35  |

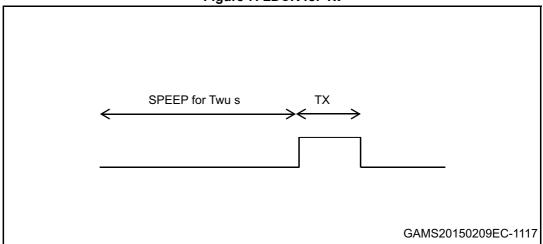

| Figure 7.  | LDCR for Tx                           | 37  |

| Figure 8.  | LDCR for Rx                           | 37  |

| Figure 9.  | CSMA flowchart                        |     |

| Figure 10. | Shaping of ASK signal                 | 50  |

| Figure 11. | Output power ramping configuration    | 53  |

| Figure 12. | LFSR block diagram                    | 62  |

| Figure 13. | Threshold of the linear FIFO          | 70  |

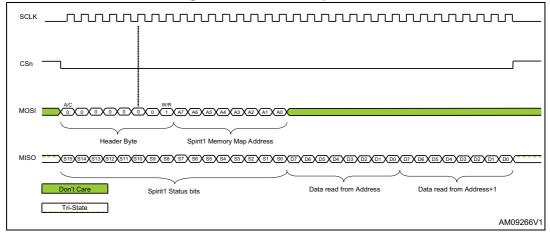

| Figure 14. | SPI "write" operation                 | 76  |

| Figure 15. | SPI "read" operation                  | 76  |

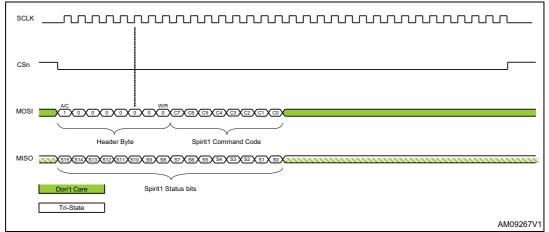

| Figure 16. | SPI "command" operation               |     |

| Figure 17. | QFN20 (4 x 4 mm.) drawing dimension 1 | 02  |

|            |                                       |     |

### 1 Description

The SPIRIT1 is a very low-power RF transceiver, intended for RF wireless applications in the sub-1 GHz band. It is designed to operate both in the license-free ISM and SRD frequency bands at 169, 315, 433, 868, and 915 MHz, but can also be programmed to operate at other additional frequencies in the 300-348 MHz, 387-470 MHz, and 779-956 MHz bands. The air data rate is programmable from 1 to 500 kbps, and the SPIRIT1 can be used in systems with channel spacing of 12.5/25 kHz, complying with the EN 300 220 standard. It uses a very small number of discrete external components and integrates a configurable baseband modem, which supports data management, modulation, and demodulation. The data management handles the data in the proprietary fully programmable packet format also allows the M-Bus standard compliance format (all performance classes).

However, the SPIRIT1 can perform cyclic redundancy checks on the data as well as FEC encoding/decoding on the packets. The SPIRIT1 provides an optional automatic acknowledgement, retransmission, and timeout protocol engine in order to reduce overall system costs by handling all the high-speed link layer operations.

Moreover, the SPIRIT1 supports an embedded CSMA/CA engine. An AES 128-bit encryption co-processor is available for secure data transfer. The SPIRIT1 fully supports antenna diversity with an integrated antenna switching control algorithm. The SPIRIT1 supports different modulation schemes: 2-FSK, GFSK, OOK, ASK, and MSK. Transmitted/received data bytes are buffered in two different three-level FIFOs (TX FIFO and RX FIFO), accessible via the SPI interface for host processing.

### 2 Introduction

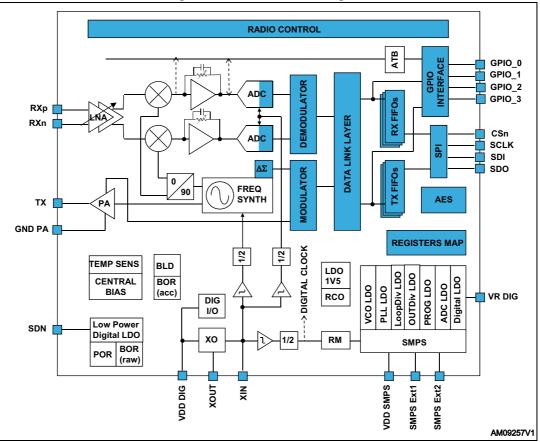

A simplified block diagram of the SPIRIT1 is shown in Figure 1.

Figure 1. SPIRIT1 block diagram

The receiver architecture is low-IF conversion. The received RF signal is amplified by a twostage low-noise amplifier (LNA) and down-converted in quadrature (I and Q) to the intermediate frequency (IF). LNA and IF amplifiers make up the RX front-end (RXFE) and have programmable gain. At IF, I/Q signals are digitized by ADCs. The demodulated data is then provided to an external MCU either through the 96-byte RX FIFO, readable via SPI, or directly using a programmable GPIO pin. A 128-bit AES co-processor is available to perform (offline) data encryption/decryption to secure data transfer.

The transmitter part of the SPIRIT1 is based on direct synthesis of the RF frequency. The power amplifier (PA) input is the LO generated by the RF synthesizer, while the output level can be configured between -30 dBm and +11 dBm in 0.5 dB steps. The data to be transmitted can be provided by an external MCU either through the 96-byte TX FIFO writable via SPI, or directly using a programmable GPIO pin. The SPIRIT1 supports frequency hopping, TX/RX and antenna diversity switch control, extending the link range and improving performance.

The SPIRIT1 has a very efficient power management (PM) system.

An integrated switched mode power supply (SMPS) regulator allows operation from a battery voltage ranging from +1.8 V to +3.6 V, and with power conversion efficiency of at least 80%.

A crystal must be connected between XIN and XOUT. It is digitally configurable to operate with different crystals. As an alternative, an external clock signal can be used to feed XIN for proper operation. The SPIRIT1 also has an integrated low-power RC oscillator, generating the 34.7 kHz signal used as a clock for the slowest timeouts (i.e. sleeping and backoff).

A standard 4-pin SPI bus is used to communicate with the external MCU. Four configurable general purpose I/Os are available.

## 3 Typical application diagram and pin description

### 3.1 Typical application diagram

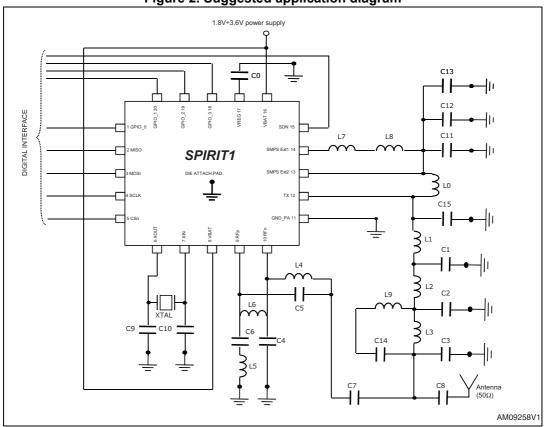

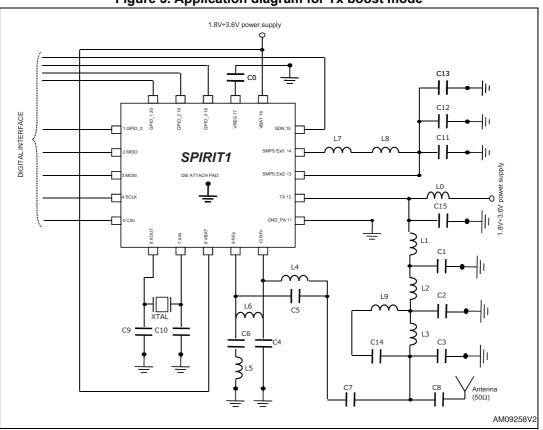

This section describes different application diagram of SPIRIT1 that can be used according to customer needs. In particular *Figure 2* shows the default configuration, *Figure 3* shows the TX boost mode configuration and *Figure 4* shows the SMPS off configuration. The default configuration is giving the best power consumption figures. The TX boost mode configuration is used to increase TX output power and the SMPS off configuration is used to enhance sensitivity at the expense of power consumption. When using SMPS off configuration, SMPS should disabled by setting to1 bit DISABLE\_SMPS in PM\_CONFIG register. It is important the SDN pin to be driven by an external microcontroller. It should be set low when the supply voltage of the device is steady to VDD. A short circuit connection of the SDN pin to ground should be avoided.

Figure 3. Application diagram for Tx boost mode

57

#### Figure 4. Application diagram for SMPS OFF mode

| Table 2. Description of the external | components of the typi | cal application diagram |

|--------------------------------------|------------------------|-------------------------|

|                                      |                        |                         |

| Components           | Description                                                        |

|----------------------|--------------------------------------------------------------------|

| C0                   | Decoupling capacitor for on-chip voltage regulator to digital part |

| C1, C2, C3, C14, C15 | RF LC filter/matching capacitors                                   |

| C4, C5               | RF balun/matching capacitors                                       |

| C6, C7, C8           | RF balun/matching DC blocking capacitors                           |

| C9, C10              | Crystal loading capacitors                                         |

| C11, C12, C13        | SMPS LC filter capacitor                                           |

| LO                   | RF choke inductor                                                  |

| L1, L2, L3, L9       | RF LC filter/matching inductors                                    |

| L4, L5, L6           | RF balun/matching inductors                                        |

| L7, L8               | SMPS LC filter inductor                                            |

| XTAL                 | 24, 26, 48, 52 MHz                                                 |

*Table 2* assumes to cover all the frequency bands using a set of different as shown in *Table 3: BOM for different bands*.

| Table 3. BOM for different bands |                         |                     |                      |           |                      |                 |                      |                   |                     |                    |

|----------------------------------|-------------------------|---------------------|----------------------|-----------|----------------------|-----------------|----------------------|-------------------|---------------------|--------------------|

| Ref                              | 170 MH                  | z band 315 MHz band |                      | z band    | 433 MHz band         |                 | 868 MH               | lz band           | 915/922 MHz band    |                    |

| design<br>(1)                    | gn STEVAL-<br>IKRV001V1 |                     | STEVAL-<br>IKRV001V2 |           | STEVAL-<br>IKRV001V3 |                 | STEVAL-<br>IKRV001V4 |                   | STEVAL-IKRV001V5    |                    |

| Comp.                            | Supplier                | Value               | Supplier             | Value     | Supplier             | Value           | Supplier             | Value             | Supplier            | Value              |

| C0                               | Murata                  | 100nF               | Murata               | 100nF     | Murata               | 100nF           | Murata               | 100nF             | Murata              | 100nF              |

| C1                               | Murata                  | 18pF                | Murata               | 12pF      | Murata               | 8.2pF           |                      | NE                | Murata              | 7pF                |

| C2                               | Murata                  | 27pF                | Murata               | 27pF      | Murata               | 18pF            | Murata               | 8.2pF             | Murata              | 2.4pF              |

| C3                               | Murata                  | 4.3pF               | Murata               | 15pF      | Murata               | 10pF            | Murata               | 5.6pF             | Murata              | 3.6pF              |

| C4                               |                         | NE                  | Murata               | 3.9pF     | Murata               | 2.2pF           | Murata               | 2.2pF             | Murata              | 2pF                |

| C5                               | Murata                  | 8pF                 | Murata               | 4.7pF     | Murata               | 3.3pF           | Murata               | 1.8pF             | Murata              | 1.5pF              |

| C6                               | Murata                  | 220pF               | Murata               | 220pF     | Murata               | 220pF           | Murata               | 220pF             | Murata              | 330pF              |

| C7                               | Murata                  | 68nH<br>(inductor)  | Murata               | 220pF     | Murata               | 220pF           | Murata               | 220pF             | Murata              | 220pF              |

| C8                               | Murata                  | 390pF               | Murata               | 220pF     | Murata               | 220pF           | Murata               | 220pF             | Murata              | 220pF              |

| C9                               | Murata                  | 12pF                | Murata               | 12pF      | Murata               | 12pF            | Murata               | 12pF              | Murata              | 12pF               |

| C10                              | Murata                  | 10pF                | Murata               | 10pF      | Murata               | 10pF            | Murata               | 10pF              | Murata              | 10pF               |

| C11                              | Murata                  | 1µF                 | Murata               | 1µF       | Murata               | 1µF             | Murata               | 470nF             | Murata              | 1µF                |

| C12                              | Murata                  | 100nF               | Murata               | 100nF     | Murata               | 100nF           | Murata               | 100nF             | Murata              | 100nF              |

| C13                              | Murata                  | 560pF               | Murata               | 330pF     | Murata               | 330pF           | Murata               | 330pF             | Murata              | 330pF              |

| C14                              | Murata                  | 220pF               | Murata               | 1.8pF     | Murata               | 1.8pF           | Murata               | 1.2pF             |                     | NE                 |

| C15                              | Murata                  | 6.2pF               | Murata               | 1.2pF     |                      | NE              |                      | NE                |                     | NE                 |

| L0                               | Murata                  | 200nH               | Murata               | 220nH     | Murata               | 150nH           | Murata               | 100nH             | Murata              | 100nH              |

| L1                               | Coilcraft               | 39nH                | Murata               | 12nH      | Murata               | 8.2nH           | Murata               | 3nH               | Murata              | 3.6nH              |

| L2                               | Coilcraft               | 56nH                | Murata               | 12nH      | Murata               | 10nH            |                      | 0R0<br>(resistor) | Murata              | 5.1nH              |

| L3                               | Murata                  | 3.6pF<br>(cap.)     | Murata               | 15nH      | Murata               | 10nH            | Murata               | 4.3nH             | Tyco<br>Electronics | 0R0                |

| L4                               | Murata                  | 100nH               | Murata               | 47nH      | Murata               | 39nH            | Murata               | 18nH              | Murata              | 15nH               |

| L5                               | Murata                  | 47nH                | Murata               | 39nH      | Murata               | 27nH            | Murata               | 18nH              | Murata              | 18nH               |

| L6                               |                         | NE                  |                      | NE        |                      | NE              | Murata               | 22nH              | Murata              | 15nH               |

| L7                               | Murata                  | 10µH                | Murata               | 10µH      | Murata               | 10µH            | Murata               | 10µH              | Murata              | 10µH               |

| L8                               |                         | 0R0<br>(resistor)   | Murata               | 270nH     | Murata               | 100nH           | Coilcraft            | 27nH              | Coilcraft           | 27nH               |

| L9                               | Coilcraft               | 51nH                | Murata               | 15nH      | Murata               | 6.2nH           | Murata               | 2.7nH             |                     | NE                 |

| XTAL                             | NDK                     | 25 MHz              | NDK                  | 50<br>MHz | NDK                  | 50 or 52<br>MHz | NDK                  | 50 or 52<br>MHz   | NDK                 | 50 or<br>52<br>MHz |

Table 3. BOM for different bands

1. For complete BOM including part numbers, please check the corresponding reference design.

## 4 Pinout

|     | Table 4. Plnout description |     |                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|-----|-----------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin | Name                        | I/O | Description                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| 1   | GPIO_0                      | I/O | See description of GPIOs below                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| 2   | MISO                        | 0   | SPI data output pin                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 3   | MOSI                        | I   | SPI data input pin                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 4   | SCLK                        | I   | SPI clock input pin                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 5   | CSn                         | I   | SPI chip select                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| 6   | XOUT                        | 0   | Crystal oscillator output. Connect to an external 26 MHz crystal or leave floating if driving the XIN pin with an external signal source                                                                                                                                                                                    |  |  |  |  |  |

| 7   | XIN                         | I   | Crystal oscillator input. Connect to an external 26 MHz crystal or to<br>an external source. If using an external clock source with no crystal,<br>DC coupling with a nominal 0.2 VDC level is recommended with<br>minimum AC amplitude of 400 mVpp.<br>The instantaneous level at input cannot exceed the 0 - 1.4 V range. |  |  |  |  |  |

| 8   | VBAT                        | VDD | +1.8 V to +3.6 V input supply voltage                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| 9   | RXp                         | I   | Differential RF input signal for the LNA. See application diagram for a                                                                                                                                                                                                                                                     |  |  |  |  |  |

| 10  | RXn                         | I   | typical matching network                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| 11  | GND_PA                      | GND | Ground for PA.<br>To be carefully decoupled from other grounds.                                                                                                                                                                                                                                                             |  |  |  |  |  |

| 12  | ТХ                          | 0   | RF output signal                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| 13  | SMPS Ext2                   | I   | Regulated DC-DC voltage input                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 14  | SMPS Ext1                   | 0   | DC-DC output pin                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| 15  | SDN                         | I   | Shutdown input pin. 0-VDD V digital input. SDN should be = '0' in all modes except shutdown mode. When SDN ='1' the SPIRIT1 is completely shut down and the contents of the registers are lost. The GPIO and SPI ports during SHUTDOWN are in HiZ.                                                                          |  |  |  |  |  |

| 16  | VBAT                        | VDD | +1.8 V to +3.6 V input supply voltage                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| 17  | VREG <sup>(1)</sup>         | VDD | Regulated output voltage. A 100 nF decoupling capacitor is required                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 18  | GPIO3                       | I/O | General purpose I/O that may be configured through the SPI                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 19  | GPIO2                       | I/O | registers to perform various functions, including:<br>– MCU clock output                                                                                                                                                                                                                                                    |  |  |  |  |  |

| 20  | GPIO1                       | I/O | <ul> <li>FIFO status flags</li> <li>Wake-up input</li> <li>Battery level detector</li> <li>TX-RX external switch control</li> <li>Antenna diversity control</li> <li>Temperature sensor output</li> </ul>                                                                                                                   |  |  |  |  |  |

| 21  | GND                         | GND | Exposed pad ground pin                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|     |                             |     | 1                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

#### Table 4. Pinout description

1. This pin is intended for use with the SPIRIT1 only. It cannot be used to provide supply voltage to other devices.

## 5 Absolute maximum ratings and thermal data

Absolute maximum ratings are those values above which damage to the device may occur. Functional operation under these conditions is not implied. All voltages are referred to GND.

| ······································ |                                   |              |      |  |  |  |  |

|----------------------------------------|-----------------------------------|--------------|------|--|--|--|--|

| Pin                                    | Parameter                         | Value        | Unit |  |  |  |  |

| 8,14,16                                | Supply voltage and SMPS output    | -0.3 to +3.9 | V    |  |  |  |  |

| 17                                     | DC voltage on VREG                | -0.3 to +1.4 | V    |  |  |  |  |

| 1,3,4,5,15,18,19,20                    | DC voltage on digital input pins  | -0.3 to +3.9 | V    |  |  |  |  |

| 2                                      | DC voltage on digital output pins | -0.3 to +3.9 | V    |  |  |  |  |

| 11                                     | DC voltage on analog pins         | -0.3 to +3.9 | V    |  |  |  |  |

| 6,7,9,10                               | DC voltage on RX/XTAL pins        | -0.3 to +1.4 | V    |  |  |  |  |

| 13                                     | DC voltage on SMPS Ext2 pin       | -0.3 to +1.8 | V    |  |  |  |  |

| 12                                     | DC voltage on TX pin              | -0.3 to +3.9 | V    |  |  |  |  |

| T <sub>STG</sub>                       | Storage temperature range         | -40 to +125  | °C   |  |  |  |  |

| V <sub>ESD-HBM</sub>                   | Electrostatic discharge voltage   | ±1.0         | KV   |  |  |  |  |

|          | <b>.</b> |         |         |

|----------|----------|---------|---------|

| Table 5. | Absolute | maximum | ratings |

Table 6. Thermal data

| Symbol               | Parameter                           | QFN20 | Unit |

|----------------------|-------------------------------------|-------|------|

| R <sub>thj-amb</sub> | Thermal resistance junction-ambient | 45    | °C/W |

#### Table 7. Recommended operating conditions

| Symbol           | Parameter                           |     | Тур. | Max. | Unit |

|------------------|-------------------------------------|-----|------|------|------|

| V <sub>BAT</sub> | Operating battery supply voltage    | 1.8 | 3    | 3.6  | V    |

| T <sub>A</sub>   | Operating ambient temperature range | -40 |      | 105  | °C   |

## 6 Characteristics

### 6.1 General characteristics

| Symbol | Parameter           | Min.                                                                                                                                                                          | Тур. | Max. | Unit  |  |  |  |  |

|--------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|--|--|--|--|

| FREQ   |                     | 150                                                                                                                                                                           |      | 174  | MHz   |  |  |  |  |

|        | Frequency range     | 300                                                                                                                                                                           |      | 348  | MHz   |  |  |  |  |

|        |                     | 387                                                                                                                                                                           |      | 470  | MHz   |  |  |  |  |

|        |                     |                                                                                                                                                                               |      | 956  | MHz   |  |  |  |  |

|        |                     | Air data rate for each modulation scheme.<br>Note that if "Manchester", "3-out-of-6" and/or FEC encoding/decoding options are selected, the effective bit rate will be lower. |      |      |       |  |  |  |  |

|        | 2-FSK               | 1                                                                                                                                                                             |      | 500  | kBaud |  |  |  |  |

| DR     | GMSK (BT=1, BT=0.5) | 1                                                                                                                                                                             |      | 500  | kBaud |  |  |  |  |

|        | GFSK (BT=1, BT=0.5) | 1                                                                                                                                                                             | -    | 500  | kBaud |  |  |  |  |

|        | MSK                 | 1                                                                                                                                                                             |      | 500  | kBaud |  |  |  |  |

|        | OOK/ASK             | 1                                                                                                                                                                             |      | 250  | kBaud |  |  |  |  |

#### Table 8. General characteristics

### 6.2 Electrical specifications

#### 6.2.1 Electrical characteristics

Characteristics measured over recommended operating conditions unless otherwise specified. Typical values are referred to  $T_A = 25$  °C,  $V_{BAT} = 3.0$  V. All performance is referred to a 50 Ohm antenna connector, via the reference design using application diagram as in *Figure 2*, except otherwise noted.

| Symbol | Parameter               | Test conditions                     | Min. | Тур. | Max. | Unit |

|--------|-------------------------|-------------------------------------|------|------|------|------|

|        | Shutdown <sup>(1)</sup> |                                     | 2.5  |      |      |      |

|        |                         | Standby <sup>(1)</sup>              |      | 600  |      | nA   |

| IBAT   | Supply current          | Sleep <sup>(1)</sup>                | -    | 850  |      |      |

|        |                         | Ready (default mode) <sup>(1)</sup> |      | 400  |      | μA   |

|        |                         | Lock <sup>(1)</sup>                 |      | 4.4  |      | mA   |

1. See *Table 20*.

| Symbol | Parameter      | Test conditions                        | SMPS ON | SMPS OFF | Unit |

|--------|----------------|----------------------------------------|---------|----------|------|

|        |                | RX <sup>(1)</sup> 169 MHz              | 9.2     | 16.9     |      |

|        |                | RX <sup>(1)</sup> 315 MHz              | 9.2     | 16.9     |      |

|        |                | RX <sup>(1)</sup> 433 MHz              | 9.2     | 16.9     |      |

|        |                | RX <sup>(1)</sup> 868 MHz              | 9.7     | 17.6     |      |

|        |                | RX <sup>(1)</sup> 915 MHz              | 9.8     | 17.6     |      |

|        |                | RX <sup>(1)</sup> 922 MHz              | 9.8     | 17.9     |      |

|        |                | TX <sup>(1)(2)</sup> +16 dBm 169 MHz   | 54      |          |      |

|        |                | TX <sup>(1)(2)</sup> +16 dBm 315 MHz   | 52      |          |      |

|        |                | TX <sup>(1)(2)</sup> +16 dBm 433 MHz   | 49.3    |          |      |

| IBAT   | Supply surrout | TX <sup>(1)(2)</sup> +15.5 dBm 868 MHz | 44      |          | mA   |

| IDAI   | Supply current | TX <sup>(1)(2)</sup> +16 dBm 920 MHz   | 45.2    |          | ША   |

|        |                | TX <sup>(1)</sup> +11 dBm 169 MHz      | 18      | 33       |      |

|        |                | TX <sup>(1)</sup> +11 dBm 315 MHz      | 22      | 37       |      |

|        |                | TX <sup>(1)</sup> +11 dBm 433 MHz      | 19.5    | 33       |      |

|        |                | TX <sup>(1)</sup> +11 dBm 868 MHz      | 21      | 41       |      |

|        |                | TX <sup>(1)</sup> +11 dBm 920 MHz      | 20      | 39       |      |

|        |                | TX <sup>(1)</sup> -8 dBm 169 MHz       | 6       |          |      |

|        |                | TX <sup>(1)</sup> -8 dBm 315 MHz       | 6.5     |          |      |

|        |                | TX <sup>(1)</sup> -7 dBm 433 MHz       | 7       |          |      |

|        |                | TX <sup>(1)</sup> -7 dBm 868 MHz       | 7       |          |      |

Table 10. Power consumption

1. See table Table 20.

2. TX boost mode configuration V<sub>BAT</sub> = 3.6 V.

### 6.2.2 Digital SPI

| Table 11. Digital SPI input and output (SDO, SDI, SCLK, CSn, and SDN) and GPIO |

|--------------------------------------------------------------------------------|

| specification (GPIO_1-4)                                                       |

| Symbol            | Parameter            | Test condition                                                       | Min. | Тур. | Max. | Unit |

|-------------------|----------------------|----------------------------------------------------------------------|------|------|------|------|

| f <sub>clk</sub>  | Clock frequency      |                                                                      |      |      | 10   | MHz  |

| C <sub>IN</sub>   | Port I/O capacitance |                                                                      |      | 1.4  |      | pF   |

| T <sub>RISE</sub> | Rise time            | 0.1*VDD to 0.9*VDD,<br>CL=20 pF (low output<br>current programming)  |      | 6.0  |      | - ns |

|                   |                      | 0.1*VDD to 0.9*VDD,<br>CL=20 pF (high output<br>current programming) |      | 2.5  |      |      |

| Symbol            | Parameter                      | Test condition                                                                    | Min.                  | Тур. | Max.          | Unit |

|-------------------|--------------------------------|-----------------------------------------------------------------------------------|-----------------------|------|---------------|------|

| _                 |                                | 0.1*VDD to 0.9*VDD,<br>CL=20 pF (low output<br>current programming)               |                       | 7.0  |               | 20   |

| T <sub>FALL</sub> | Fall time                      | 0.1*VDD to 0.9*VDD,<br>CL=20 pF (high output<br>current programming)              |                       | 2.5  |               | ns   |

| V <sub>IH</sub>   | Logic high level input voltage |                                                                                   | VDD/2<br>+0.3         |      |               | V    |

| V <sub>IL</sub>   | Logic low level input voltage  |                                                                                   |                       |      | VDD/8<br>+0.3 | V    |

| V <sub>OH</sub>   | High level output voltage      | IOH = -2.4 mA (-4.2 mA if<br>high output current<br>capability is<br>programmed). | (5/8)*<br>VDD+<br>0.1 |      |               | V    |

| V <sub>OL</sub>   | Low level output voltage       | IOL = +2.4 mA (+4 mA if<br>high output current<br>capability is<br>programmed).   |                       |      | 0.5           | V    |

| Table 11. Digital SPI input and output (SDO, SDI, SCLK, CSn, and SDN) and GPIO |

|--------------------------------------------------------------------------------|

| specification (GPIO_1-4) (continued)                                           |

#### 6.2.3 RF receiver

Characteristics measured over recommended operating conditions unless otherwise specified. All typical values are referred to  $T_A = 25$  °C,  $V_{BAT} = 3.0$  V, no frequency offset in the RX signal. All performance is referred to a 50 Ohm antenna connector, via the reference design.

| Symbol           | Parameter                                                       | Test condition                                                                               | Min. | Тур. | Max. | Unit |

|------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------|------|------|------|------|

| RL               | Return loss                                                     | 169.4-169.475 MHz, 433-435<br>MHz, 868-868.6 MHz, 310-320<br>MHz, 902-928 MHz <sup>(1)</sup> |      |      | -10  | dB   |

| CH <sub>BW</sub> | Receiver channel bandwidth                                      |                                                                                              | 1    |      | 800  | kHz  |

| P <sub>SAT</sub> | Saturation 1% PER (packet<br>length = 20 bytes) FEC<br>DISABLED | 868 MHz 2-GFSK (BT=1) 38.4<br>kbps (20 kHz dev. CH Filter=100<br>kHz)                        |      | 10   |      | dBm  |

| IIP <sub>3</sub> | Input third order intercept                                     | Input power -50 dBm 915 MHz                                                                  | -37  | -31  | -26  | dBm  |

| Symbol                                 | Parameter                                                                                                  | Test condition                                                                                                                                     | Min. | Тур. | Max. | Unit |

|----------------------------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

|                                        |                                                                                                            | Desired channel 3 dB above<br>sensitivity level. 12.5 kHz ∆f, 2-<br>FSK 1.2 kbps, (1 kHz dev. CH<br>Filter=6 kHz)                                  |      | 49   |      | dB   |

| C/I <sub>1-CH</sub> <sup>(2) (3)</sup> | Adjacent channel rejection,<br>1% PER (packet length = 20                                                  | Desired channel 3 dB above<br>sensitivity level. 100 kHz ∆f, 2-<br>FSK 1.2 kbps, (4.8 kHz dev. CH<br>Filter=58 kHz)                                |      | 40   |      | dB   |

| C/11-CH                                | bytes) FEC DISABLED 868<br>MHz                                                                             | Desired channel 3 dB above<br>sensitivity level. 200 kHz ∆f, 2-<br>GFSK (BT=1) 38.4 kbps, (20 kHz<br>dev. CH Filter=100 kHz)                       |      | 40   |      | dB   |

|                                        |                                                                                                            | Desired channel 3 dB above<br>sensitivity level. 750 kHz $\Delta$ f, 2-<br>GFSK (BT=1) 250 kbps, (127 kHz<br>dev. CH Filter=540 kHz)               |      | 38   |      | dB   |

|                                        |                                                                                                            | Desired channel 3 dB above<br>sensitivity level. 25 kHz ∆f, 2-FSK<br>1.2 kbps, (1 kHz dev. CH Filter=6<br>kHz)                                     |      | 52   |      | dB   |

| C/I <sub>2-CH</sub> <sup>(4)</sup>     | Alternate channel rejection,<br>1% PER (packet length = 20<br>bytes)                                       | Desired channel 3 dB above<br>sensitivity level. 200 kHz ∆f, 2-<br>FSK 1.2 kbps, (4.8 kHz dev. CH<br>Filter=58 kHz)                                |      | 43   |      | dB   |

| 0/12-CH                                | FEC DISABLED<br>868 MHz                                                                                    | Desired channel 3 dB above<br>sensitivity level. 400 kHz ∆f, 2-<br>GFSK (BT=1) 38.4 kbps, (20 kHz<br>dev. CH Filter=100 kHz)                       |      | 44   |      | dB   |

|                                        |                                                                                                            | Desired channel 3 dB above<br>sensitivity level. 1.5 MHz $\Delta$ f, 2-<br>GFSK (BT=1) 250 kbps, (127 kHz<br>dev. CH Filter=540 kHz)               |      | 46   |      | dB   |

| IM <sub>REJ</sub> <sup>(4)</sup>       | Image rejection, 1% PER<br>(packet length = 20 bytes)<br>1% PER (packet length = 20<br>bytes) FEC DISABLED | 868 MHz 2-GFSK (BT=1) 38.4<br>kbps (20kHz dev. CH Filter=100<br>kHz), desired channel 3 dB above<br>the sensitivity limit, with IQC<br>correction. |      | 47   |      | dB   |

| RX <sub>BLK</sub> <sup>(4)</sup>       | Blocking at offset above the upper band edge and below                                                     | @ 2 MHz offset, 868 MHz 2-<br>GFSK (BT=1) 38.4kbps, desired<br>channel 3 dB above the sensitivity<br>limit                                         |      | -42  |      | dBm  |

|                                        | the lower band edge 1%<br>BER                                                                              | @ 10 MHz offset, 868 MHz 2-<br>GFSK (BT=1) 38.4kbps, desired<br>channel 3 dB above the sensitivity<br>limit                                        |      | -40  |      | dBm  |

| Table 12. RF receiver characteristics (continued |

|--------------------------------------------------|

|--------------------------------------------------|

| Symbol             | Parameter                                                              | Test condition                                              | Min.                | Тур.                                | Max. | Unit  |

|--------------------|------------------------------------------------------------------------|-------------------------------------------------------------|---------------------|-------------------------------------|------|-------|

|                    |                                                                        | RF = 170 MHz, f< 1 GHz                                      |                     | -65                                 |      |       |

|                    |                                                                        | RF = 170 MHz, 1 GHz < f < 4 GHz                             |                     | -69                                 |      |       |

|                    | Spurious emissions                                                     | RF = 433 MHz - 435 MHz, f< 1<br>GHz                         |                     | -63                                 |      |       |

|                    | (maximum values according to ETSI EN 300 220-1)                        | RF = 433 MHz - 435 MHz, 1 GHz<br>< f < 4 GHz                |                     | -83                                 |      |       |

|                    |                                                                        | RF = 868 MHz, f< 1 GHz                                      |                     | -70                                 |      |       |

|                    |                                                                        | RF = 868 MHz, 1 GHz < f < 6 GHz                             |                     | -60                                 |      |       |

|                    | Spurious emissions (maxi-                                              | RF = 312 MHz - 315 MHz, f< 1<br>GHz                         |                     | -69                                 |      |       |

|                    | mum values according to ARIB STD-T93)                                  | RF = 312 MHz - 315 MHz, f> 1<br>GHz                         |                     | -59                                 |      | dBm   |

| RX <sub>SPUR</sub> | Spurious emissions (maxi-<br>mum values according to<br>ARIB STD-T67)  | RF = 426 MHz - 470 MHz                                      |                     | -61                                 |      | UDIII |

|                    |                                                                        | RF = 920 MHz - 924 MHz, f< 710<br>MHz                       |                     |                                     |      |       |

|                    |                                                                        | RF = 920 MHz - 924 MHz, 710<br>MHz < f < 915 MHz            |                     | <-70                                |      |       |

|                    | Spurious emissions (maxi-<br>mum values according to<br>ARIB STD-T108) | RF = 920 MHz - 924 MHz, 915<br>MHz < f < 930 MHz            |                     | <-70                                |      |       |

|                    |                                                                        | RF = 920 MHz - 924 MHz, 930<br>MHz < f < 1 GHz              |                     |                                     |      |       |

|                    |                                                                        | RF = 920 MHz - 924 MHz, f> 1<br>GHz                         | /Hz - 924 MHz, f> 1 | -75                                 |      |       |

| ZIN, RX            | Differential Input Impedance<br>(simulated values)                     | Max RX gain<br>RF = 170 MHz<br>RF = 315 MHz<br>RF = 433 MHz |                     | 200 - j36<br>180 - j57<br>170 - j70 |      | Ω     |

|                    |                                                                        | RF = 868 MHz<br>RF = 915 MHz<br>RF = 922 MHz                |                     | 118 - j87<br>113 - j87<br>113 - j87 |      |       |

1. Guaranteed in an entire single sub band. Reference design can be different for different application bands.

2. Interferer is CW signal (as specified by ETSI EN 300 220 v1).

3. Selectivity performance is guaranteed if no SPI accesses are performed during reception or SPI clock is below 1 MHz.

4. Blocker is CW signal (as specified by ETSI EN 300 220 v1).

| Symbol             | Parameter                                          | Test condition                                                        | SMPS ON | SMPS OFF | Unit |

|--------------------|----------------------------------------------------|-----------------------------------------------------------------------|---------|----------|------|

|                    |                                                    | 169 MHz 2-FSK 1.2kbps<br>(4 kHz dev. CH Filter=10 kHz)                | -117    | -123     | dBm  |

|                    | Sensitivity, 1% BER<br>(according to W-MBUS N      | 169 MHz 2-GFSK (BT=0.5)<br>2.4kbps (2.4 kHz dev. CH<br>Filter=7 kHz)  | -114    | -121     | dBm  |

| DV                 | mode specification)                                | 169 MHz 2-FSK 38.4kbps (20 kHz<br>dev. CH Filter=100 kHz)             | -104    | -109     | dBm  |

| RX <sub>SENS</sub> |                                                    | 169 MHz 2-GFSK (BT=0.5)<br>50 kbps (25 kHz dev. CH<br>Filter=100 kHz) | -104    | -108     | dBm  |

|                    | Sensitivity, 1% PER (packet length = 20 bytes) FEC | 315 MHz 2-FSK 1.2 kbps (4.8 kHz<br>dev. CH Filter=58 kHz)             | -109    | -110     | dBm  |

|                    | DISABLED                                           | 315 MHz MSK 500 kbps (CH<br>Filter=800 kHz)                           | -88     | -88      | dBm  |

| Table 13 | . RF | receiver | characteristics | - sensitivity |

|----------|------|----------|-----------------|---------------|

|----------|------|----------|-----------------|---------------|

| Symbol             | Parameter                                                         | Test condition                                                        | SMPS ON | SMPS OFF | Unit |

|--------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------|---------|----------|------|

|                    |                                                                   | 433 MHz 2-FSK 1.2 kbps (1 kHz<br>dev. CH Filter=6 kHz)                | -116    | -120     | dBm  |

|                    | Sensitivity, 1% PER (packet                                       | 433 MHz 2-GFSK (BT=1) 1.2<br>kbps (4.8 kHz dev. CH Filter=58<br>kHz)  | -106    | -110     | dBm  |

|                    | length = 20 bytes) FEC<br>DISABLED                                | 433 MHz 2-GFSK (BT=1) 38.4<br>kbps (20 kHz dev. CH Filter=100<br>kHz) | -103    | -107     | dBm  |

|                    |                                                                   | 433 MHz 2-GFSK (BT=1) 250<br>kbps (127 kHz dev. CH Filter=540<br>kHz) | -96     | -100     | dBm  |

|                    |                                                                   | 868 MHz 2-FSK 1.2 kbps (1 kHz<br>dev. CH Filter=6 kHz)                | -118    | -118     | dBm  |

|                    |                                                                   | 868 MHz 2-GFSK (BT=1) 1.2<br>kbps (4.8 kHz dev. CH Filter=58<br>kHz)  | -108    | -109     | dBm  |

|                    | Sensitivity, 1% PER (packet<br>length = 20 bytes) FEC<br>DISABLED | 868 MHz 2-GFSK (BT=1) 38.4<br>kbps (20 kHz dev. CH Filter=100<br>kHz) | -105    | -106     | dBm  |

| RX <sub>SENS</sub> |                                                                   | 868 MHz GFSK (BT=1) 250 kbps<br>(127 kHz dev. CH Filter=540 kHz)      | -98     | -99      | dBm  |

|                    |                                                                   | 868 MHz MSK 250 kbps (CH<br>Filter=540 kHz)                           | -93     | -94      | dBm  |

|                    |                                                                   | 915 MHz 2-FSK 1.2 kbps (4.8 kHz<br>dev. CH Filter=58 kHz)             | -108    | -109     | dBm  |

|                    | Sensitivity, 1% PER (packet<br>length = 20 bytes) FEC             | 915 MHz 2-FSK 38.4 kbps (20<br>kHz dev. CH Filter =100 kHz)           | -106    | -106     | dBm  |

|                    | DISABLED                                                          | 915 MHz 2-FSK 250 kbps (127<br>kHz dev. CH Filter=540 kHz)            | -98     | -99      | dBm  |

|                    |                                                                   | 915 MHz MSK 500 kbps (CH<br>Filter=800 kHz)                           | -94     | -95      | dBm  |

|                    |                                                                   | 922 MHz 2-FSK 1.2 kbps (4.8 kHz<br>dev. CH Filter=58 kHz)             | -108    | -109     | dBm  |

|                    | Sensitivity, 1% PER (packet length = 20 bytes) FEC                | 922 MHz 2-FSK 38.4 kbps (20<br>kHz dev. CH Filter =100 kHz)           | -106    | -106     | dBm  |

|                    | DISABLED                                                          | 922 MHz 2-FSK 250 kbps (127<br>kHz dev. CH Filter=540 kHz)            | -98     | -99      | dBm  |

|                    |                                                                   | 922 MHz MSK 500 kbps (CH<br>Filter=800 kHz)                           | -94     | -95      | dBm  |

| Symbol             | Parameter                                             | Test condition                               | SMPS ON | SMPS OFF | Unit |

|--------------------|-------------------------------------------------------|----------------------------------------------|---------|----------|------|

|                    |                                                       | 433 MHz OOK 1.2 kbps (CH<br>Filter=6 kHz)    | -116    | -117     | dBm  |

|                    | Sensitivity, 1% PER (packet<br>length = 20 bytes) FEC | 433 MHz OOK 2.4 kbps (CH<br>Filter=12 kHz)   | -113    | -116     | dBm  |

|                    | DISABLED <sup>(1)</sup>                               | 433 MHz OOK 38.4 kbps (CH<br>Filter=100 kHz) | -99     | -100     | dBm  |

| PY                 |                                                       | 433 MHz OOK 250 kbps (CH<br>Filter=540 kHz)  | -87     | -87      | dBm  |

| RX <sub>SENS</sub> |                                                       | 868 MHz OOK 1.2 kbps (CH<br>Filter=6 kHz)    | -116    | -116     | dBm  |

|                    | Sensitivity, 1% PER (packet<br>length = 20 bytes) FEC | 868 MHz OOK 2.4 kbps (CH<br>Filter=12 kHz)   | -113    | -114     | dBm  |

|                    | DISABLED <sup>(2)</sup>                               | 868 MHz OOK 38.4 kbps (CH<br>Filter=100 kHz) | -100    | -100     | dBm  |

|                    |                                                       | 868 MHz OOK 250 kbps (CH<br>Filter=540 kHz)  | -90     | -90      | dBm  |

Table 13. RF receiver characteristics - sensitivity (continued)

1. In OOK modulation, indicated value represents mean power.

#### 6.2.4 RF transmitter

Characteristics measured over recommended operating conditions unless otherwise specified. All typical values are referred to  $T_A = 25$  °C,  $V_{BAT} = 3.0$  V. All performance is referred to a 50 Ohm antenna connector, via the reference design.

| Symbol                        | Parameter                                 | Test conditions                                                                                          | Min. | Тур. | Max. | Unit |

|-------------------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------|------|------|------|------|

| P <sub>MAX_TX_BO</sub><br>OST | Maximum output<br>power <sup>(1)(2)</sup> | Delivered to a 50 Ohm single-<br>ended load via reference design<br>using TX boost mode<br>configuration | -    | 16   |      | dBm  |

| P <sub>MAX</sub>              | Maximum output<br>power <sup>(2)</sup>    | Delivered to a 50 Ohm single-<br>ended load via reference design                                         | -    | 11   |      | dBm  |

| P <sub>MIN</sub>              | Minimum output power                      | Delivered to a 50 Ohm single-<br>ended load via reference design                                         | -    | -30  |      | dBm  |

| P <sub>STEP</sub>             | Output power step                         |                                                                                                          | -    | 0.5  |      | dB   |

51

| Symbol                 | Parameter                                                                          | Test conditions                                                            | Min. | Тур. | Max.  | Unit |

|------------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------|------|-------|------|

|                        |                                                                                    | RF = 170 MHz, frequencies below<br>1 GHz                                   | -    |      | -36   | dBm  |

|                        |                                                                                    | RF = 170 MHz, Frequencies<br>above 1 GHz                                   | -    |      | < -60 | dBm  |

|                        |                                                                                    | RF = 170 MHz, frequencies within<br>47-74, 87.5-108,174-230,470-862<br>MHz | -    |      | -55   | dBm  |

|                        | Unwanted emissions                                                                 | RF = 434 MHz, frequencies below<br>1 GHz                                   | -    |      | -42   | dBm  |

| P <sub>SPUR,ETSI</sub> | according to ETSI<br>EN300 220-1<br>(harmonic included,<br>using reference design) | RF = 434 MHz, Frequencies<br>above 1 GHz                                   | -    |      | -46   | dBm  |

|                        |                                                                                    | RF = 434 MHz, frequencies within<br>47-74, 87.5-108,174-230,470-862<br>MHz | -    |      | -61   | dBm  |

|                        |                                                                                    | RF = 868 MHz, frequencies below<br>1 GHz                                   | -    |      | -51   | dBm  |

|                        |                                                                                    | RF = 868 MHz, Frequencies<br>above 1 GHz                                   | -    |      | -40   | dBm  |

|                        |                                                                                    | RF = 868 MHz, frequencies within<br>47-74, 87.5-108,174-230,470-862<br>MHz | -    |      | -54   | dBm  |

Table 14. RF transmitter characteristics (continued)

| Symbol                | Parameter                                        | Test conditions                                                                                                                              | Min. | Тур. | Max. | Unit |

|-----------------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

|                       |                                                  | RF = 310-320 MHz, harmonics<br>(measured with max output<br>power)                                                                           | -    |      | -37  | dBm  |

|                       |                                                  | RF = 310-320 MHz, 1.705 MHz<br><f< 30="" mhz<="" td=""><td>-</td><td></td><td>&lt;-60</td><td>dBm</td></f<>                                  | -    |      | <-60 | dBm  |

|                       |                                                  | RF = 310-320 MHz, 30 MHz <f<<br>88 MHz</f<<br>                                                                                               | -    |      | <-60 | dBm  |

|                       |                                                  | RF = 310-320 MHz, 88 MHz <f<<br>216 MHz</f<<br>                                                                                              | -    |      | <-60 | dBm  |

|                       | Unwanted emissions                               | RF = 310-320 MHz, 216 MHz <f<<br>960 MHz</f<<br>                                                                                             | -    |      | <-60 | dBm  |

| P <sub>SPUR,FCC</sub> | according to FCC part                            | RF = 310-320 MHz, 960 MHz <f< td=""><td>-</td><td></td><td>&lt;-60</td><td>dBm</td></f<>                                                     | -    |      | <-60 | dBm  |

|                       | 15(harmonic included,<br>using reference design) | RF = 902-928 MHz, 1.705 MHz<br><f< (@="" 30="" max="" mhz="" output="" power)<="" td=""><td>-</td><td></td><td>&lt;-70</td><td>dBm</td></f<> | -    |      | <-70 | dBm  |

|                       |                                                  | RF = 902-928 MHz, 30 MHz <f<<br>88 MHz (@ max output power)</f<<br>                                                                          | -    |      | <-70 | dBm  |

|                       |                                                  | RF = 902-928 MHz, 88 MHz <f<<br>216 MHz (@ max output power)</f<<br>                                                                         | -    |      | <-70 | dBm  |

|                       |                                                  | RF = 902-928 MHz, 216 MHz <f<<br>960 MHz (@ max output power)</f<<br>                                                                        | -    |      | -52  | dBm  |

|                       |                                                  | RF = 902-928 MHz, 960 MHz <f<br>(@ max output power)</f<br>                                                                                  | -    |      | -41  | dBm  |

|                       |                                                  | 2 <sup>nd</sup> and 7 <sup>th</sup> harmonics                                                                                                | -    |      | -25  | dBc  |

Table 14. RF transmitter characteristics (continued)

| Symbol                 | Parameter          | Test conditions                                                                                                                 | Min. | Тур. | Max. | Unit |

|------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

|                        |                    | RF = 312-315 MHz, frequency<br>below 1 GHz (@ max output<br>power, according to ARIB STD-<br>T93)                               | -    |      | -41  | dBm  |

|                        |                    | RF = 312-315 MHz, frequency<br>above 1 GHz (@ max output<br>power, according to ARIB STD-<br>T93)                               | -    |      | -48  | dBm  |

|                        |                    | RF = 426-470 MHz (@ max output<br>power, according to ARIB STD-<br>T67)                                                         | -    |      | <-40 | dBm  |

|                        |                    | RF = 915-917 MHz and<br>RF = 920-930 MHz, f< 710 MHz<br>(@ max output power, according<br>to ARIB STD-T108)                     | -    |      | <-55 | dBm  |

|                        |                    | RF = 915-917 MHz and<br>RF = 920-930 MHz, 710 MHz <f<<br>915 MHz (@ max output power,<br/>according to ARIB STD-T108)</f<<br>   | -    |      | -55  | dBm  |

| D                      | Unwanted emissions | RF = 915-917 MHz and<br>RF = 924-930 MHz, 915 MHz <f<<br>930 MHz (@ max output power,<br/>according to ARIB STD-T108)</f<<br>   | -    |      | -36  | dBm  |

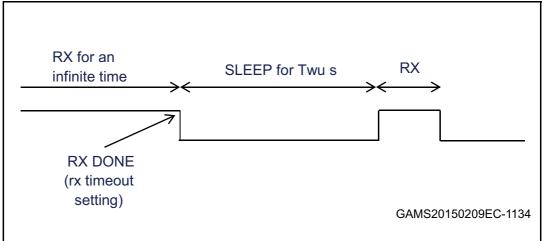

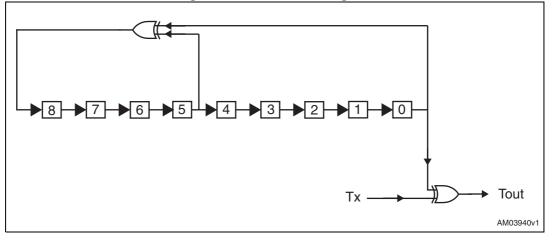

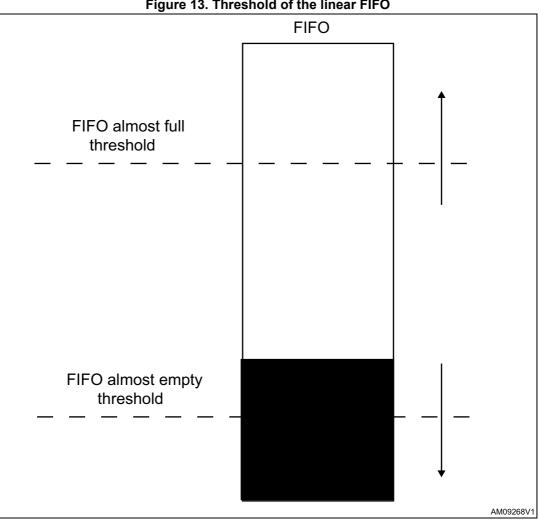

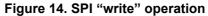

| P <sub>SPUR,ARIB</sub> | according to ARIB  | RF = 920-924 MHz, 915 MHz <f<<br>920.3 MHz (@ max output power,<br/>according to ARIB STD-T108)</f<<br>                         | -    |      | <-36 | dBm  |