- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- STM32H503RB I3C Target TX-FIFO Size Question

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32H503RB I3C Target TX-FIFO Size Question

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-07-04 3:45 AM

I am using NUCLEO-H503RB as I3C Target with LL library.

What's the minimum size of TX-FIFO available when I3C Target is reading by Controller?

I setup I3C Target TX-FIFO using function "LL_I3C_ConfigTxPreload" with 1 byte, but it always runs 8 bytes per time.

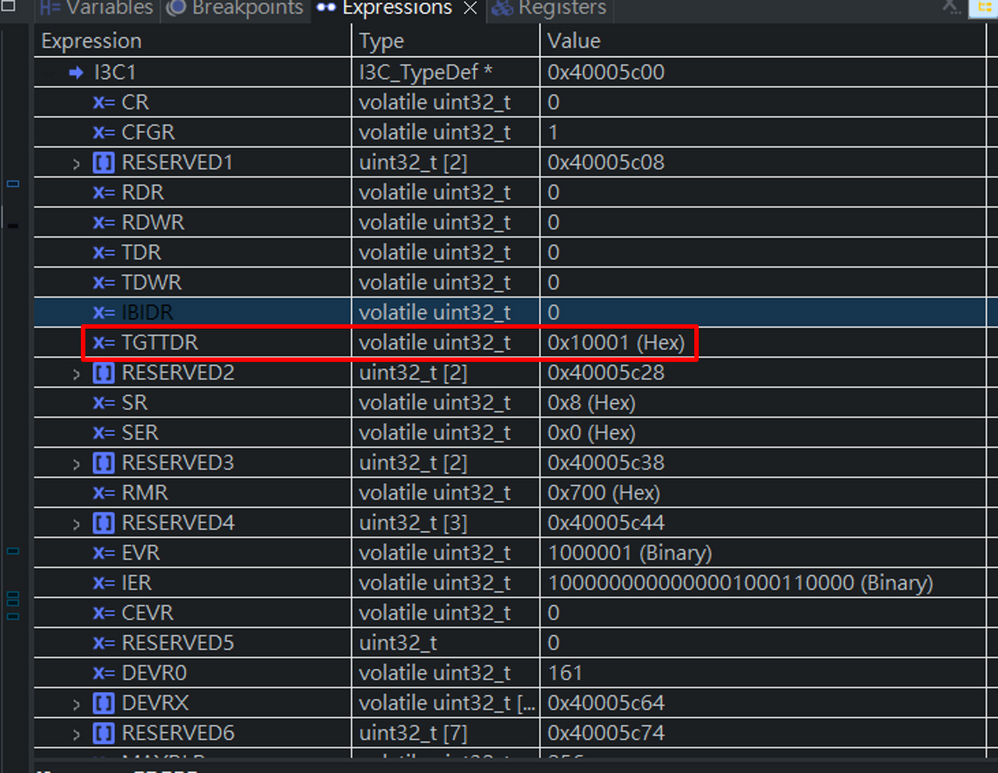

According to the datasheet, the size of TX-FIFO would be TGTTDCNT if size is lower than 8 bytes.

My TGTTDCNT settings:

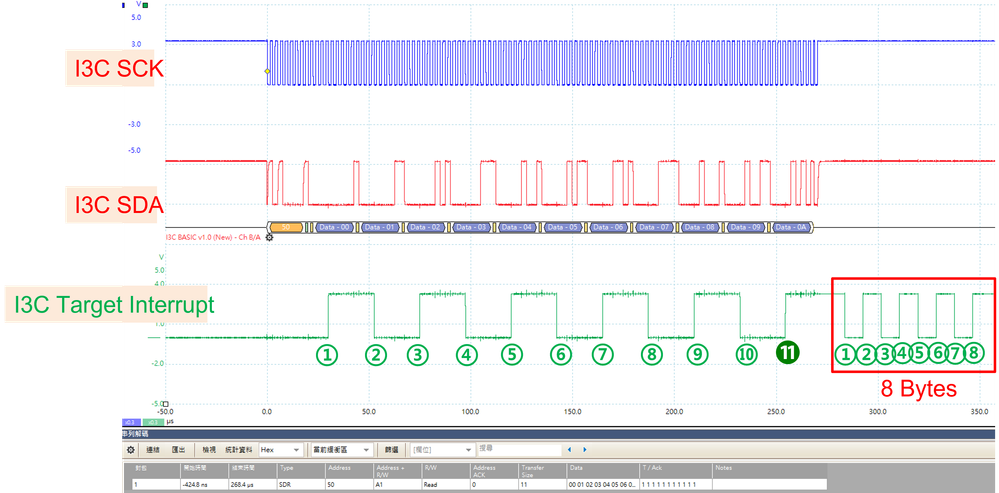

The test procedure is I3C Controller start a private read with 11 bytes and Target return the array contents.

The source code is attached, the result diagram is described below.

Solved! Go to Solution.

- Labels:

-

I3C

-

STM32H5 series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-07-04 6:27 AM

Hello @BRIAN_LAI ,

The minimum size of TX-FIFO available when I3C Target is reading by Controller is 1 byte.

You need to indicate the status of TX FIFO preload (target mode) by using : LL_I3C_IsActiveTxPreload. Then you can Set TX FIFO Preload (target mode) LL_I3C_ConfigTxPreload

Foued

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-07-04 6:27 AM

Hello @BRIAN_LAI ,

The minimum size of TX-FIFO available when I3C Target is reading by Controller is 1 byte.

You need to indicate the status of TX FIFO preload (target mode) by using : LL_I3C_IsActiveTxPreload. Then you can Set TX FIFO Preload (target mode) LL_I3C_ConfigTxPreload

Foued

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-07-04 8:04 PM

Hi @Foued_KH ,

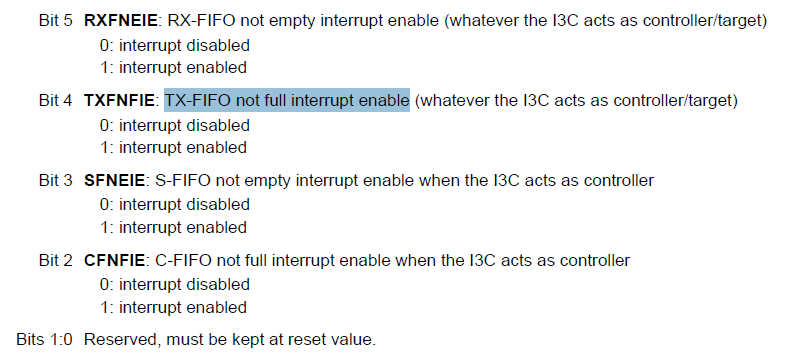

I think the root cause may be the Target Interrupt "I3C_EVR_TXFNFF" trigger when TX-FIFO is not full with 8 bytes.

Is it required to fill TX-FIFO full every time before I3C Target being read from Controller?

Are we able to implement I3C Target with using TX-FIFO only a single byte?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-07-05 1:31 AM

Hello @BRIAN_LAI ,

Just configure Tx Fifo Threshold : 1 byte

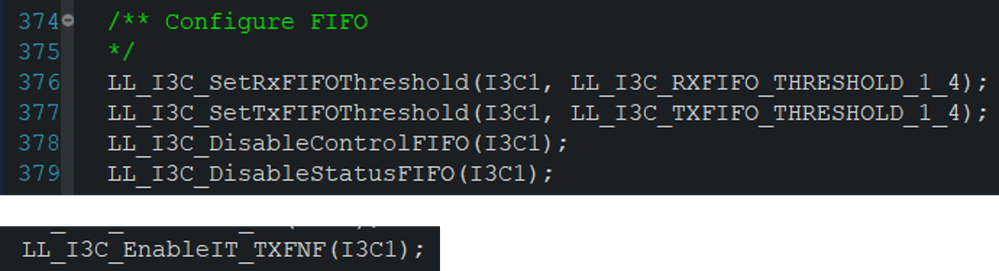

/** Configure FIFO**/

sFifoConfig.TxFifoThreshold =HAL_I3C_TXFIFO_THRESHOLD_1_4;

Foued

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-07-05 3:49 AM

Hi @Foued_KH ,

I've already setup with "I3C_TXFIFO_THRESHOLD_1_4".

The interrupt condition is "One or more free space available in TX-FIFO". (1 byte empty then trigger Interrupt)

Is it possible to change the interrupt condition to "TX-FIFO empty" ? (only trigger Interrupt when 8 bytes empty)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-07-05 5:50 AM

Are you sure that you are sharing the target code ?

because I see the process for the dynamic addressing in the target side

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-07-05 6:29 PM

Yes, I have both I3C Controller and Target on the same board.

I3C1 act as Target with Interrupt.

I3C2 act as Controller with polling (no Interrupt).