- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: SPI modes unclear

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

SPI modes unclear

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-06 04:10 AM

Hi everyone,

I am working with the SPI in slave mode on an STM32G071 and having some trouble with the different SPI modes. I set both CPOL and CPHA to 0 during initialization:

SPI_InitStruct.TransferDirection = LL_SPI_FULL_DUPLEX;

SPI_InitStruct.Mode = LL_SPI_MODE_SLAVE;

SPI_InitStruct.DataWidth = LL_SPI_DATAWIDTH_8BIT;

SPI_InitStruct.ClockPolarity = LL_SPI_POLARITY_LOW;

SPI_InitStruct.ClockPhase = LL_SPI_PHASE_1EDGE;

SPI_InitStruct.NSS = LL_SPI_NSS_HARD_INPUT;

SPI_InitStruct.BitOrder = LL_SPI_MSB_FIRST;

SPI_InitStruct.CRCCalculation = LL_SPI_CRCCALCULATION_DISABLE;

SPI_InitStruct.CRCPoly = 7;

LL_SPI_Init(SPI1, &SPI_InitStruct);According to the datasheet (see attached image) I would expect the data to be loaded on falling edge and sampled on rising edge. When I send a 0x81, I get the signal from the second attached image. Obviously the data is updated during rising edge and sampled on the falling edge. What am I missing here?

- Labels:

-

SPI

-

STM32G0 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-08 11:26 PM

Read out and check/post the SPI registers content.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-09 12:29 AM

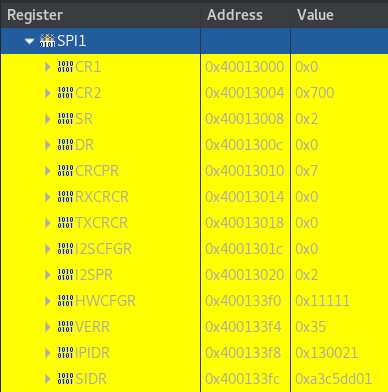

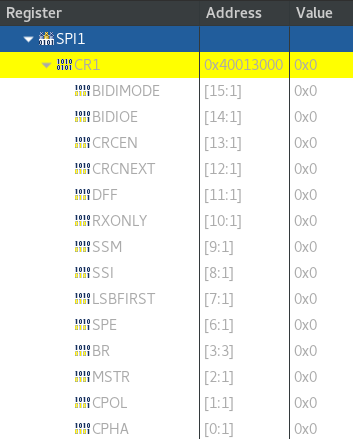

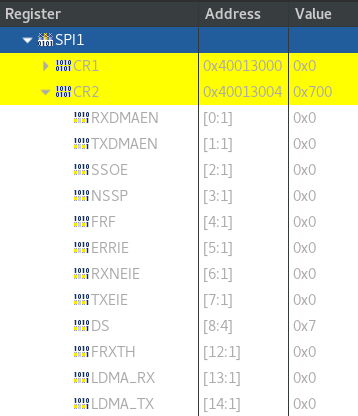

Here are the registers after initialization. Looks fine to me.

Edit: Ohh sorry, that was just the initialization, before enabling it. This will also set the SPE bit in CR1, everything else stays the same.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-09 03:34 AM

Try to observe the signals on oscilloscope.

Try a different (lower) baudrate.

Try to increase drive (OSPEEDR), first at slave's MISO, then master's SCK (but carefully, if the master is a high speed IO, highest speeds may be detrimental if you don't have proper termination).

You don't connect master and slave with flying leads, do you? If so, make sure it's as short as possible, and there's a return (ground) to each signal separately (best twisted with its signal).

JW

- ADC generates power consumption after stm32L4 enters stop mode in STM32 MCUs Embedded software

- Creating new Project with X-CUBE-AUDIO-KIT in STM32 MCUs Embedded software

- STM32H533CET6 File download error in STM32CubeIDE (MCUs)

- H7 QSPI XIP single mode demo fails in STM32 MCUs Products

- SPI Sending and Receiving Extra Bytes in STM32 MCUs Products