- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Embedded software

- Issue with stm32l433 configuring HSI

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Issue with stm32l433 configuring HSI

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-27 4:03 AM

Hi,

I have a stm32l433 chip and i'm using the internal RC Oszilator HSI.

My issue was that code generated straigth from cubemx turned the chip to run too fast, my HalTick was like 1.2 Khz instead of 1kHz.

Now i tracked the error down to a bad configuration of the HSI trim registers within the HAL libraries. Followed listed what i've found:

RCC_OscInitStruct.HSICalibrationValue = RCC_HSICALIBRATION_DEFAULT;This one gets the default value from stm32l433xx.h which says;

#if defined(RCC_ICSCR_HSITRIM_6)

#define RCC_HSICALIBRATION_DEFAULT 0x40U /*!< Default HSI calibration trimming value 64 on devices other than STM32L47x/STM32L48x */

#else

#define RCC_HSICALIBRATION_DEFAULT 0x10U /*!< Default HSI calibration trimming value 16 on STM32L47x/STM32L48x devices */

#endif /* RCC_ICSCR_HSITRIM_6 */Now this RCC_ICSCR_HSITRIM_6 is beeing defined so it takes the 0x40U.

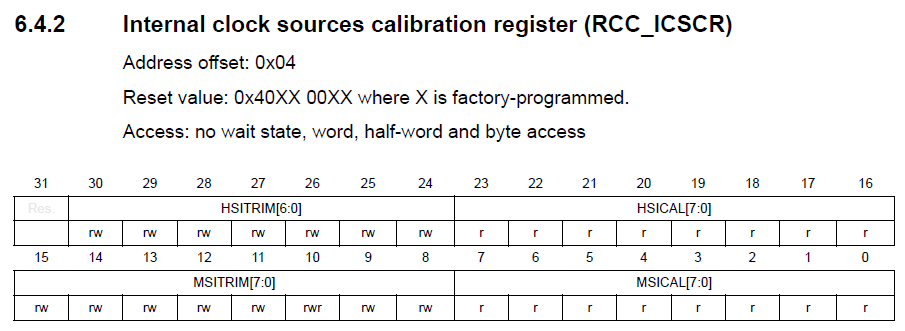

So this checks if HSITRIM is 7 bits wide. which is according datasheet correct:

Now i see the reset value should be 0x40xx 00xx. When i check this register after POR it has a value of 0x10xx00xx. Strange..

So if i now set:

RCC_OscInitStruct.HSICalibrationValue = 0x10;then the chip runs exactly at my desired speed.....

So that says either:

- Datasheet RM0394 and HAL is wrong

or:

- CHIP STM32L433CCU6 has a bug..

Did i miss something?

Cheers

Solved! Go to Solution.

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-29 2:41 AM

Hello @Nico_S ,

Welcome to the STM32 Community :smiling_face_with_smiling_eyes: and thanks for pointing out this issue.

The problem comes from the HAL and the RM0394 Rev4 as you said.

This has been raised to the appropriate team for fix:

1. RM0394 should be updated for STM32L43x/STM32L44x devices HSITRIM range.

2. The fix in HAL is planned and will be integrated soon. So, keep an eye out for the coming update.

- Correction in CMSIS Device files: stm32l431xx.h / stm32l432xx.h / stm32l433xx.h / stm32l442xx.h / stm32l443xx.h

/*!< HSITRIM configuration */

#define RCC_ICSCR_HSITRIM_Pos (24U)

#define RCC_ICSCR_HSITRIM_Msk (0x1FUL << RCC_ICSCR_HSITRIM_Pos) /*!< 0x1F000000 */

#define RCC_ICSCR_HSITRIM RCC_ICSCR_HSITRIM_Msk /*!< HSITRIM[4:0] bits */

#define RCC_ICSCR_HSITRIM_0 (0x01UL << RCC_ICSCR_HSITRIM_Pos) /*!< 0x01000000 */

#define RCC_ICSCR_HSITRIM_1 (0x02UL << RCC_ICSCR_HSITRIM_Pos) /*!< 0x02000000 */

#define RCC_ICSCR_HSITRIM_2 (0x04UL << RCC_ICSCR_HSITRIM_Pos) /*!< 0x04000000 */

#define RCC_ICSCR_HSITRIM_3 (0x08UL << RCC_ICSCR_HSITRIM_Pos) /*!< 0x08000000 */

#define RCC_ICSCR_HSITRIM_4 (0x10UL << RCC_ICSCR_HSITRIM_Pos) /*!< 0x10000000 */- Correction in HAL RCC file: stm32l4xx_hal_rcc.h

#if defined(RCC_ICSCR_HSITRIM_6)

#define RCC_HSICALIBRATION_DEFAULT 0x40U /*!< Default HSI calibration trimming value 64 on devices other than STM32L43x/STM32L44x/STM32L47x/STM32L48x */

#else

#define RCC_HSICALIBRATION_DEFAULT 0x10U /*!< Default HSI calibration trimming value 16 on STM32L43x/STM32L44x/STM32L47x/STM32L48x devices */

#endif /* RCC_ICSCR_HSITRIM_6 */- stm32l4xx_ll_rcc.h (only comments)

/**

* @brief Set HSI Calibration trimming

* @note user-programmable trimming value that is added to the HSICAL

* @note Default value is 16 on STM32L43x/STM32L44x/STM32L47x/STM32L48x or 64 on other devices,

* which, when added to the HSICAL value, should trim the HSI to 16 MHz +/- 1 %

* @rmtoll ICSCR HSITRIM LL_RCC_HSI_SetCalibTrimming

* @param Value Between Min_Data = 0 and Max_Data = 31 on STM32L43x/STM32L44x/STM32L47x/STM32L48x or

* between Min_Data = 0 and Max_Data = 127 on other devices

* @retval None

*/

__STATIC_INLINE void LL_RCC_HSI_SetCalibTrimming(uint32_t Value)

{

MODIFY_REG(RCC->ICSCR, RCC_ICSCR_HSITRIM, Value << RCC_ICSCR_HSITRIM_Pos);

}

/**

* @brief Get HSI Calibration trimming

* @rmtoll ICSCR HSITRIM LL_RCC_HSI_GetCalibTrimming

* @retval Between Min_Data = 0 and Max_Data = 31 on STM32L43x/STM32L44x/STM32L47x/STM32L48x or

* between Min_Data = 0 and Max_Data = 127 on other devices

*/

__STATIC_INLINE uint32_t LL_RCC_HSI_GetCalibTrimming(void)

{

return (uint32_t)(READ_BIT(RCC->ICSCR, RCC_ICSCR_HSITRIM) >> RCC_ICSCR_HSITRIM_Pos);

}Imen

Thanks

Imen

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-27 4:14 AM

I would suspect that HAL is wrong...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-29 2:41 AM

Hello @Nico_S ,

Welcome to the STM32 Community :smiling_face_with_smiling_eyes: and thanks for pointing out this issue.

The problem comes from the HAL and the RM0394 Rev4 as you said.

This has been raised to the appropriate team for fix:

1. RM0394 should be updated for STM32L43x/STM32L44x devices HSITRIM range.

2. The fix in HAL is planned and will be integrated soon. So, keep an eye out for the coming update.

- Correction in CMSIS Device files: stm32l431xx.h / stm32l432xx.h / stm32l433xx.h / stm32l442xx.h / stm32l443xx.h

/*!< HSITRIM configuration */

#define RCC_ICSCR_HSITRIM_Pos (24U)

#define RCC_ICSCR_HSITRIM_Msk (0x1FUL << RCC_ICSCR_HSITRIM_Pos) /*!< 0x1F000000 */

#define RCC_ICSCR_HSITRIM RCC_ICSCR_HSITRIM_Msk /*!< HSITRIM[4:0] bits */

#define RCC_ICSCR_HSITRIM_0 (0x01UL << RCC_ICSCR_HSITRIM_Pos) /*!< 0x01000000 */

#define RCC_ICSCR_HSITRIM_1 (0x02UL << RCC_ICSCR_HSITRIM_Pos) /*!< 0x02000000 */

#define RCC_ICSCR_HSITRIM_2 (0x04UL << RCC_ICSCR_HSITRIM_Pos) /*!< 0x04000000 */

#define RCC_ICSCR_HSITRIM_3 (0x08UL << RCC_ICSCR_HSITRIM_Pos) /*!< 0x08000000 */

#define RCC_ICSCR_HSITRIM_4 (0x10UL << RCC_ICSCR_HSITRIM_Pos) /*!< 0x10000000 */- Correction in HAL RCC file: stm32l4xx_hal_rcc.h

#if defined(RCC_ICSCR_HSITRIM_6)

#define RCC_HSICALIBRATION_DEFAULT 0x40U /*!< Default HSI calibration trimming value 64 on devices other than STM32L43x/STM32L44x/STM32L47x/STM32L48x */

#else

#define RCC_HSICALIBRATION_DEFAULT 0x10U /*!< Default HSI calibration trimming value 16 on STM32L43x/STM32L44x/STM32L47x/STM32L48x devices */

#endif /* RCC_ICSCR_HSITRIM_6 */- stm32l4xx_ll_rcc.h (only comments)

/**

* @brief Set HSI Calibration trimming

* @note user-programmable trimming value that is added to the HSICAL

* @note Default value is 16 on STM32L43x/STM32L44x/STM32L47x/STM32L48x or 64 on other devices,

* which, when added to the HSICAL value, should trim the HSI to 16 MHz +/- 1 %

* @rmtoll ICSCR HSITRIM LL_RCC_HSI_SetCalibTrimming

* @param Value Between Min_Data = 0 and Max_Data = 31 on STM32L43x/STM32L44x/STM32L47x/STM32L48x or

* between Min_Data = 0 and Max_Data = 127 on other devices

* @retval None

*/

__STATIC_INLINE void LL_RCC_HSI_SetCalibTrimming(uint32_t Value)

{

MODIFY_REG(RCC->ICSCR, RCC_ICSCR_HSITRIM, Value << RCC_ICSCR_HSITRIM_Pos);

}

/**

* @brief Get HSI Calibration trimming

* @rmtoll ICSCR HSITRIM LL_RCC_HSI_GetCalibTrimming

* @retval Between Min_Data = 0 and Max_Data = 31 on STM32L43x/STM32L44x/STM32L47x/STM32L48x or

* between Min_Data = 0 and Max_Data = 127 on other devices

*/

__STATIC_INLINE uint32_t LL_RCC_HSI_GetCalibTrimming(void)

{

return (uint32_t)(READ_BIT(RCC->ICSCR, RCC_ICSCR_HSITRIM) >> RCC_ICSCR_HSITRIM_Pos);

}Imen

Thanks

Imen

- Clangd preprocessor define issue - opacity stops working after toggling Configure in STM32CubeIDE for Visual Studio Code (MCUs)

- STM32N657X0 NUCLEO — Secure LED not blinking, Non-Secure LED not working at all (TrustZone + RIF configuration issue) in STM32 MCUs Embedded software

- HRTIM1, TIMA output2 configuration issue in STM32CubeMX (MCUs)

- STM32H7S78-DK: USBX standalone (CDC ACM + PIMA) works in FS; fails in HS in STM32 MCUs Embedded software

- BlueCoin RCC configuration issue / BlueCoin board (STEVAL-BCNCS01V1) in STM32 MCUs Boards and hardware tools