- STMicroelectronics Community

- MEMS and sensors

- MEMS (sensors)

- Re: How to interface 4-wired SPI with interface LS...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How to interface 4-wired SPI with interface LSM9DS0?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2013-10-09 11:29 PM

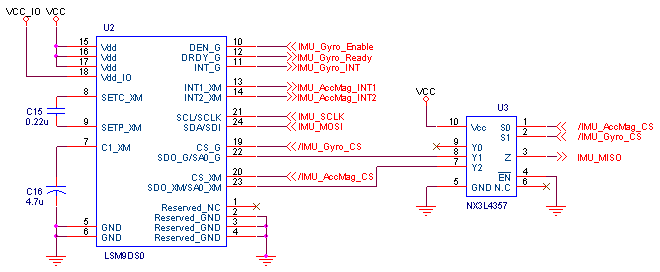

I'm designing with LSM9DS0.

And my goal is interface a 4-wired SPI with the MEMs device. This is my interface design. I add a 3:1 mux for interface 2 SDO pins into a MISO. I want to know that my approach is suitable for interfacing with a simgle 4-wired SPI. If the other idea exist, please let me know. I can't find any reference design for LSM9DS0. So I can't refer any design. Is there any reference design ST proposed? #4-wired-spi #interface-confliction #lsm9ds0 #interface

I add a 3:1 mux for interface 2 SDO pins into a MISO. I want to know that my approach is suitable for interfacing with a simgle 4-wired SPI. If the other idea exist, please let me know. I can't find any reference design for LSM9DS0. So I can't refer any design. Is there any reference design ST proposed? #4-wired-spi #interface-confliction #lsm9ds0 #interface

- Labels:

-

INEMO-Inertial Modules

-

SPI

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2013-10-23 11:16 PM

The SDO lines tri-state according to the data sheets (standard for SPI), so you just connect them together. Use CS to get data from the appropriate SDO pin. Make sure they are exclusive so there is no conflict. That is how I interpret the data, and how I will use the part.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2013-11-06 09:06 PM

Thanks ricky and there is one more question.

If I use one device as SPI, then the other device should be I2C. Because the SCL and SDA signal share with the SPI and I2C, I concern about that the I2C device has a possibility of activation. (LSM9DS0 has I2C slave functionality and the transaction of slave is started through a START signal. The START condition of I2C is defined as a HIGH to LOW transition on SDA while the SCL is held HIGH. The START signal transmitted from master to slave.) If the SPI and I2C are active on the same time, Which Interface is dominant? And, How to solve this problem? Should I avoid the confliction by controlling the SCLK and SDI's phase?- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2013-11-21 01:32 PM

Data sheet section 6 says that if CS is tied high, then part is I2C, if CS is taken low, then it is SPI, and the data transactions that take place while CS is low will be SPI, so there is no conflict between the communication standards. Since you are programming the host processor, you have control of the CS and the prootcol in use.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2014-06-24 06:50 AM

But here are two CS. I assume CS_G and CS_XM are or'ed internally to select SPI/I2C (If CS_G is 1 and CS_XM is 0, is the SDA/SDI-pin in SPI or I2C mode)?

And is there any solution for more SPI-devices than a single LSM9DS0 on the same SPI-bus?- VL53L4CX: How/where to store calibration data in Imaging (sensors)

- VD56G3 optical flow in Imaging (sensors)

- ASM330LHHXG1 does not take the DRDY flag to high in MEMS (sensors)

- Using LSM9DS1 Sensors on the STM32 WB55RG (SPI) in MEMS (sensors)

- Generating interrupts from VL53L0X pin GPIO1 in Imaging (sensors)