- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Embedded software

- Unable to run STM32F401 at 84 MHz Sysclk (works fi...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Unable to run STM32F401 at 84 MHz Sysclk (works fine at 48 MHz)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-07 02:39 AM

Hello guys :waving_hand:

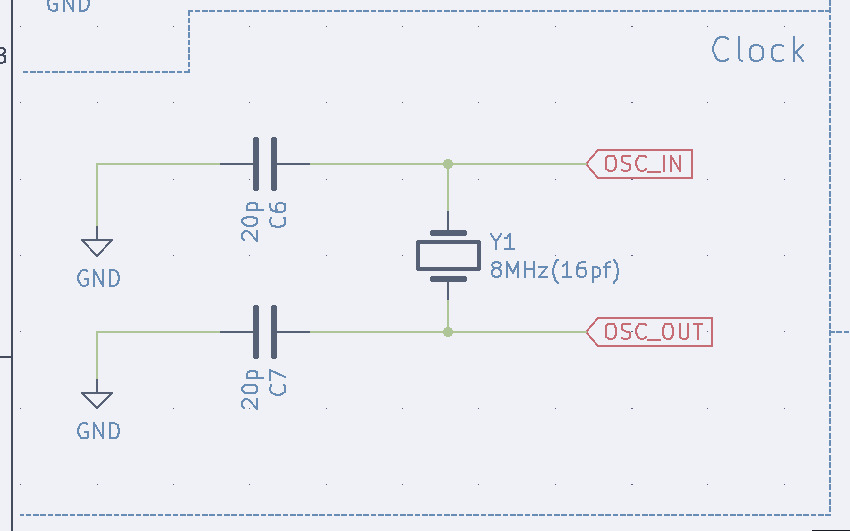

I am having a STM32F401CDU6TR on a custom board and I am not able to run it at 84 MHz SYSCLK. The source is an external 8 MHz crystal with two 22pF caps as seen here:

I created the project in CubeMX as a Makefile project. I only use CubeMX for configuring the GPIOs as well as the clock. The actual code is written and flashed via VSCode. Works great so far.

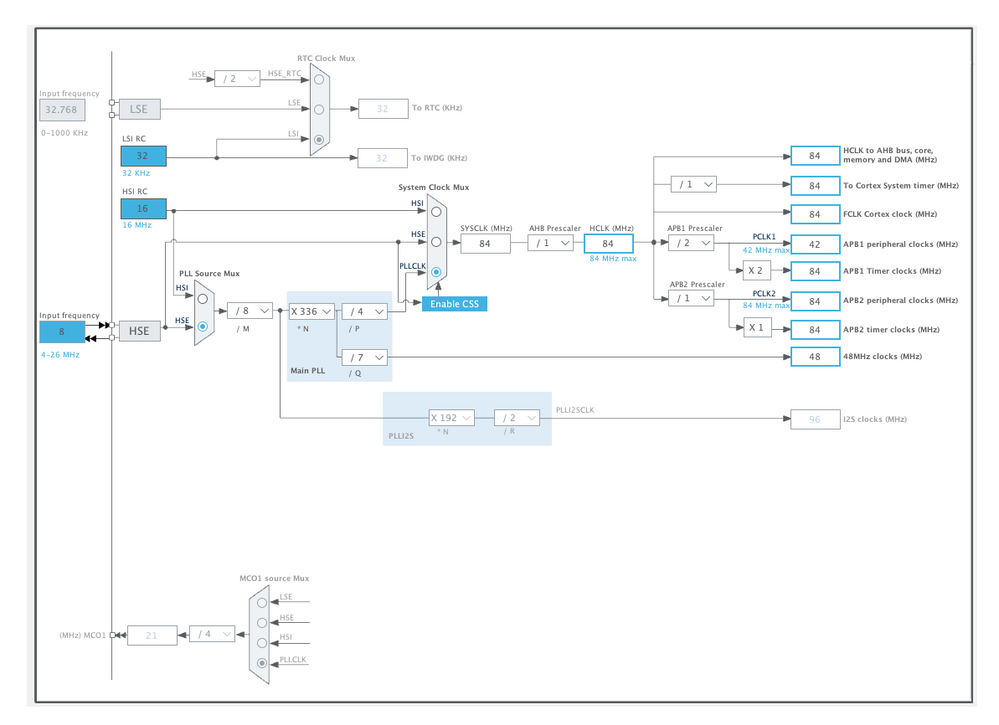

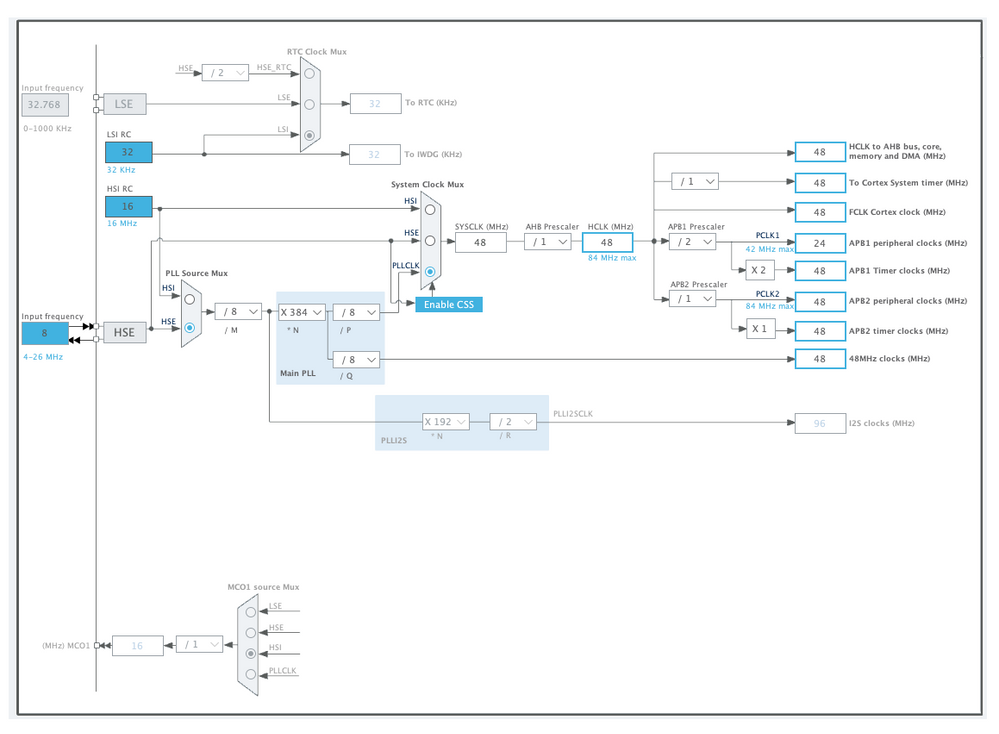

Here is my current 84 MHz clock configuration in CubeMX:

When I flash this code I always end up in a HardFault_Handler before the SystemClock_Config(); function returns.

/**

* @brief System Clock Configuration

* @retval None

*/

void SystemClock_Config(void)

{

RCC_OscInitTypeDef RCC_OscInitStruct = {0};

RCC_ClkInitTypeDef RCC_ClkInitStruct = {0};

/** Configure the main internal regulator output voltage

*/

__HAL_RCC_PWR_CLK_ENABLE();

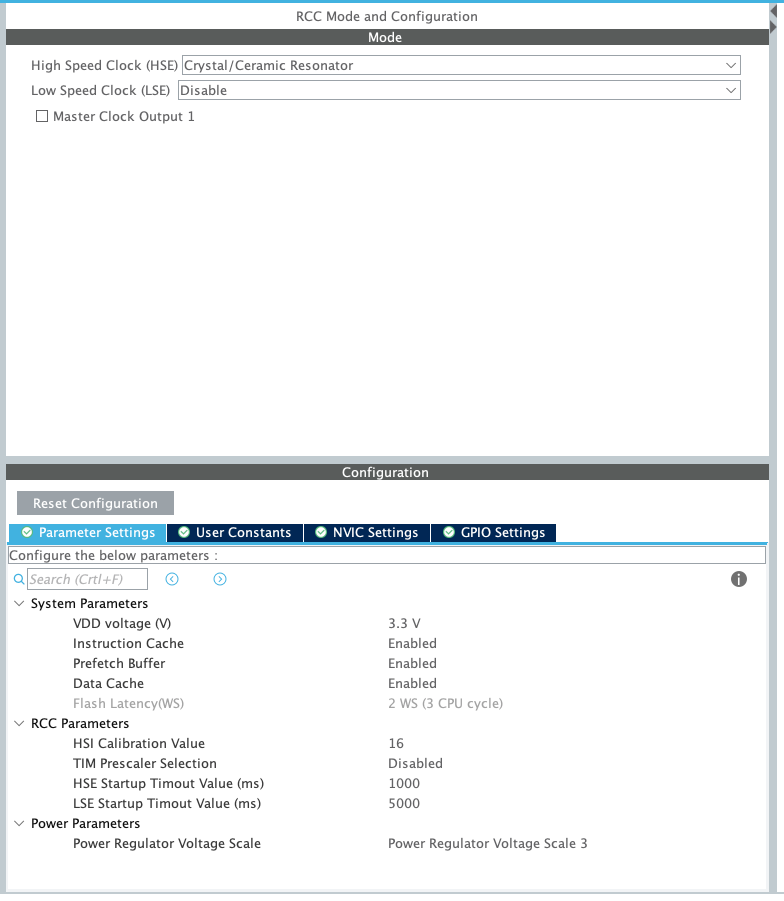

__HAL_PWR_VOLTAGESCALING_CONFIG(PWR_REGULATOR_VOLTAGE_SCALE3);

/** Initializes the RCC Oscillators according to the specified parameters

* in the RCC_OscInitTypeDef structure.

*/

RCC_OscInitStruct.OscillatorType = RCC_OSCILLATORTYPE_HSE;

RCC_OscInitStruct.HSEState = RCC_HSE_ON;

RCC_OscInitStruct.PLL.PLLState = RCC_PLL_ON;

RCC_OscInitStruct.PLL.PLLSource = RCC_PLLSOURCE_HSE;

RCC_OscInitStruct.PLL.PLLM = 8;

RCC_OscInitStruct.PLL.PLLN = 336;

RCC_OscInitStruct.PLL.PLLP = RCC_PLLP_DIV4;

RCC_OscInitStruct.PLL.PLLQ = 7;

if (HAL_RCC_OscConfig(&RCC_OscInitStruct) != HAL_OK)

{

Error_Handler();

}

/** Initializes the CPU, AHB and APB buses clocks

*/

RCC_ClkInitStruct.ClockType = RCC_CLOCKTYPE_HCLK|RCC_CLOCKTYPE_SYSCLK

|RCC_CLOCKTYPE_PCLK1|RCC_CLOCKTYPE_PCLK2;

RCC_ClkInitStruct.SYSCLKSource = RCC_SYSCLKSOURCE_PLLCLK;

RCC_ClkInitStruct.AHBCLKDivider = RCC_SYSCLK_DIV1;

RCC_ClkInitStruct.APB1CLKDivider = RCC_HCLK_DIV2;

RCC_ClkInitStruct.APB2CLKDivider = RCC_HCLK_DIV1;

if (HAL_RCC_ClockConfig(&RCC_ClkInitStruct, FLASH_LATENCY_2) != HAL_OK)

{

Error_Handler();

}

}When I activate MCO1 I can measure the HSE and PLLCLK signals with the expected frequency.

When I set the SYSCLK to 48 MHz as seen here everything works as expected.

I have no idea what is going on here 🤷�?♂�?

Thanks for your help!

Cheers,

Robin

Solved! Go to Solution.

- Labels:

-

Power

-

STM32F4 Series

-

USB

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-07 05:29 AM

Should be at least 2.2 uF, it is a bulk capacitor for the internal LDO

I'll double check the specs, the single up case might be 4.7 uF

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-07 03:40 AM

> When I flash this code I always end up in a HardFault_Handler before the SystemClock_Config(); function returns.

Single-step that code, best in disasm view (i.e. instruction by instruction) to find out where it goes into the HardFault.

Is FLASH set appropriately to your VDD and clock? Is VDD stable enough? Do you have adequate decoupling?

Try the same code on a "known good" board such as Nucleo or Disco.

Is your crystal 8MHz?

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-07 03:43 AM

"8 MHz crystal with two 22pF caps"

It actually shows 20pF

and the crystal is labelled "16pF"

Is it actually oscillating at all? If it is, is it at 8MHz?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-07 04:29 AM

Thanks for taking time! Here are my answers.

> Single-step that code, best in disasm view (i.e. instruction by instruction) to find out where it goes into the HardFault.

Will do that later this day. Thanks.

> Is FLASH set appropriately to your VDD and clock?

I am not sure what you mean by that? The voltage of the flash? How do I set that?

> Is VDD stable enough?

I am not sure what is considered stable. I'll do some measurements later while powering on the board.

I am looking for a voltage drop on that line? And or jitter?

> Do you have adequate decoupling?

I placed 100n decoupling caps across all VDD/GND supply pins around the MCU as close to the MCU as possible.

I might be able to refactor this so the caps are closer. But when I take a look at a nucleo board those seem to be even further away from the MCU.

But I have to admit that my decoupling design could be better. Do you think that is the issue?

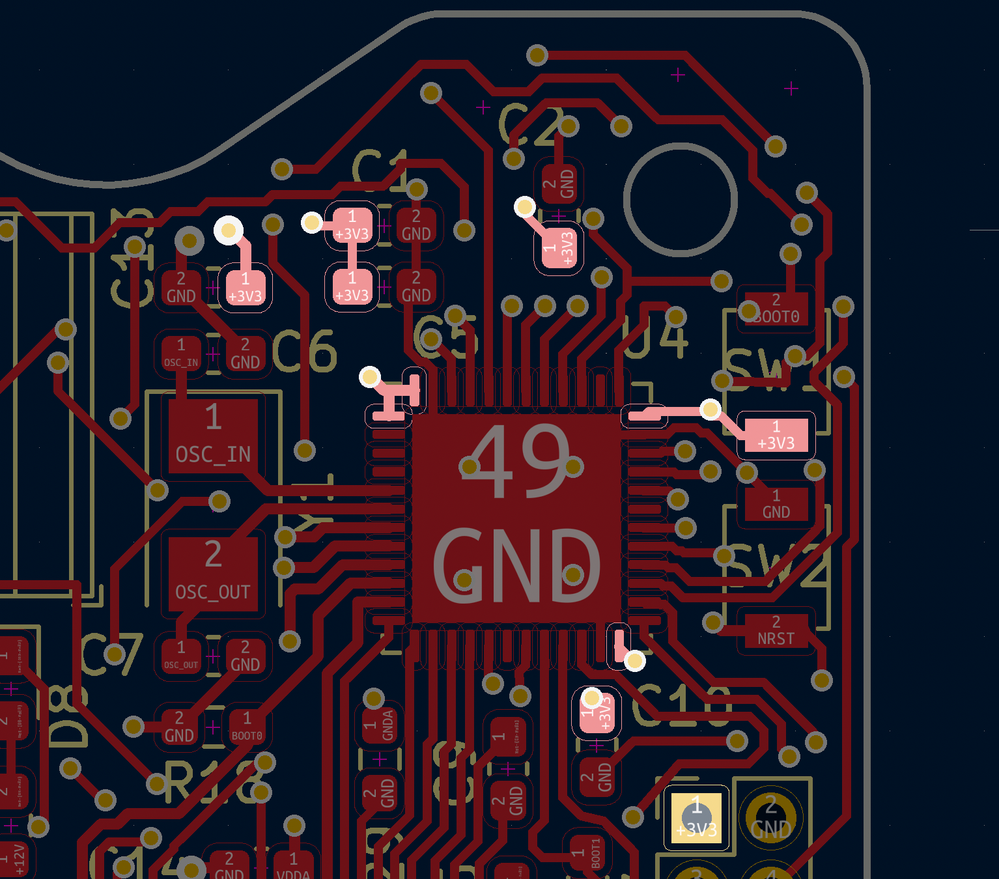

Here's a picture of the board layout with the 3v3 net highlighted. Back copper is hidden. Its a 4 layer board.

> It actually shows 20pF

You're right. I meant to say 20 pF. Thats what I have installed.

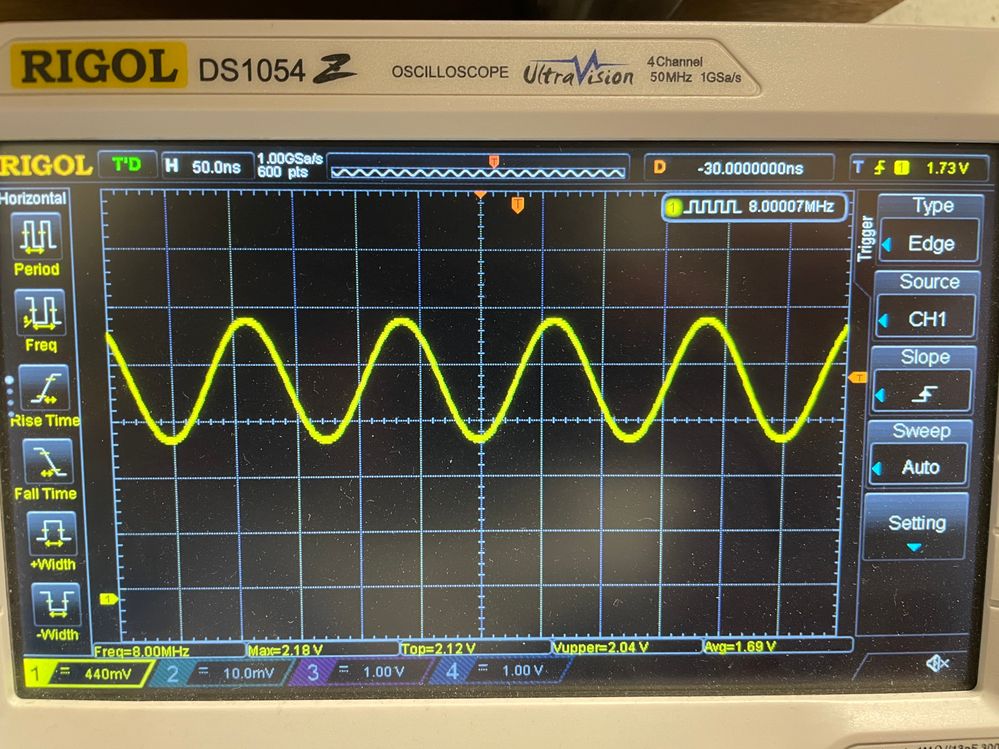

> Is it actually oscillating at all? If it is, is it at 8MHz?

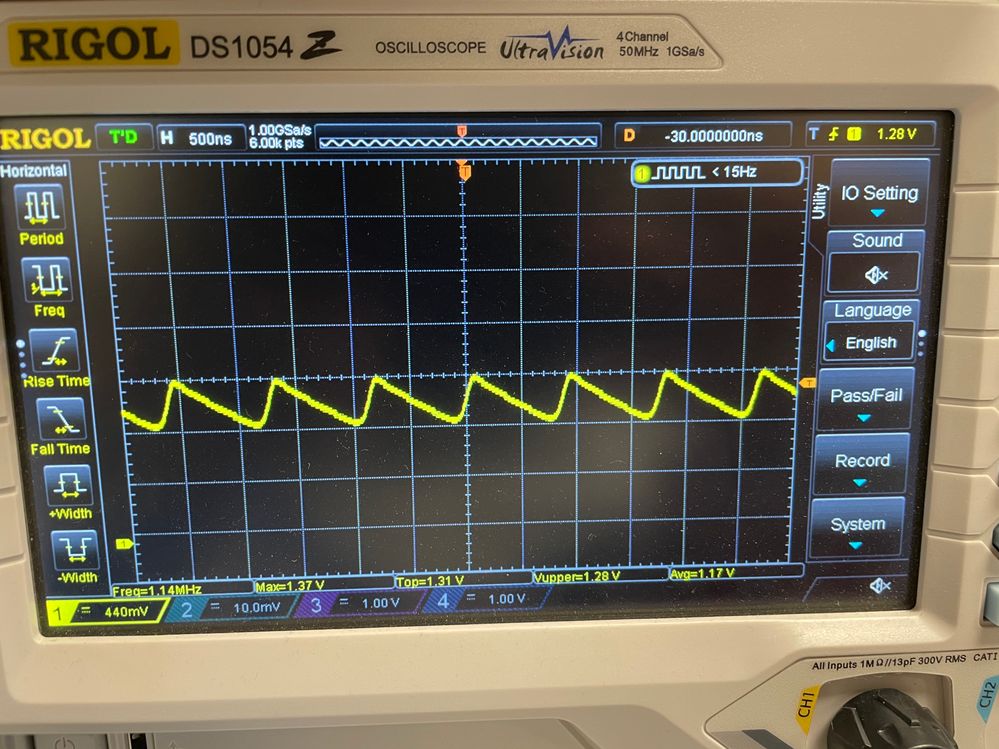

It is oscillating at exactly 8 MHz. The only thing that bothers me is the voltage peak to peak is a little low, right?

Might also be because I am introducing an error when measuring with my 10x probe.

I measured at one of the crystals leads.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-07 04:42 AM

HSE looks fine

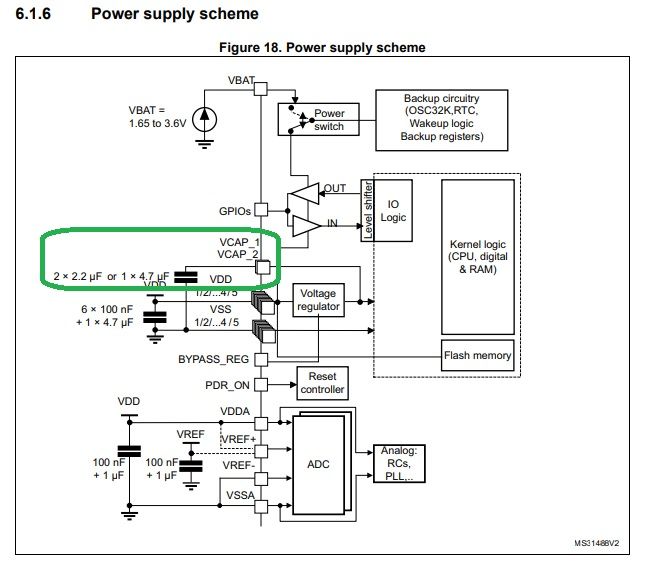

What's going on with VCAP? Check voltage and capacitor value.

Should see 1.25V

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-07 05:04 AM

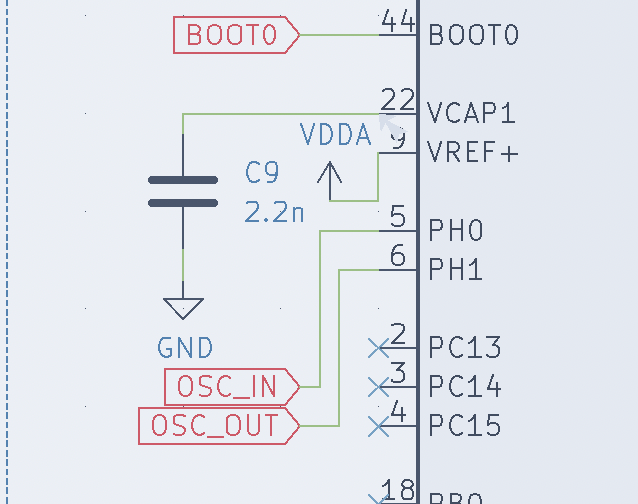

> What's going on with VCAP? Check voltage and capacitor value.

The value is 2.2n as seen here

Thats what I see when measuring on the MCU facing side of the C9. Seems fine, right?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-07 05:29 AM

Should be at least 2.2 uF, it is a bulk capacitor for the internal LDO

I'll double check the specs, the single up case might be 4.7 uF

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-07 05:36 AM

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-07 05:39 AM

Oh you are right!

Thats clearly a bug.

Thanks for pointing it out. Will swap that for a 4.7uF one.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-07 05:40 AM

I hate how Clive always beats us all in this game... must be the inferior quality of my crystal cube... 😉

Jan

- Unable to get maximum SYSCLK of 480MHz on STM32H743XIH in STM32 MCUs products

- What is the correct systemClock_Config to use in order to have USB OTG FS with a 48MHz external cristal as the clock source ? in STM32 MCUs Embedded software

- How to use STM32F401 mcu to driver color sensor. in STM32CubeMX (MCUs)

- Configure clock at runtime on STM32F401CCU6 causes lockup/crash? in STM32 MCUs products

- Trouble configuring the system clock for an STM32F303K8T6 for speeds higher than 16Mhz (using CubeMX and CubeIDE) in STM32CubeIDE (MCUs)