- STMicroelectronics Community

- STM32 MCUs Software development tools

- STM32CubeMX (MCUs)

- Possible CubeMX clock setup bugs (STM32H7)

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Possible CubeMX clock setup bugs (STM32H7)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-03 12:16 PM

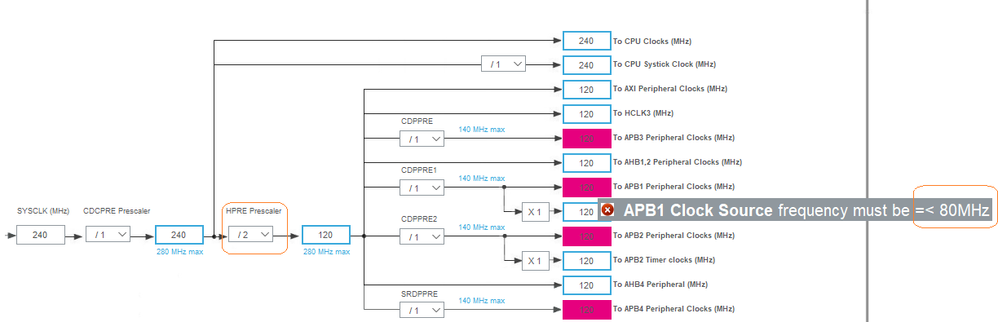

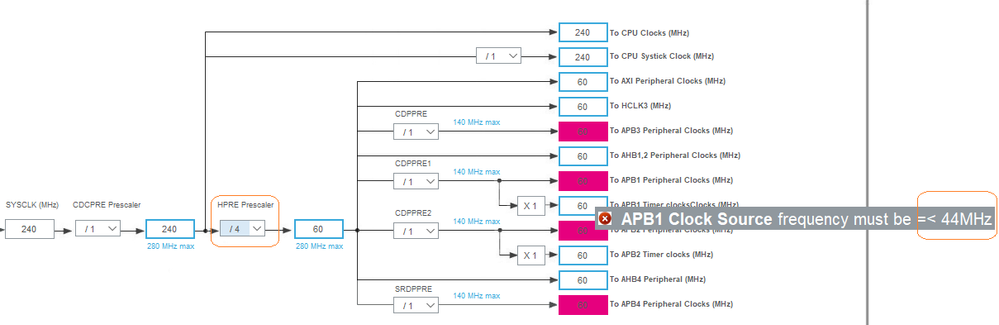

1) When changing HPRE prescaler only CubeMX unexpectedly changes timer clock limits.

I think those limits should depend on VOS voltage which, in turn, depends on SYSCLK, rather than on post-HPRE clock. As a result, lowering timers' clock lowers the max limits - see the screenshots. This does not seem to make sense.

2) Interestingly, AHB1, AHB2, APB1, APB2 and AHB4 clocks do not get the warning.

3) Setting DFSDM1&2 clocks higher than the max allowed 140MHz does not cause any warnings. It is a bit unclear what max DFSDM clock is. In Table 23 on p. 84 DS13195 specifies 140MHz while in Table 107 on p. 162 it states max fDFSDMCLK is fSYSCLK.

4) Watch out! Generated SystemClock_Config() contains this line:

HAL_PWREx_ConfigSupply(PWR_DIRECT_SMPS_SUPPLY);

CubeMX 6.2.1 now by default wants to use SMPS power supply. It seems this is a deviation from the previous version.

5) It is not a CubeMX issue but RM0455 33.4.4 (pp. 1161, 1164, 1165) incorrectly states that Manchester clock time should stay within the limits defined by SYSCLK. It should be DFSDMCLK - which may or may not equal SYSCLK.

Tested with STM32H7A3VITx and CubeMX 6.2.1

Max STM32H7A3 clock frequencies are defined in DS13195, Table 23, p. 84

- Labels:

-

STM32CubeMX

-

STM32H7 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-05 12:22 AM

Hello @TJast

Thanks for your feedback,

Could you please share your ioc file to check it?

Khouloud

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-05 04:24 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-05 10:10 AM

@Khouloud ZEMMELI , one more thought: I think it would be beneficial if CubeMX allowed to set DFSDM input clock divider separately per each channel and independently from CLKOUT. Currently, CLKOUT needs to be enabled in order to set input clock divider, which probably does not make sense.

It seems that the current design of this CubeMX part does not well resemble the underlying concept.

- Generating makefiles without STM32IDE in STM32CubeMX (MCUs)

- Placing HAL functions into ITCM RAM in STM32CubeIDE (MCUs)

- MMT not available in tools menu in STM32CubeIDE (MCUs)

- STM32L432 UART receive IRQ handler unable to created by Cube in STM32CubeMX (MCUs)

- CubeMx clock resolver chooses the wrong USB clock frequency in STM32CubeMX (MCUs)