- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Embedded software

- stm32f407 - timer10 interrupt handler called with ...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

stm32f407 - timer10 interrupt handler called with delay

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-02-12 05:00 AM

Dear ST community,

I am running stm32f4-7 with FreeRTOS, and lwip, I am running TCP server by use of LWIP and some other application logic.

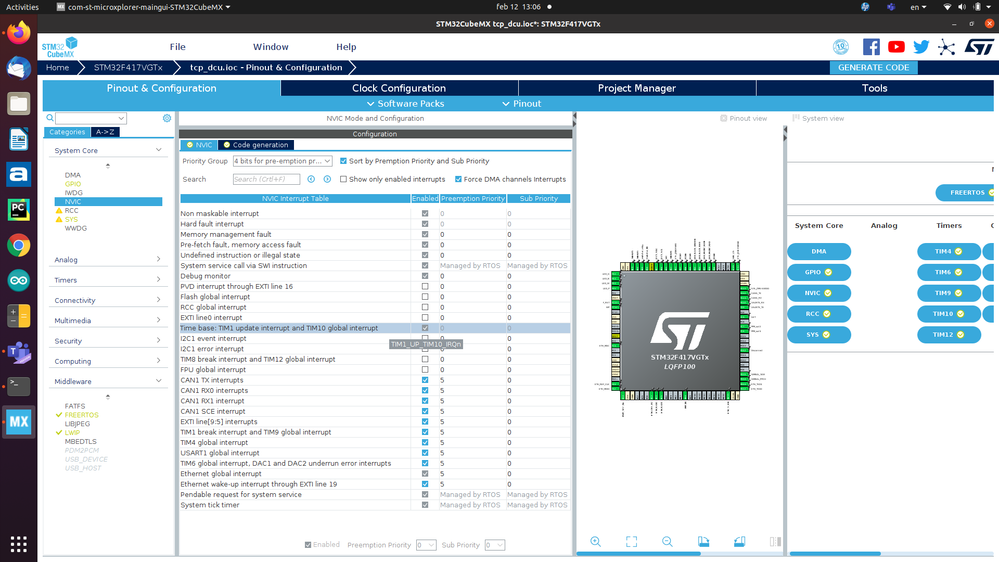

I need to generate PPM signal (8 PWM pulses with different length) every 20ms. For this purpose I am using timer10, and on each interrupt I set one GPIO pin to 1 or 0. Each PWM pulse is from 0,5ms to 1,1ms, so the timming i gues is not that fast... I am running system clock of 168MHz.

everything runs fine, just sometimes, PPM signal has some parts longer than it should be, most porbably timer interrupt is called with some delay. I suggest processor is bussy with some other task, thus cannot service interrupt for the timer. I have nested interrupts enabled with the priority for my timer = 0.

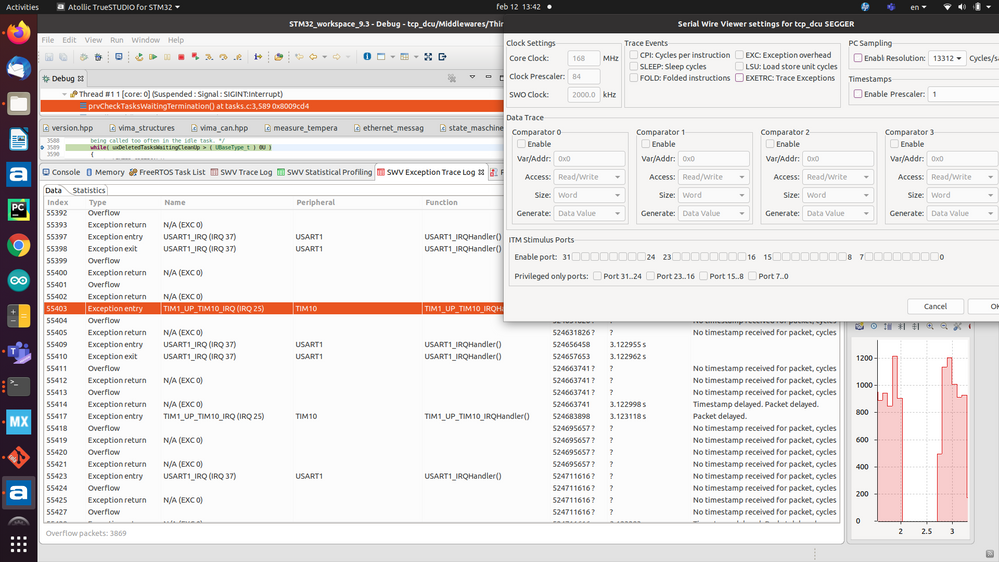

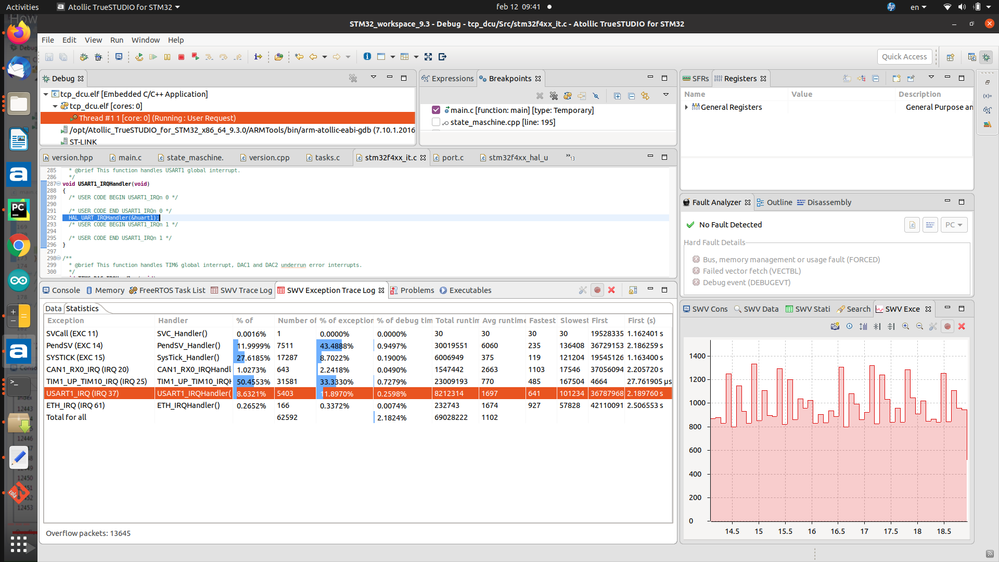

I was trying to debug this by SWV. where I can see entering and exiting of interrupts.

my question fot the SWV:

- What does the overflow means in the sequence list of exceptions?

- The message with index 55403 says I am entering TIM10 interrupt, but then I see index 55409 USART1_IRQ, however usart has lower priority than time10, so does this mean usart is preepting handling of tim10?

- index 55403 and 55417 I can see just tim10 entering, but no exit, why does it happen? most of the tiem I can see entering of tim10 interrupt and then exit of tim10 interrupt

I know RTOS has probably heigher interrupt priority then timers do, so maybe when there is a flag raised for tim10 interrupt, it cannot be handled becouse RTOS is bussy with CPU, but I am delayed with interrupt routine for timer 10 for more then 0,1ms, which I thing is too much to be delayed even if RTOS is doing something. Or is it something that is normal?

Q2: Is there some other way to generate PPM signal?

Thank You.

Peter

- Labels:

-

FreeRTOS

-

STM32F4 Series

-

TIM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-02-12 06:02 AM

I would generate the pulse train with a hardware timer (TIM) channel OC (output compare) feature combined with DMA. If you have 8 ppm channels you have 16 edges per 20 ms (?) round. Let the timer run at 1 MHz. Then you store the 16 edge-to-edge timings in the array and let the DMA be triggered by the timers OC event (not interrupt). The DMA target is th timer channels compare register for the next edge. After setup, this runs all in hardware without a single interrupt...

- PSP switches to the handler stack upon function return in STM32 MCUs Embedded software

- STM32L0 LPUART reboot in STM32 MCUs Embedded software

- External IRQ on PB15 in STM32CubeMX (MCUs)

- STM32F407 USB Device HS mode interrupt transmission jitter in STM32 MCUs products

- MDMA write error writing to DMA registers in STM32 MCUs products