- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- STM32H750 (rev.V) Needs higher ADC clock for dual ...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32H750 (rev.V) Needs higher ADC clock for dual interleaved mode when triggered from timer?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-27 11:47 PM

According to AN5354:

Page 13 / Table 12: Number of ADC = 2, resolution = 12, LQFP100, maximum ADC frequency is 35MHz (providing 70MHz from PLL2P before /2 divider)

Page 15 / Table 16: Direct 4.38 MSPS Fast 3.83 MSPS

And according to formula from RM: Tconv=(1.5+6.5)

a=35*10^6/Tconv = 4.375 [MHz]

With this settings it is possible to obtain ~ 8MHz sampling rates for ~ 35Mhz ADC clock (dual interleaved 2x4MHz, continuous conversion)

This works perfectly until I try to trigger ADC from timer with continuous conversion disabled.

For 8MHz (2 x 4MHz) sampling rate i need to provide ADC clock around ~45MHz (90MHz from PLL2P before /2 divider) for correct operation. When lower ADC clock is provided, then ADC sampling rate is reduced by 1/1.5, 1/2, etc. factor.

Why ADC clock must be higher when sampling rate is set by timer trigger events?

Solved! Go to Solution.

- Labels:

-

ADC

-

STM32H7 Series

-

TIM

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-02-04 11:37 PM

Hello @Georgy Moshkin ,

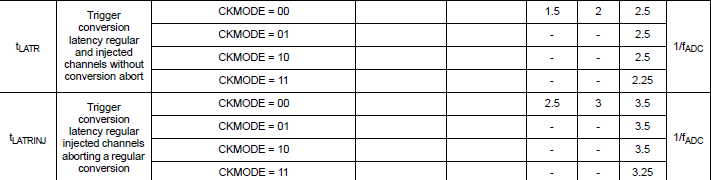

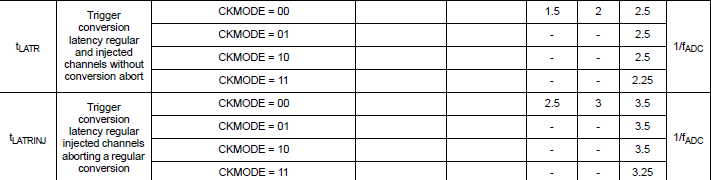

When the ADC is triggered by a timer there is an extra latency before ADC will start conversions.

This latency is defined in the STM32H7 datasheet (Table of ADC characteristics) and this could explain the behaviour that you see.

By the way the dual interleaved is for max perf and is used in continuous mode.

I would suggest that you add more details to your post, specifically about your use case.

Imen

Thanks

Imen

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-02-04 11:37 PM

Hello @Georgy Moshkin ,

When the ADC is triggered by a timer there is an extra latency before ADC will start conversions.

This latency is defined in the STM32H7 datasheet (Table of ADC characteristics) and this could explain the behaviour that you see.

By the way the dual interleaved is for max perf and is used in continuous mode.

I would suggest that you add more details to your post, specifically about your use case.

Imen

Thanks

Imen

- STM32F407VE sampling signal with ADC. in STM32 MCUs products

- STM32H725 problems with ADC IRQ handler in regular simultaneos mode in STM32CubeIDE (MCUs)

- STM32H750 RTC wakeup timer not periodically triggered in STM32 MCUs Embedded software

- STM32H750: STOP mode working on revision Y, not on revision V but normal application working normally. What causes this problem? in STM32 MCUs products

- STM32H747 DMA Linked List (or Double Buffering) and ADC Interleaved in STM32 MCUs products