- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- Nucleo-g431kb TIM2 Output Compare DMA - When does ...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Nucleo-g431kb TIM2 Output Compare DMA - When does the dma shift actually trigger?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-21 12:42 AM

Hi!

A question related to the 32 bit TIM2 (or timers in general).

I am generating a square wave output using TIM2 Output Compare function with toggle mode.

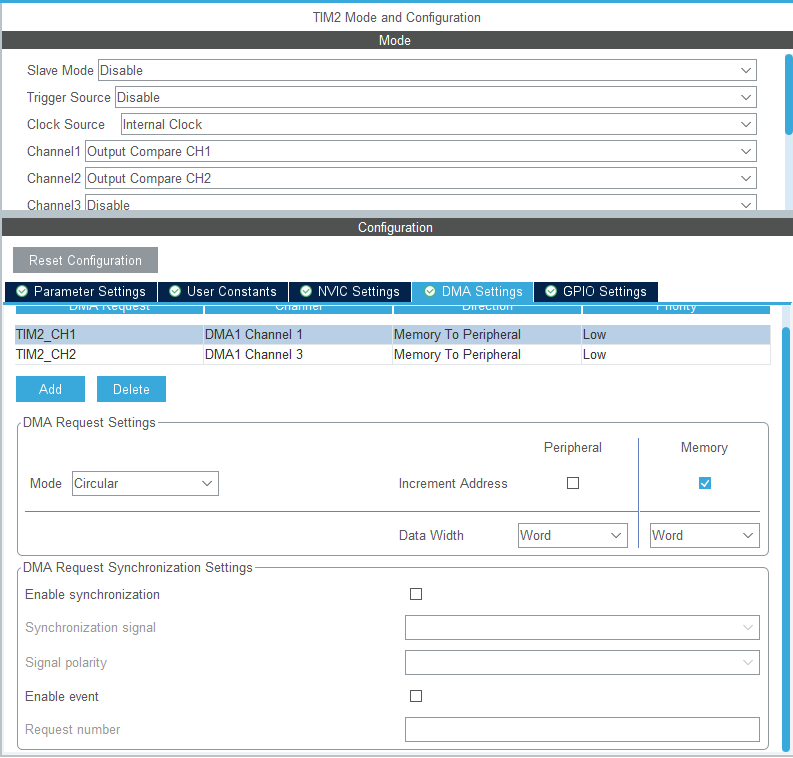

I have also configured the DMA to help switch the CCRx output compare value in order to go from low to high, and high to low again within a each timer period. At least that is want I want to achieve.

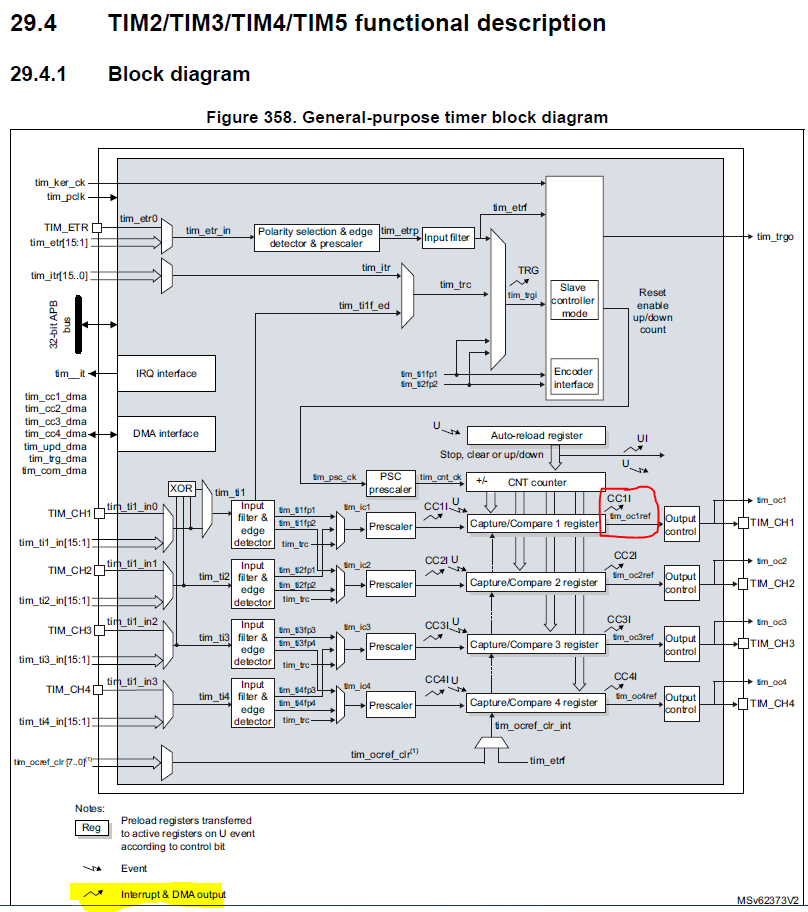

However, the DMA seems to be triggered at when each timer period is finished and not when each compare has happened. Should it not do this?

According to the STM32G4 reference manual, it look like the DMA request should happen after a compare as I expect but not how it is happening?

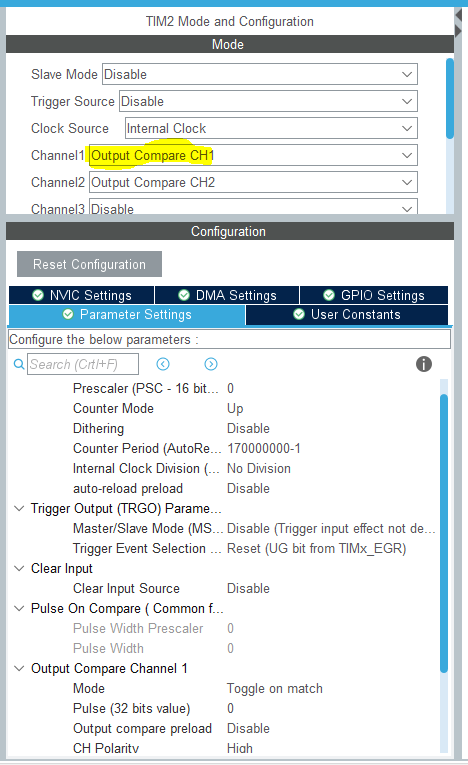

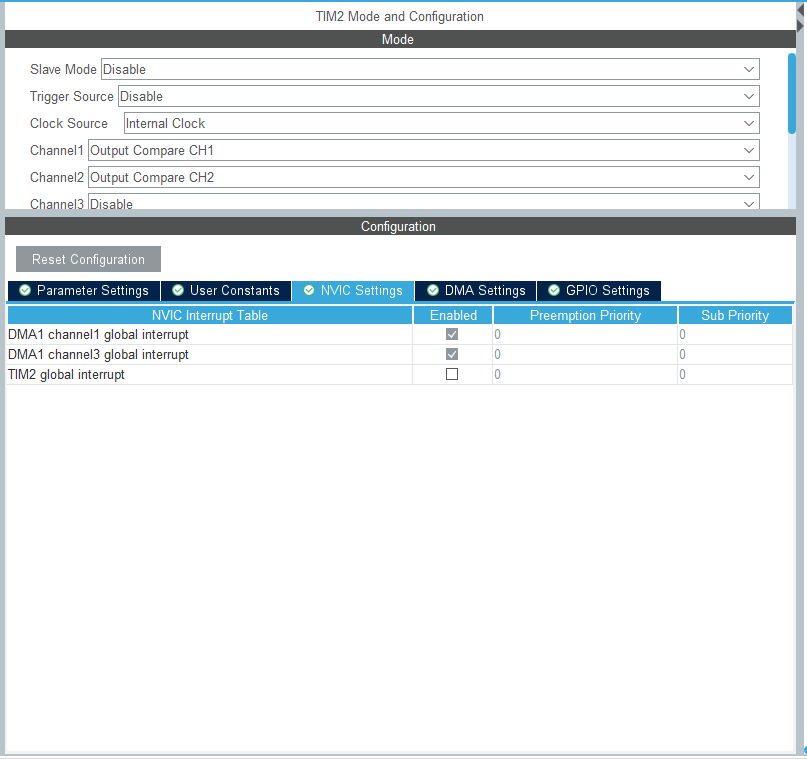

My timer CUBEMX configuration is as following. The system clock is set maximum 170MHz. Prescale set 0, period is set 170000000-1, so I expect the square puls to be generate 1 time per second. Instead it is generate everyother second.

#define MOTOR_DMA_OC_HIGH 0

#define MOTOR_DMA_OC_LOW 10

static uint32_t m1_tim2_dma_buffer[2] = {MOTOR_DMA_OC_HIGH, MOTOR_DMA_OC_LOW};

void motor_m1_enable(void)

{

HAL_TIM_OC_Start_DMA(&htim2, TIM_CHANNEL_1, m1_tim2_dma_buffer, 2);

}Any inputs from you guys is much appreciated 😊

Solved! Go to Solution.

- Labels:

-

DMA

-

STM32G4 Series

-

TIM

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-21 01:05 PM

I'm not sure DMA will succeed loading the new CCR value within 10 system clocks.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-21 12:56 AM

You set the mode "toggle on match". So, every second the signal is toggled --> 0.5 Hz.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-21 12:27 PM

Hi @KnarfB , thanks for the input.

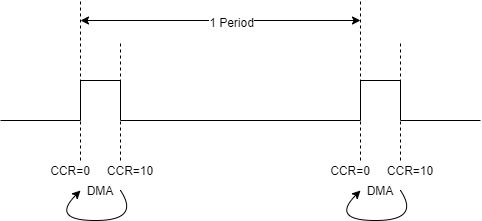

So, if the DMA toggles the CCR1 value on every match, I should se a square wave with a 1Hz period on the output as illustrated below:

This seems not to be the case. I have connected my output TIM2 CH1 pin to TIM3 Ext input where I measure each rising edge. This is updating at approx the double -> 0.5Hz. I am actually not clocking TIM3 since I am using it as "external clock source", so I am just estimating the update frequency of the counter. I could change it to Input Capture and measure.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-21 01:05 PM

I'm not sure DMA will succeed loading the new CCR value within 10 system clocks.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-21 01:42 PM

@Community member thanks for the input!

My thoughts were actually on it too. So I have been reading about DMA latency in AN2548 Application Note Using the STM32F0/F1/F3/Gx/Lx Series DMA controller where it does hint towards me maybe pushing the limit a little 🙂

I dont have any particual constraint saying my high must be max 10 cycles. I will try to increase a lot and test more.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-21 02:20 PM

It works for larger values and differences of HIGH and LO. Depending on what you want to achieve, couldn't you substantially lower the counter period (and increase the pre-scaler accordingly)? For a counter period of 100 you can set HI and LO in steps of 1%, or take a period of 1000 ...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-24 12:11 PM

@KnarfB I would like to keep the prescaler 0 (or as close to as possible) in order to increase the output frequency resolution. My code is going to control a stepper motor, hence the reason for adjusting the ARR value on the go.

Increasing the difference between the two CRR values did the job for me and it seems to be working as expected now.

- STM32F412 CAN Transmits unexpected data in STM32 MCUs products

- LoRa RX timeout triggers immediately in non-continuous receive mode in STM32 MCUs Wireless

- Trigger from Timer does not trigger injected conversion on ADC in STM32 MCUs products

- LPBAM I2C data buffer using NUCLEO-U575ZI-Q in STM32 MCUs products

- STM32H7 : Using the DMA to transfer burst of Can-Bus data in STM32 MCUs products