- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- STM32 won't start without physical reset.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32 won't start without physical reset.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-06 06:24 AM

Hi,

My mcu is STM32L476RGTx and I experiencing very strange behaviors to make my cpu start.

This mcu is on pcb I designed myself.

My boot0 pin is shorted to GND

And the reset pin pulled up to VCC.

I can program my chip with my st link (updated to the last version) an after each programming my chip is starting up as expected.

But as soon as I tried to make it boot from cold start it won't start. I have to manually press reset button and after that, it run as expected.

It append what ever i use as supply. 3V3 from programmer, 3V3 from local switching supply (LM43602)...

For the moment i do not use the 8mhz quartz on board.

Have you any idea I did not check yet or they're is any parameter that could prevent my mcu to run my program from flash but make it run as soon as I create a true reset event ?

Maybe is it BOD ? But how could I check that ?

anyway, Thanks for your help.

Solved! Go to Solution.

- Labels:

-

RESET

-

STM32L4 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-11 02:13 AM

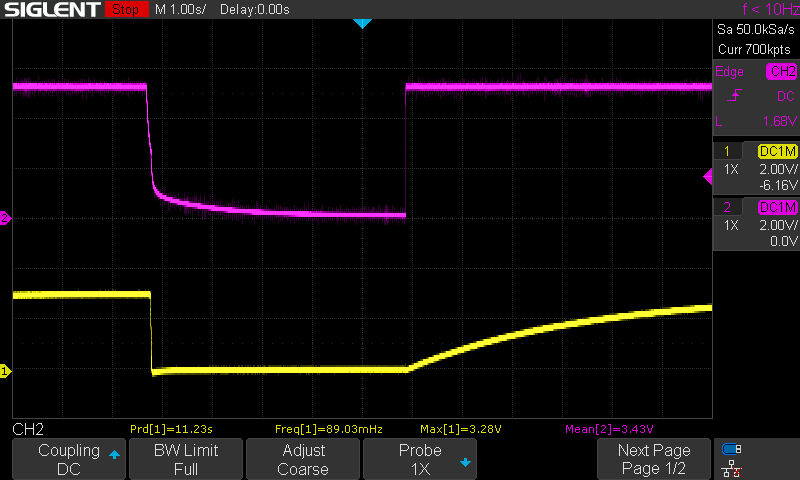

I put a 100uF capacitor between NRST and GND. Take 5 sc to charge. And boot fine with that !

(take care to the base time on the image below. Screen width take 14sc).

Same connection as previous. Top is VSS and bottom is NRST

So i'll let it like that.

That was my 100nF capacitor (between NRST and GND) which is the faulty one. Was here to protect RESET button and debonce NRST signal. But seems too big.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-06 06:56 AM

It could be that it's just stuck during startup somewhere. Maybe HSE failed to initialize in time or similar. Attach a debugger when it's in the stuck state to see where it is.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-06 11:21 PM

Hi, first thanks for your reply.

So, installed openOCD, and running under command line. Worked fine, connected to target and telnet cmd prompt.

> stm32l4x.cpu curstate

runningEvent if my debug LED on my board is still off.

(For this very simple debug, the first action in my code is to change my led state to on. Witch is perfectly working after hardware reset)

I have to halt my device to get core dump. There it is :

> halt

target halted due to debug-request, current mode: Thread

xPSR: 0x61000000 pc: 0x1fff4956 msp: 0x200030a8

> reg

===== arm v7m registers

(0) r0 (/32): 0x48000000

(1) r1 (/32): 0x00000000

(2) r2 (/32): 0x00010100

(3) r3 (/32): 0x50000b00

(4) r4 (/32): 0x200007d8

(5) r5 (/32): 0x48000400

(6) r6 (/32): 0x40021040

(7) r7 (/32): 0x48000000

(8) r8 (/32): 0x48000800

(9) r9 (/32): 0xe000e010

(10) r10 (/32): 0x40013000

(11) r11 (/32): 0x40003800

(12) r12 (/32): 0x00000000

(13) sp (/32): 0x200030a8

(14) lr (/32): 0x1fff4947

(15) pc (/32): 0x1fff4956

(16) xPSR (/32): 0x61000000

(17) msp (/32): 0x200030a8

(18) psp (/32): 0x00000000

(20) primask (/1): 0x00

(21) basepri (/8): 0x00

(22) faultmask (/1): 0x00

(23) control (/3): 0x04

(24) d0 (/64): 0x0000000000000000

(25) d1 (/64): 0x0000000000000000

(26) d2 (/64): 0x0000000000000000

(27) d3 (/64): 0x0000000000000000

(28) d4 (/64): 0x0000000000000000

(29) d5 (/64): 0x0000000000000000

(30) d6 (/64): 0x0000000000000000

(31) d7 (/64): 0x0000000000000000

(32) d8 (/64): 0x0000000000000000

(33) d9 (/64): 0x0000000000000000

(34) d10 (/64): 0x0000000000000000

(35) d11 (/64): 0x0000000000000000

(36) d12 (/64): 0x0000000000000000

(37) d13 (/64): 0x0000000000000000

(38) d14 (/64): 0x0000000000000000

(39) d15 (/64): 0x0000000000000000

(40) fpscr (/32): 0x02000000

===== Cortex-M DWT registersafter a reset run command the I can get my software work. So I halted after that and get core dump. Here you can see:

> reset run

Unable to match requested speed 500 kHz, using 480 kHz

Unable to match requested speed 500 kHz, using 480 kHz

> halt

target halted due to debug-request, current mode: Thread

xPSR: 0x01000000 pc: 0x08002cae msp: 0x20017fc8

> reg

===== arm v7m registers

(0) r0 (/32): 0x48000400

(1) r1 (/32): 0x00000400

(2) r2 (/32): 0x00040000

(3) r3 (/32): 0x48000400

(4) r4 (/32): 0x00000000

(5) r5 (/32): 0x00000000

(6) r6 (/32): 0x00000000

(7) r7 (/32): 0x20017fc8

(8) r8 (/32): 0x00000000

(9) r9 (/32): 0x00000000

(10) r10 (/32): 0x00000000

(11) r11 (/32): 0x00000000

(12) r12 (/32): 0x00000000

(13) sp (/32): 0x20017fc8

(14) lr (/32): 0x08000f3d

(15) pc (/32): 0x08002cae

(16) xPSR (/32): 0x01000000

(17) msp (/32): 0x20017fc8

(18) psp (/32): 0x00000000

(20) primask (/1): 0x01

(21) basepri (/8): 0x00

(22) faultmask (/1): 0x00

(23) control (/3): 0x00

(24) d0 (/64): 0x0000000000000000

(25) d1 (/64): 0x0000000000000000

(26) d2 (/64): 0x0000000000000000

(27) d3 (/64): 0x0000000000000000

(28) d4 (/64): 0x0000000000000000

(29) d5 (/64): 0x0000000000000000

(30) d6 (/64): 0x0000000000000000

(31) d7 (/64): 0x0000000000000000

(32) d8 (/64): 0x0000000000000000

(33) d9 (/64): 0x0000000000000000

(34) d10 (/64): 0x0000000000000000

(35) d11 (/64): 0x0000000000000000

(36) d12 (/64): 0x0000000000000000

(37) d13 (/64): 0x0000000000000000

(38) d14 (/64): 0x0000000000000000

(39) d15 (/64): 0x0000000000000000

(40) fpscr (/32): 0x00000000

===== Cortex-M DWT registers- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-07 03:56 AM

> (15) pc (/32): 0x1fff4956

That's in the bootloader.

Consult AN2606 and chapter Boot configuration in RM. They are slightly contradictory.

BFB2 bit in the user option bytes is set how?

> My boot0 pin is shorted to GND

Double-check, measuring directly on the physical pin coming out of the package.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-07 04:23 AM

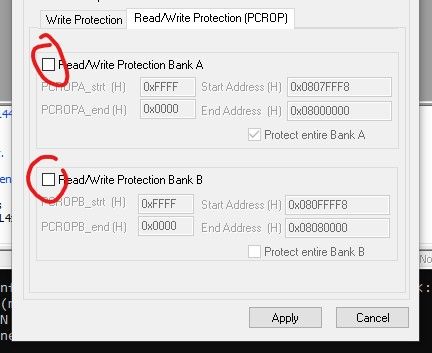

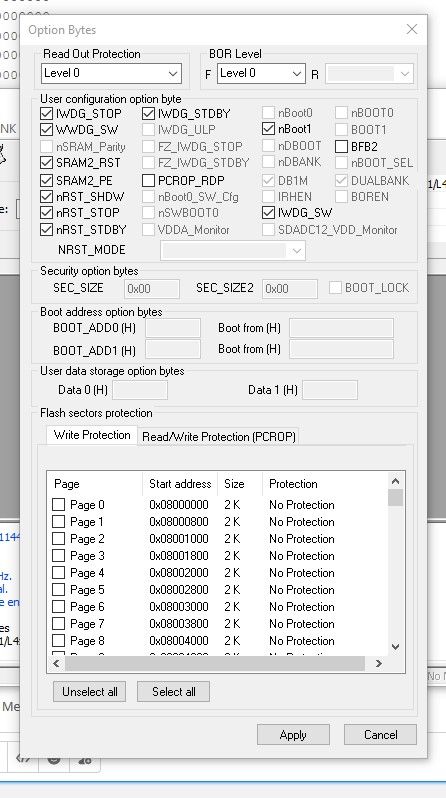

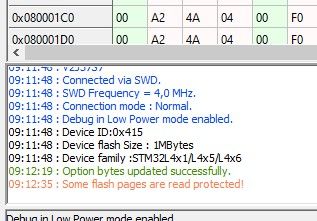

BFB2 is LOW (see picture).

And double checked, BOOT0 is shorted to GND. Measured value : 0V from GND and -3.3V FROM VCC. (is not floating)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-07 02:56 PM

This IMO looks good.

I assume your code is absolute minimal (no system init or library calls, just the usual C memory clear in the startup, and only the LED blinking with loopdelay in main()).

You can try to disconnect your power source an use an external one, to see if it makes any difference. You can try other BOD levels.

Other than that, I am out of ideas, sorry.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-07 10:38 PM

First, thanks anyway for your idea. I'll find, it's just a matter of time.

For the moment i'm checking basics. But soon, i'll be run out of it...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-08 12:10 AM

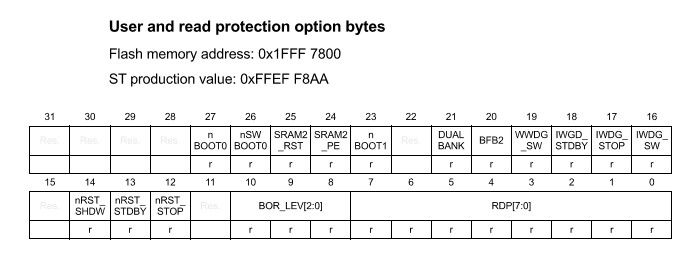

Probably nothing to do mith my issue but is it normal that I can't program to the factory reset this option byte ?

> stm32l4x.cpu mdw 0x1FFF7800

0x1fff7800: ffbff8aa

> stm32l4x.cpu mww 0x1FFF7800 0xFFEFF8AA

> stm32l4x.cpu mdw 0x1FFF7800

0x1fff7800: ffbff8aa

But this seems normal, cause in the ST-LINK utility windows, some option are grayed. (DUALBANK ?)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-08 12:20 AM

And mutliples times I get the BANK A and BANK B locked (even, if i never wanted to, and never check that option). So I had to set PCROP_RDP bit to 1 and switch security level from 0 to 1 to zero again... as explained in error message.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-08 11:36 AM

ffbff8aa

That's BFB2 set, isn't it?

Is your connection from STLink to target short (up to 15cm) and, if using a flat cable, with ground in between the signal lines?

JW

- Optimization causes "No open pipes!" in STM32 MCUs products

- G431RBT6 - Interfacing timer and compare output timer have rather fluctuation timings in STM32 MCUs products

- STM32F103CBT6 not recognized USB device in STM32 MCUs products

- RTC integrity check in STM32 MCUs products

- STM32F405 Can not connect to target in STM32 MCUs products