- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- How to control STM32H7 QSPI Chip Select?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How to control STM32H7 QSPI Chip Select?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-12-09 11:27 PM

Hi,

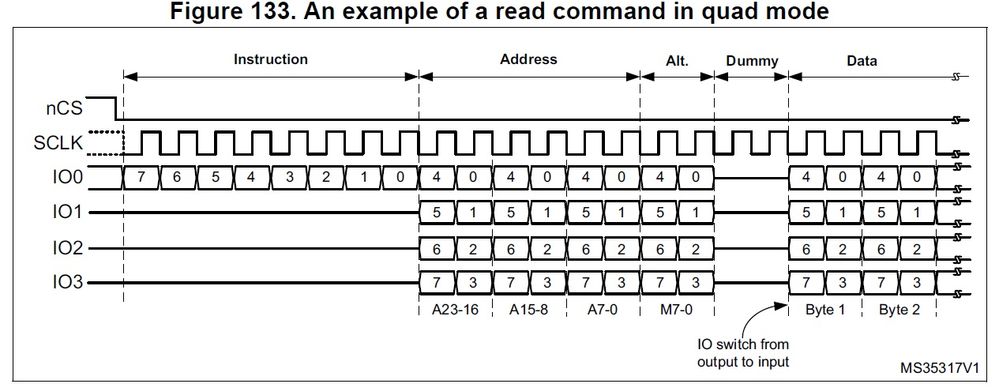

I am working on interfacing IS25LP128 128Mbit QSPI Flash with STM32H743 Nucleo board. I am running into problem with how the QSPI controller is driving the NCS line. The flash requires that the chip select remains low between command and data read/write operations. But the way QSPI HAL APIs are provided, it required two different calls. First to set command, and second to transmit or receive data.

The problem is that the QSPI controller drives NCS high between these call, and the flash reject the transaction. Is is something I am missing in using the QSPI HAL driver? Has anyone found any solution for this?

QSPI Initialization

static void MX_QUADSPI_Init(void)

{

/* USER CODE BEGIN QUADSPI_Init 0 */

/* USER CODE END QUADSPI_Init 0 */

/* USER CODE BEGIN QUADSPI_Init 1 */

/* USER CODE END QUADSPI_Init 1 */

/* QUADSPI parameter configuration*/

hqspi.Instance = QUADSPI;

hqspi.Init.ClockPrescaler = 50;

hqspi.Init.FifoThreshold = 4;

hqspi.Init.SampleShifting = QSPI_SAMPLE_SHIFTING_NONE;

hqspi.Init.FlashSize = 22;

hqspi.Init.ChipSelectHighTime = QSPI_CS_HIGH_TIME_1_CYCLE;

hqspi.Init.ClockMode = QSPI_CLOCK_MODE_0;

hqspi.Init.FlashID = QSPI_FLASH_ID_1;

hqspi.Init.DualFlash = QSPI_DUALFLASH_DISABLE;

if (HAL_QSPI_Init(&hqspi) != HAL_OK)

{

Error_Handler();

}

/* USER CODE BEGIN QUADSPI_Init 2 */

/* USER CODE END QUADSPI_Init 2 */

}

Flash Register Read Routine

{

int retStatus = -1;

QSPI_CommandTypeDef rdRegCommand;

memset(&rdRegCommand, 0, sizeof(rdRegCommand));

/* Prepare QPSI Command */

rdRegCommand.InstructionMode = QSPI_INSTRUCTION_4_LINES;

rdRegCommand.Instruction = pCmdInfo->cmd;

rdRegCommand.AddressMode = QSPI_ADDRESS_NONE;

rdRegCommand.AlternateByteMode = QSPI_ALTERNATE_BYTES_NONE;

rdRegCommand.DataMode = QSPI_DATA_4_LINES;

rdRegCommand.DummyCycles = pCmdInfo->dummy;

rdRegCommand.DdrMode = QSPI_DDR_MODE_DISABLE;

rdRegCommand.SIOOMode = QSPI_SIOO_INST_EVERY_CMD;

rdRegCommand.NbData = pCmdInfo->size;

/* Send EFD Read Register Command to QPSI Line */

if(HAL_OK == HAL_QSPI_Command(phqspi, &rdRegCommand, HAL_QPSI_TIMEOUT_DEFAULT_VALUE))

{

/* At this point, the NCS goes high */

/* Receive EFD Read Register data from QSPI Line */

if(HAL_OK == HAL_QSPI_Receive(phqspi, pdata, HAL_QPSI_TIMEOUT_DEFAULT_VALUE))

retStatus = 0;

}

return retStatus;

}

Solved! Go to Solution.

- Labels:

-

QSPI

-

STM32H7 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-17 08:38 PM

Turns out it was an understanding error on our part. The CS is driven absolutely fine by the QSPI controller.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-12-11 09:09 AM

Hello @Joyabb ,

Welcome to the STM32 Community 😊

Could you please share your screenshot of output command signals that you see in the oscilloscope ? and what is really the command you send?

Imen

Thanks

Imen

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-12-11 10:15 AM

Pretty sure it's not supposed to go high normally between the phases.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-01-17 08:38 PM

Turns out it was an understanding error on our part. The CS is driven absolutely fine by the QSPI controller.

- SPI NSS/CS when working with registers and DMA in STM32 MCUs products

- How to interface STM32H750xB with ST-Link/V2 debugger in STM32CubeIDE (MCUs)

- STlink-V3Set Low Voltage Error; Failed on OpenOCD init in STM32 MCUs products

- Interfacing with memory mapped device (i.e. FPGA) on STM32F7 FMC bus in STM32 MCUs products

- High current consumption in Stop Mode on STM32U575 DEV Kit and Custom Board in STM32 MCUs products