- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- STM32F7 QSPI wrong read data

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F7 QSPI wrong read data

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-20 02:28 AM

Hello!

I am going to use stm32f722vc MCU and QSPI in my design. Before designing PCB I research QSPI on available hardware: board with stm32f722vc MCU installed and all GPIOs available on headers. I am trying to execute indirect read mode to fetch GPIOs states, as memory chip is not available by now.

Test code is

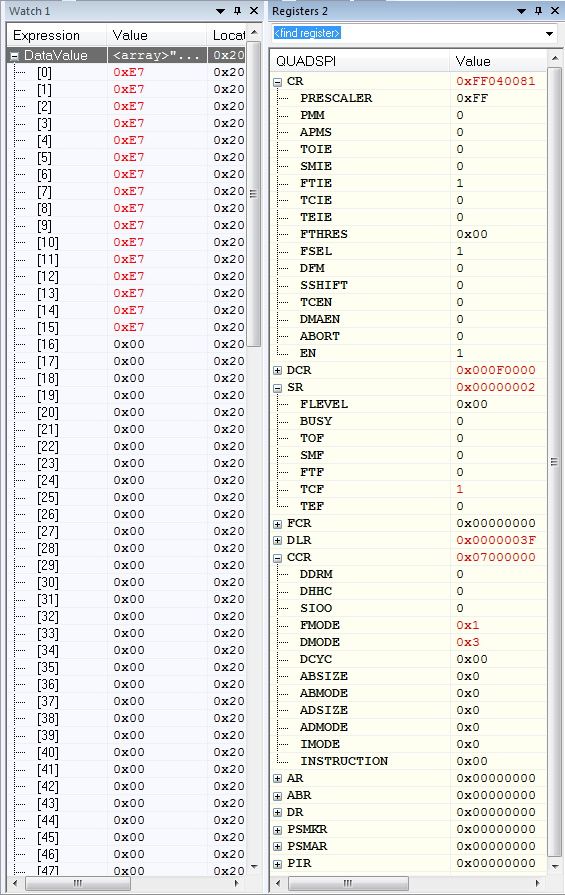

QUADSPI->CR = (255 << QUADSPI_CR_PRESCALER_Pos) | (0x00UL << QUADSPI_CR_FTHRES_Pos) | QUADSPI_CR_FSEL | QUADSPI_CR_EN;

QUADSPI->DLR = 63;

QUADSPI->DCR = 15 << QUADSPI_DCR_FSIZE_Pos;

QUADSPI->CCR = QUADSPI_CCR_FMODE_0 | QUADSPI_CCR_DMODE_0 | QUADSPI_CCR_DMODE_1;

QUADSPI->CR |= QUADSPI_CR_FTIE;

//interrupt handler

void QUADSPI_IRQHandler(void)

{

DataValue[DataCnt] = *((__IO uint8_t *)&(QUADSPI->DR));

DataCnt++;

}

So with code above I expect QSPI will read 64 bytes of states of it's 4 data lines. But the result is completely different. QSPI always reads a quater of QUADSPI->DLR value, that is 16 bytes instead of 64 regardless off data lines count used (DMODE bits). And the data QSPI fetches is completely not the lines states. I get only 0xE7 data bytes regardless of actual lines states (all lines coonected to GND or all lines connected to 3V3) and data lines count used (DMODE bits). Also FIFO settings do not effect data bytes. But transfer itself seems to be executed without errors, transfer complete flag arises, busy flag is cleared (picture attached).

What am I doing wrong, missing something?

Please, help me understand QSPI logic: FIFO, DLR, indirect read mode with only data phase (when DCYC = 0; ABMODE = 0; ADMODE = 0; IMODE = 0).

Thanks.

- Labels:

-

QSPI

-

STM32F7 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-26 09:00 AM

Hi @EvgenS Po ,

You said "I have read documents about QSPI, but have not found the answers"

==> Did you checked AN4760 (Quad-SPI interface on STM32 microcontrollers and microprocessors).

-Amel

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-26 01:49 PM

Hello @Amel NASRI (ST Employee)

Thank you for reply, I have read this one too.

Finally I managed to get QSPI reading data as it should, but only for the first bank, when FSEL = 0.

It is found out that I am faced with the very same situation described here https://community.st.com/s/question/0D50X00009XkWnQ/quadspi-read-with-data-only-phase-indirect-mode

Actually, as you answered in that thread, "QuadSPI could not be configured with only data phase activated in indirect read mode". Although that discussion and your answer regarded to STM32H7x3, it is found out that stm32f722vc has the very same limitation.

STM32F72xxx STM32F73xxx Errata sheet does not mention this limitation but in practice indirect read mode with only data phase activated does not work for stm32f722vc. The workaround you suggested (to enable the dummy phase with at least 2 dummy cycles) resolves the situation.

Please confirm or refute impossibility to use QSPI in indirect read mode with only data phase activated in stm32f722vc.

Best regards,

EvgenS Po

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-02-18 06:00 AM

Hi @EvgenS Po ,

Sorry to ome back late to this discussion. I want to confirm that the same limitation about indirect mode usage for STM32H7 is applicable in the case of STM32F7 as well.

There will be an update of the errata sheet to include this limitation and it is thanks to your contribution that we trigger it.

Even if the confirmation is late, but it can be helpful for other users facing a similar issue.

-Amel

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.