- STMicroelectronics Community

- Automotive & Transportation

- Microcontrollers

- SPC560D CAN baudrate confirmation

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

SPC560D CAN baudrate confirmation

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-14 05:55 PM

Hello all,

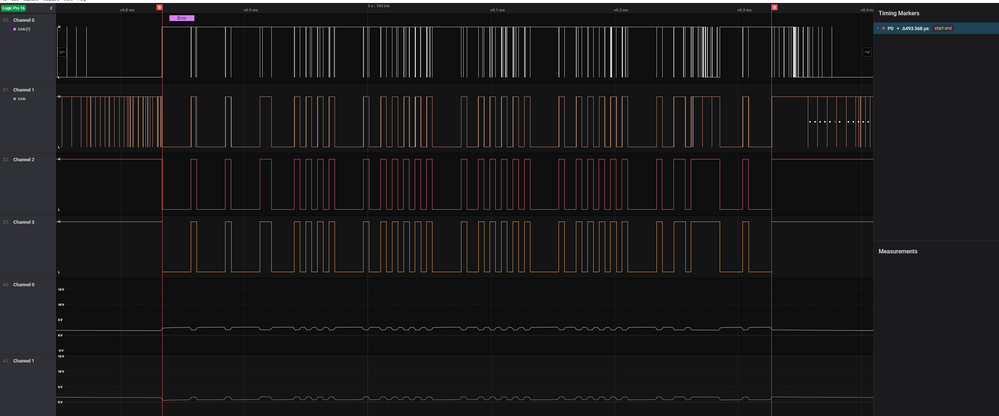

im working on a project that uses an SBC, using my logic analyser i can confirm data is coming and and looks to be a can signal but it seems my baud rate timing is incorrect or something else is amiss.

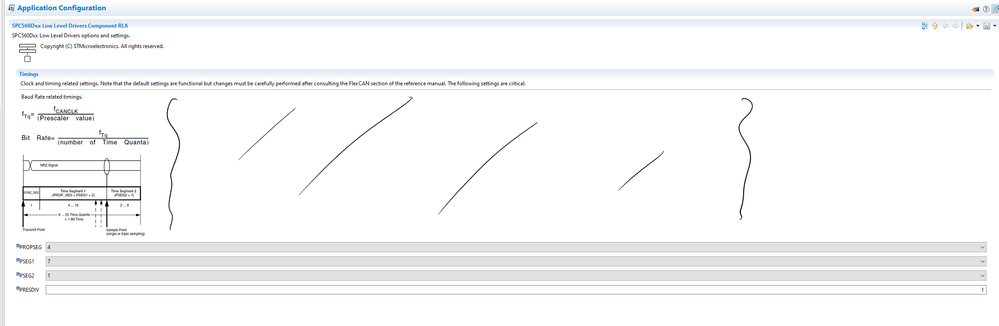

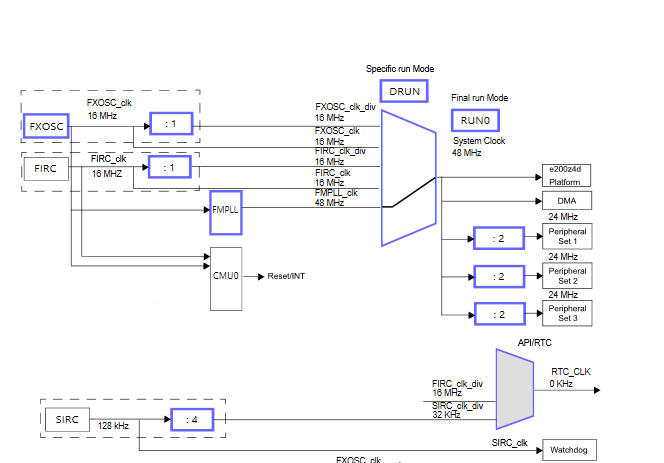

my board is the SPC560DL1, i understand the the flexcan uses Perphial set 2 clock so mine by default is set to 24Mhz.

http://www.bittiming.can-wiki.info/#Freescale

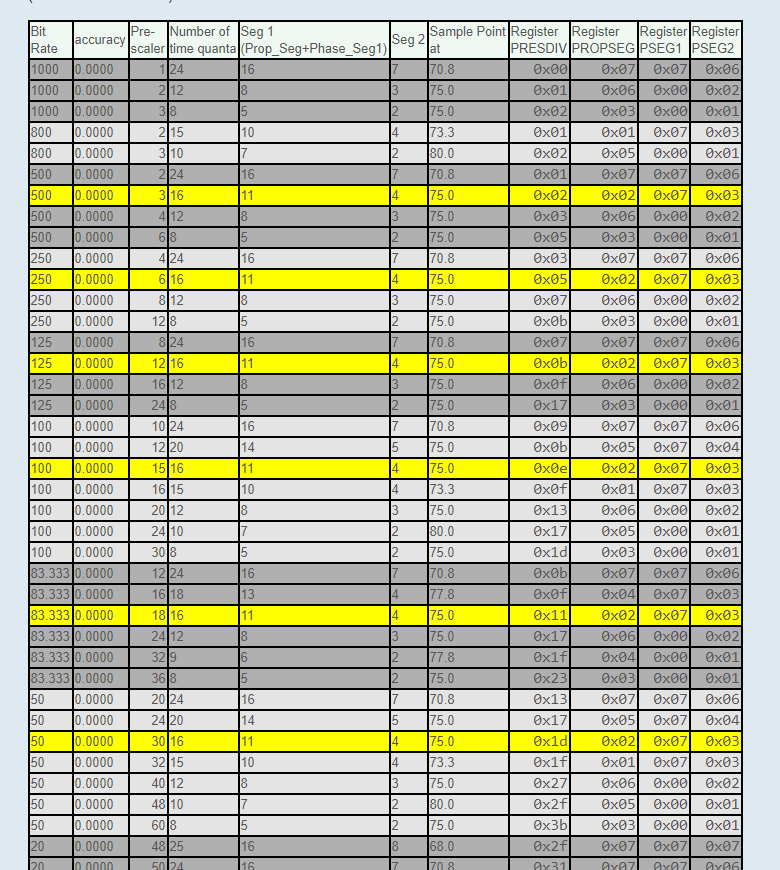

here is the table i've created with < 24Mhz, 75% sample point >

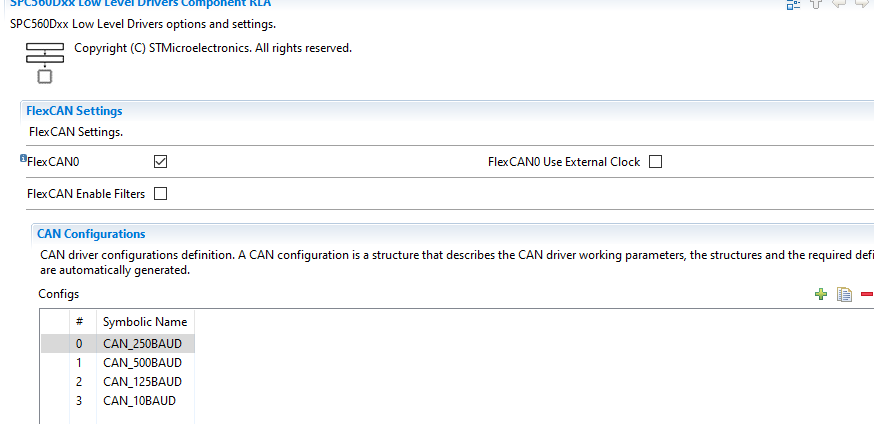

my settings for 250 are

sample point @ 75%, i've also tried 87.5

Pclk 24Mhz

propseg= 2

pseg1 =7

pseg2 =3

presdiv =6

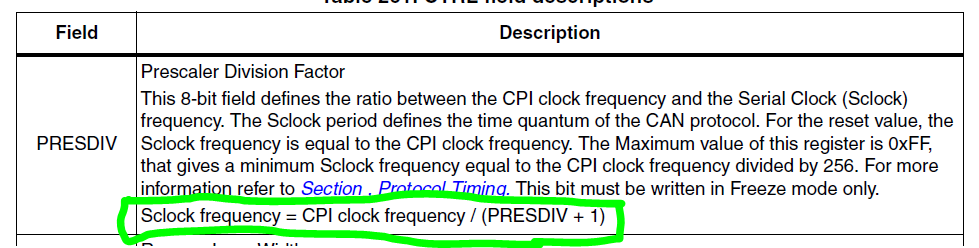

which should solve to 24,000,000/6 = 4000000

4000000/16 = 250 baud

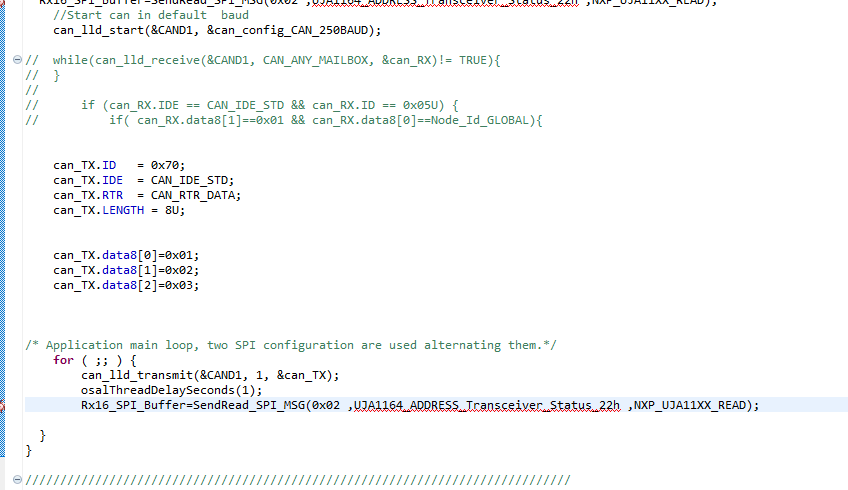

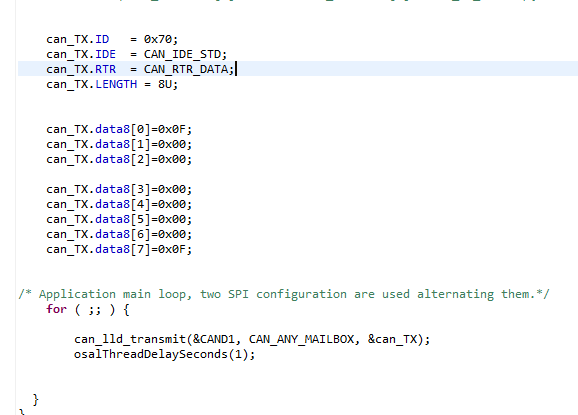

Here is my code snippit that i'm using to test can functionality

Solved! Go to Solution.

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-11-19 01:00 AM

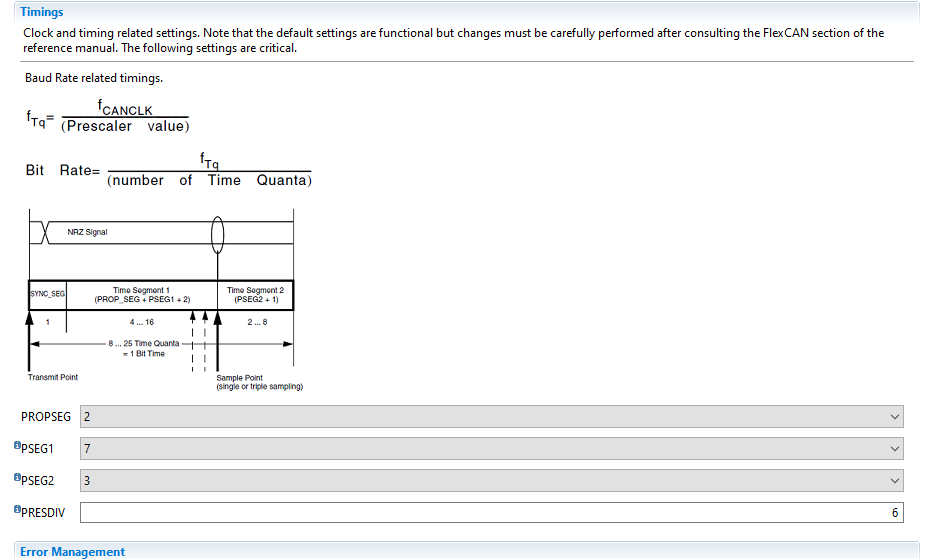

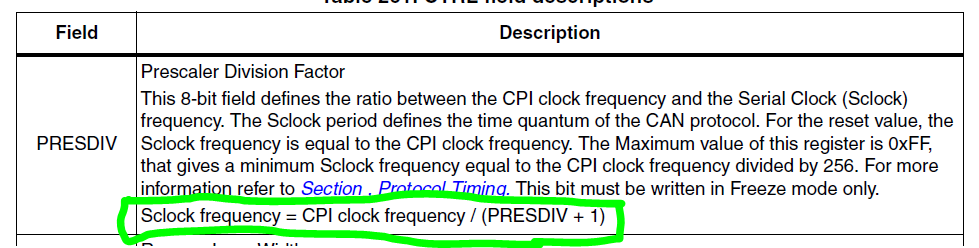

the issue is in your configuration.

the formula to calculate the clock is:

PCLK / (PRESDIV + 1)

So, in your configuration PRESDIV has to be set to 5 (and not to 6)

Regards,

Giuseppe

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-16 01:38 AM

Hello ,

According to your settings ,

the bitrate should be 250 Kbit/s

I do not see any timing or scale in your screenshot ...

Best regards

Erwan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-18 04:11 PM

Hey Erwan,

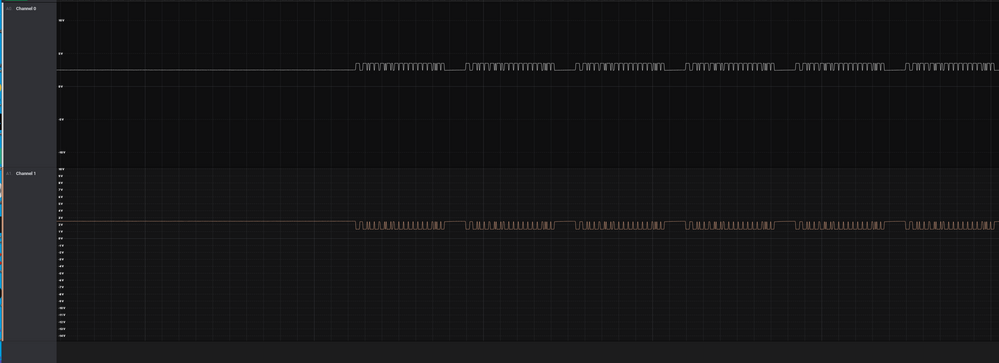

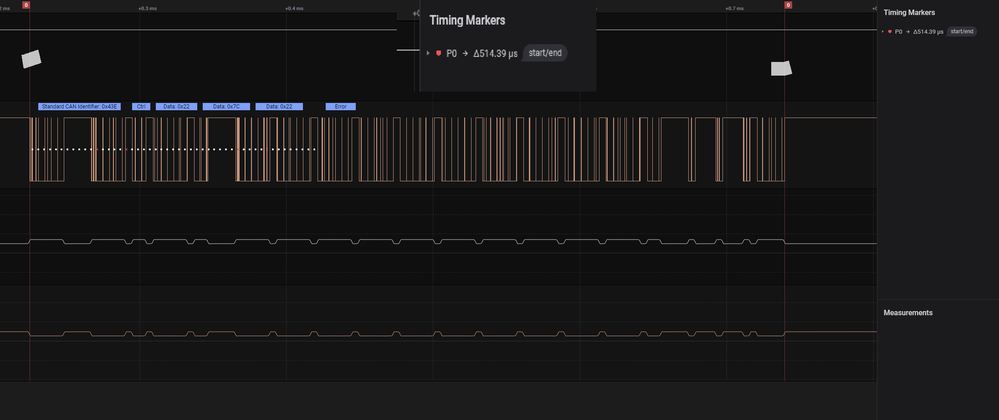

here is an attached image, the data constantly changes along with everything else but here is one that had more data than the rest and with a timing marker as well.

Setup:

8 bytes of data where the message is 0F 00 00 00 00 00 00 0F

I've also attached the file with the entire can recording ( program is logic 2 from salaeae) , also added in the timing for the start and end.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-18 04:16 PM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

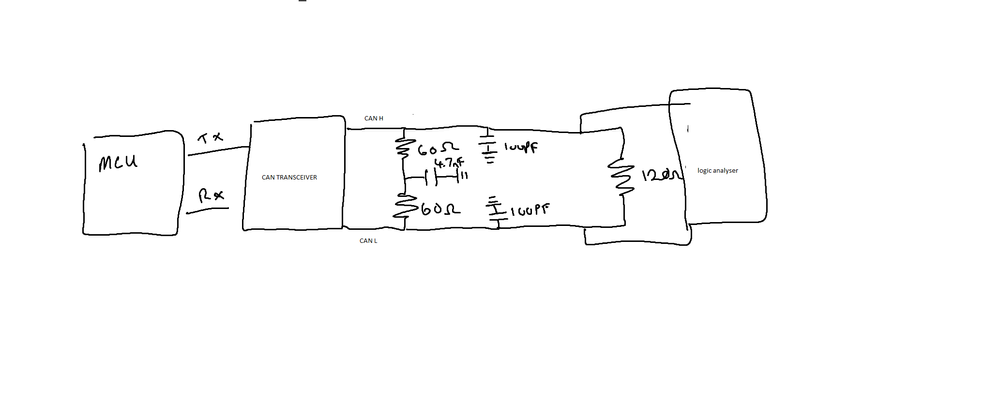

2020-10-18 04:54 PM

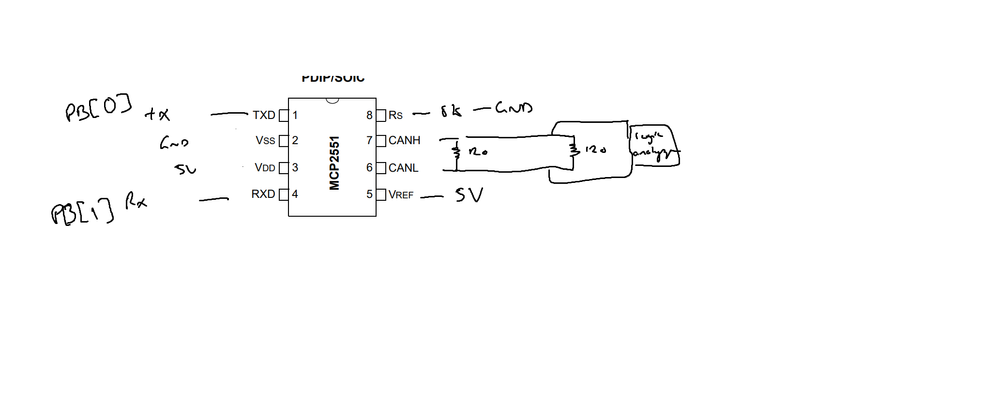

Here is also a setup using the mcp2551 with just 2 120 ohm resistors at each end

the data in this message should be different to the prior as this is on my spc560d-dis board

channel 2 and 3 are connected to TX and RX

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-20 07:58 PM

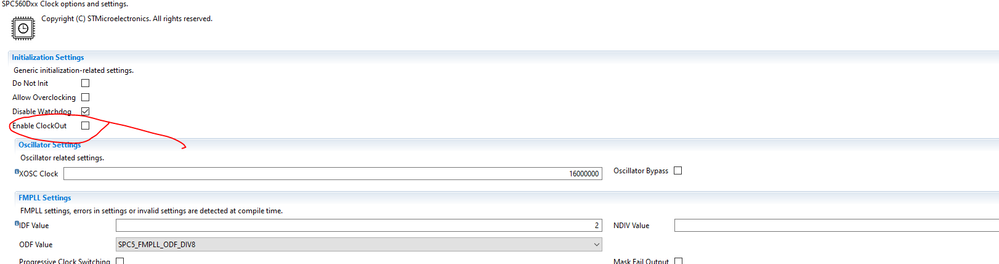

Hey Erwan, i found out that beyond 20kbps the can signal becomes unstable.

i was told that i should be using the external clock to which i've tried enabling but when i do it results in a system reset.

is there a process to enabling the external clock ?

these also some boxes like enable clockout that i dont quite understand what it exactly does.

a guess would be that you would need to tick it along with the bypass clock but in doing that i still get an unexpected reset.

on my board i have the the CSTNE16M0V53C000R0 (16Mhz) which is advertised to be an alternative to the one used in the spc560d disc board.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-11-19 01:00 AM

the issue is in your configuration.

the formula to calculate the clock is:

PCLK / (PRESDIV + 1)

So, in your configuration PRESDIV has to be set to 5 (and not to 6)

Regards,

Giuseppe

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-11-19 06:28 PM

You are a livesaver!

To avoid this issue for anyone else, would it be possible to change or add in a note to the application configuration page ?