- STMicroelectronics Community

- MEMS and sensors

- MEMS (sensors)

- LIS2DH register details missing

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

LIS2DH register details missing

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-01 01:50 AM

Hi there,

I was working on the LIS2DH for one of our applications, and found that there are some details missing in the datasheet (Doc ID 022516 Rev 1), enlisted below:

1- The bits HPCF2 - HPCF1 in the CTRL_REG2 (21h) corresponding to the high pass filter cut off frequency selection do not have any details mentioned about how they affect the cut-off frequency.

2- The REFERENCE/DATACAPTURE (26h) also does not have any details about it mentioned in the datasheet, except that it acts as the reference for the HPF. What does the "Data Capture" here represent?

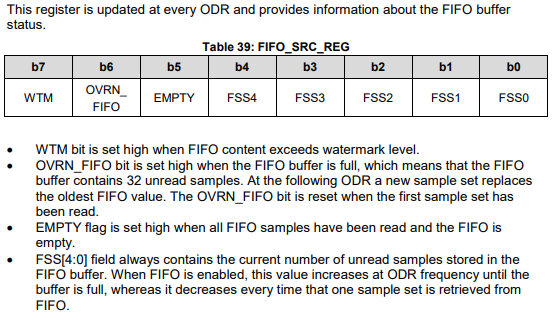

3- Also, there is no information about the various bits of the FIFO_SRC_REG (2Fh).

It would be really appreciable if you could share details on the functionality of these bits/registers.

Looking forward to hearing back from soon.

Warm regards,

Sarthak Malik.

Solved! Go to Solution.

- Labels:

-

Accelerometers

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-09 04:49 AM

Hi @Smalik ,

If the information was useful for you, please click on Select as Best if my reply fully solves your problem or answers your question, to help future community users with the same question.

Thanks,

-Eleon

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-01 03:44 AM

Hi @Smalik ,

Please find below my answers to your questions.

1- The bits HPCF2 - HPCF1 in the CTRL_REG2 (21h) corresponding to the high pass filter cut off frequency selection do not have any details mentioned about how they affect the cut-off frequency.

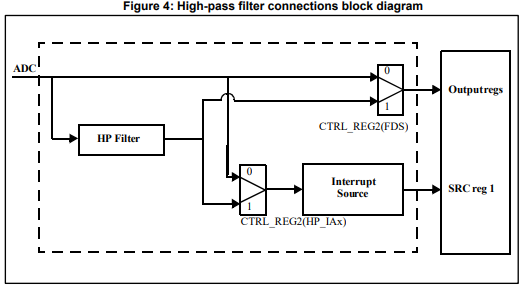

This datasheet section is effectively not well detailed. However, you can refer to the application note AN3308 for the LIS3DH, which is quite identical to the from this register point of view. The High-pass filter working mode is described in p.17, p.18 and p.19 of this app note.

2- The REFERENCE/DATACAPTURE (26h) also does not have any details about it mentioned in the datasheet, except that it acts as the reference for the HPF. What does the "Data Capture" here represent?

The use of this Reference register is as well described in the previous mentioned application note, p.19:

"In this configuration the output data is calculated as the difference between the input acceleration and the content of REFERENCE (26h). This register is in 2’s complement representation and the value of 1 LSB of these 7-bit registers depends on the selected full scale (Table 12: "Reference mode LSB value")".

3- Also, there is no information about the various bits of the FIFO_SRC_REG (2Fh).

FIFO_SRC_REG (2Fh) register is described in the same application note, at p.44 and p.45.

-Eleon

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-09 04:49 AM

Hi @Smalik ,

If the information was useful for you, please click on Select as Best if my reply fully solves your problem or answers your question, to help future community users with the same question.

Thanks,

-Eleon

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-14 12:40 AM

Hi there,

I was working on the LIS2DH for one of our applications, and found that there is some details missing in the datasheet (Doc ID 022516 Rev 1), enlisted below:

- in the CTRL_REG3 (22h) both DRDY bits are shown interrupt on INT1_Pin then what is the role of INT2_Pin and how to enable DRDY interrupt on INT2_Pin.

Looking forward to hearing back from soon.

Warm regards,

Sarthak Malik.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-14 07:57 AM

Hi Sarthak,

well, I believe you are right and that detail is wrong... there are only one DRDY interrupt and only one AOI interrupt, so the CTRL_REG3 (22h) register bits description has to be rephrased in the following way:

- I1_AOI2 --> I2_AOI, DRDY interrupt on INT2 pin. Default value 0

- I1_DRDY2 --> I2_DRDY, DRDY interrupt on INT2 pin. Default value 0

I'll however report it internally to check if it is actually the case.

-Eleon

- LIS2DW12 latching INT1 pin to GND on board reboot in MEMS (sensors)

- Detecting fast Z movement on LIS2DW12 in MEMS (sensors)

- LIS3DH sensor - Required method / formulae to convert the Raw ADC value to Temperature in MEMS (sensors)

- LIS2DTW12 Power Down question in MEMS (sensors)

- STEVAL-MKI231KA The WHO_AM_I register value does not match the device selected. in MEMS (sensors)