- STMicroelectronics Community

- MEMS and sensors

- MEMS (sensors)

- how to enable lsm6dsl i2c master,

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

how to enable lsm6dsl i2c master,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-09-30 05:05 PM

When I enable lsm6dsl I2C as master , both lines are going to gnd.

lsm6dsl_sh_master_set(&dev_ctx, PROPERTY_ENABLE);

any tip on using lsm6dsl sensor hub, thanks

- Labels:

-

INEMO-Inertial Modules

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-01 11:51 PM

Hi @SRabi.1 ,

I suggest you to check the C examples on Github for the LSM6DSM, which has the same Sensor Hub master digital block of the LSM6DSL. In particular, you can consider for example the sensor hub with the LPS22HB pressure sensor, without passing through the FIFO (lsm6dsm_sens_hub_lps22hb.c). Here below the configuration code for the read function (LSM6DSM I2C master, LPS22HB I2C slave):

static int32_t lsm6dsm_read_cx(void* ctx, uint8_t reg, uint8_t* data, uint16_t len)

/* Configure Sensor Hub to read LPS22HB */

mm_error = lsm6dsm_sh_slv0_cfg_read(&dev_ctx, &val);

lsm6dsm_sh_num_of_dev_connected_set(&dev_ctx, LSM6DSM_SLV_0_1);

/* Enable I2C Master and I2C master Pull Up */

lsm6dsm_func_en_set(&dev_ctx, PROPERTY_ENABLE);

lsm6dsm_sh_master_set(&dev_ctx, PROPERTY_ENABLE);

/* Enable accelerometer to trigger Sensor Hub operation */

lsm6dsm_xl_data_rate_set(&dev_ctx, LSM6DSM_XL_ODR_104Hz);

/* Wait Sensor Hub operation flag set */

lsm6dsm_acceleration_raw_get(&dev_ctx, data_raw_acceleration.u8bit);

do

{

lsm6dsm_xl_flag_data_ready_get(&dev_ctx, &drdy);

} while (!drdy);Please let me know if this can be of some help.

-Eleon

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-03 02:35 PM

Thanks for your help, I have the system up and running. But I found the following:

Im using the lsm6dsl as master and the h3lis200dl as slave of the lsm6 sensor hub, is the only device slave

I turned on start_config so that the DRDY signal from the h3lis signals the data availability.

This works up to ODR of 400 Hz. when ODR is at 1Khz, it stops working.

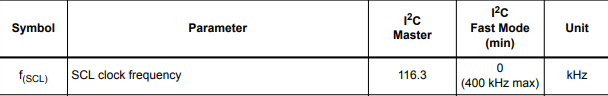

I noticed that the I2C Master clock output from lsm6dsl is 100 Khz. Datasheet says that in master mode it works on fast mode up to 400 Khz.

But I don't find any indication on how to make the clock go to 400 Khz.

At 100 Khz clock retrieving the data from the h3lis takes 1 ms, which is the time of the ODR so of course we can't use ODR at 1 Khz with a 100 Khz clock.

Any help here ?

Thanks, Sergio

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-05 07:22 AM

Hi @Eleon BORLINI I also have the same question regarding the LSM6DSL sensor hub with I2C fast mode. All of the LSM datasheets suggest that the device can operate the MSCL clock line at 400kHz, but we observe only 100kHz. Is there a way to force fast mode?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-06 03:12 AM

Hi @SRabi.1 , @NAnth.1 ,

Please consider the datasheet, p. 28:

The "Fast Mode" is defined for I2C master clocks above 100kHz. The 116kHz clock (typ frequency) that is coming out cannot be calibrated at chip level and is in the fast mode region. So, the two chips are communicating in I2C fast mode with clock frequency fixed at 116kHz.

>> This works up to ODR of 400 Hz. when ODR is at 1Khz, it stops working.

But cannot you receive the ACK any more if you set the ODR 1kHz?

-Eleon

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-06 04:32 AM

The h3lis simply stops generating data ready signal. it looks like that at 1khz if h3lis200 not getting the read instruction in a synchronized pace.

I tried to switch from 400 hz to 1000 hz after sensor hub Signals end of operation.

A single reading cycle Is generated and than dataready is not generated again.

Thanks Sergio

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-06 08:26 AM

Hi @SRabi.1 ,

The I2C pattern block from master to slave is composed by slave address, register address, while from the slave you get 3 x 8bits (the acceleration dataout of the h3lis200). Running at ODR 1kHz with I2C 116KHz, the master may not be so fast to rise the DRDY pin in time...

Btw, did you correctly configured the I2C physical lines (external pull-ups or bit PULL_UP_EN = 1 in reg 1Ah), as described in the application note AN5040 p.58?

-Eleon

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-06 08:43 AM

The dataready is generated by the slave as the sensor hub can only run at 104 Hz max with its own trigger to read external sensors.

With Dataready generated at 400 Hz by the slave it did work, but when I switch to 1 Khz it fails. Yes, pull up is enabled.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-06 10:21 AM

@Eleon BORLINI According to the datasheet, it looked like the LSM6DSL master should drive the I2C bus at 400kHz. If I understand your response correctly, the LSM6DSL considers anything greater than 100kHz as "Fast Mode". Is that correct?

In other words, is the LSM6DSL unable to drive the SCL line faster than 116.3kHz?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-10-07 12:01 AM

Hi @NAnth.1 , you are right. The internal I2C master clock is generated by a fixed clock division from a master with frequency in the order of magnitude of the MHz.

-Eleon

- LSM6DSL data retrieval in MEMS (sensors)

- IMP34DT05 returns only silence in MEMS (sensors)

- Enabling FIFO on LSM6DSOX in MEMS (sensors)

- LSM6DSL Linux Driver, How to add the Gyroscope output registers for user interface as sysfs entries? in MEMS (sensors)

- Setting scale on LSM303AGR Acceleration sensor on STM32F411E Discovery board in MEMS (sensors)