- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Embedded software

- Is UM1884 (STM32L4/L4+ HAL and low-layer drivers U...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Is UM1884 (STM32L4/L4+ HAL and low-layer drivers UM) description for RCC_PLLInitTypeDef inconsistent with header file 'stm32l4xx_hal_rcc.h' generated by STM32CUBEMX with respect to PLLP, PLLR parameter definitions?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-09-17 03:28 PM

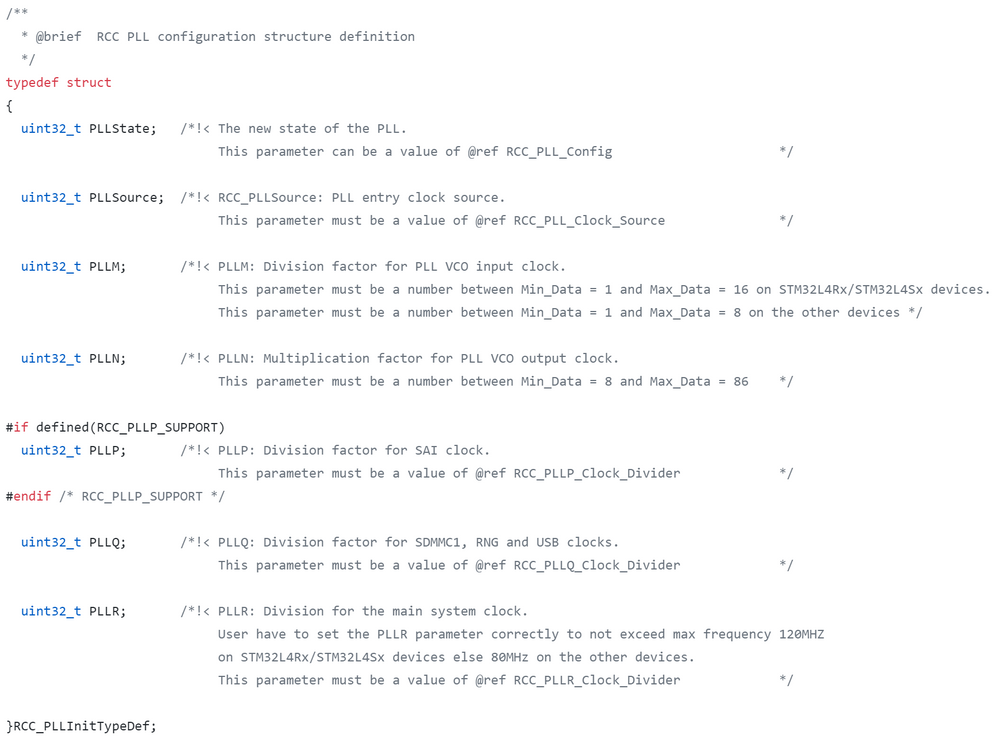

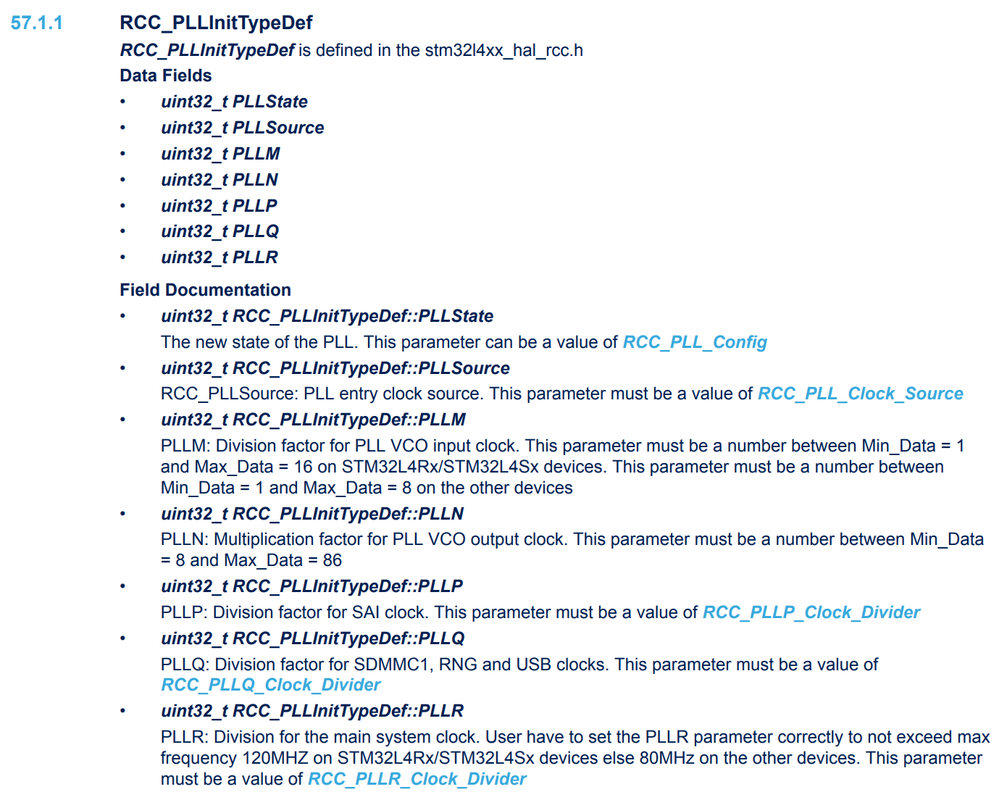

The structure definition for RCC_PLLInitTypeDef in the header file 'stm32l4xx_hal_rcc.h', generated by STM32CUBEMX, is inconsistent with the RCC_PLLInitTypeDef struct description in the STM32L4/L4+ HAL and low-layer drivers UM (UM1884 Rev8) page 821, specifically PLLP, PLLR parameters.

Compare that description with the RCC_PLLInitTypeDef in stm32l4xx_hal_rcc.h, generated by STM32CUBEMX for nucleo-l4r5zi_ board:

typedef struct {

...

#if defined(RCC_PLLP_SUPPORT)

uint32_t PLLP; /*!< PLLP: Division factor for SAI clock.

This parameter must be a value of @ref RCC_PLLP_Clock_Divider */

#endif /* RCC_PLLP_SUPPORT */

uint32_t PLLQ; /*!< PLLQ: Division factor for SDMMC1, RNG and USB clocks.

This parameter must be a value of @ref RCC_PLLQ_Clock_Divider */

uint32_t PLLR; /*!< PLLR: Division for the main system clock.

User have to set the PLLR parameter correctly to not exceed max frequency 120MHZ

on STM32L4Rx/STM32L4Sx devices else 80MHz on the other devices.

This parameter must be a value of @ref RCC_PLLR_Clock_Divider */

}RCC_PLLInitTypeDef;

Am I missing something?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-09-18 09:30 AM

Looks consistent to me. PLLQ and PLLR are defined in both. What do you think is inconsistent about them?

If I were you I would throw away the user manual and consult the code directly. It's always going to be correct.

- inconsistent behaviour in TIMER and CCxR interrupt in STM32 MCUs products

- STM32F4 OSC Problem in STM32 MCUs products

- Delay of interfacing timer is rather inconsistent in STM32 MCUs products

- tpkg file format unclear, import error bug or undocumented feature? in STM32 MCUs TouchGFX and GUI

- STM32G050C8T6 ADC_IN11: inconsistency in the datasheet? in STM32 MCUs products