- STMicroelectronics Community

- STM32 MPUs

- STM32 MPUs products

- Failed to download system image

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Failed to download system image

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-08-02 10:58 PM

Our self-made board contains emmc and lpddr3 (1GB, 32bit). The error message when downloading the image is as the attachment.

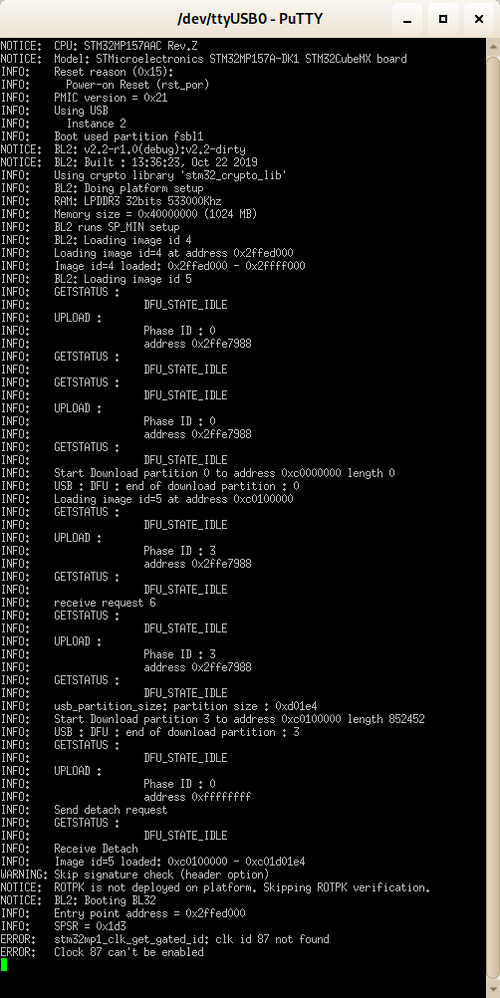

Use Uart to monitor during the download process to get the following information:

NOTICE: CPU: STM32MP157AAC Rev.Z

NOTICE: Model: Thinta TTU Board

INFO: Reset reason (0x15):

INFO: Power-on Reset (rst_por)

INFO PMIC version = 0x21

INFO: Using USB

INFO: Instance 2

INFO: Boot used partition fsbl1

NOTICE: BL2: v2.2-r1.0(debug):v2.2-dirty

NOTICE: BL2: Built : 13:36:23, Oct 22 2019

INFO: Using crypto library 'stm32_crypto_lib'

INFO: BL2: Doing platform setup

INFO: RAM: LPDDR3 8Gb 533MHz v1.45

ERROR: DDR addr bus test: can't access memory @ 0xc0000004I have tried to replace multiple boards. Can you help find the cause of the failure?

- Labels:

-

STM32MP15 Lines

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-08-02 11:54 PM

Hello,

did you customized your Device Tree according to your board ? https://wiki.st.com/stm32mpu/wiki/How_to_create_your_board_device_tree

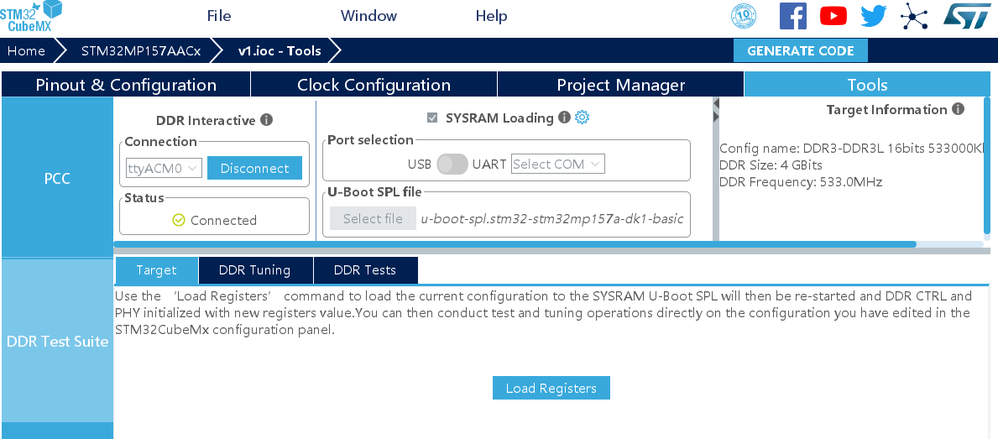

Did you run the DDR tuning tool (par of STM32CubeMx) ? Unless you get the DDR working fine, you cannot go further on the platform programming.

The DDR tuning tool interacts with the target via U-Boot SPL, which must be run instead of TF-A. U-Boot SPL could be loaded in SYSRAM using DDR Tuning Tool and USB .

If your board is compatible with either STM32MP157x-EV1 or STM3@MP157x-DK1/DK2 boards (i.e. Console on UART4 using same pins, using STPMIC1 on I2C4 using same pins and HSE digital bypass), you can directly use the U-BootSPL binary from an ST delivery.

Otherwise, you must build a U-BootSPL binary with a configuration aligned with your board: U-BootSPL binary generation can be done from your Yocto machine adding the "basic" boot scheme in your machine conf file.

Once a DDR config file is ok, it must then be used for build TF-A

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-08-03 12:50 AM

Thanks for your reply.

I had customized the Device Tree according to my board.

But it can't connect to "DDR Interactive". According to the phenomenon, the U-Boot SPL file has been loaded.

The connection status is always displayed in the interface. Does it mean that there is a problem with the LPDDR3 configuration.

Our LPDDR3 model is Samsung's K4E8E324EB, and refer to the LPDDR3 parameters of STM32MP157AAA3 only support 16bit-LPDDR3

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-08-03 01:23 AM

Hi,

Did you check the 5.3 in https://www.st.com/resource/en/user_manual/dm00104712-stm32cubemx-for-stm32-configuration-and-initialization-c-code-generation-stmicroelectronics.pdf (and particularly check the 5.3.2) ?

DDR Tool should connect to your board even if LPDDR3 settings are not yet good (u-Boot SPL does not use DDR to start). That's the purpose of the tool.

If you are not able to connect, you could have either a mistake on the UART + USB connection (USB used to download u-BootSPL using DFU, then UART used as main control of u-Boot SPL) or a mistake in your Device Tree making it not starting (of badly starting). You should solve that first.

The LPDDR3 settings is only an example you could refer to, but should be checked/refined to your board specific using DDR Tuning tool.

Regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-08-03 09:10 AM

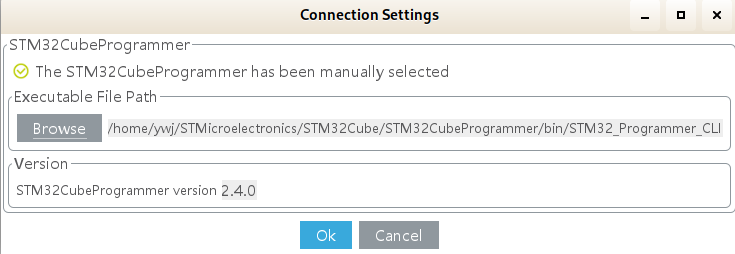

Did you setup the path to CubeProgrammer_CLI (blue config button next to 'SYSRAM Loading") ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-08-03 08:39 PM

Yes, I had setup the path.

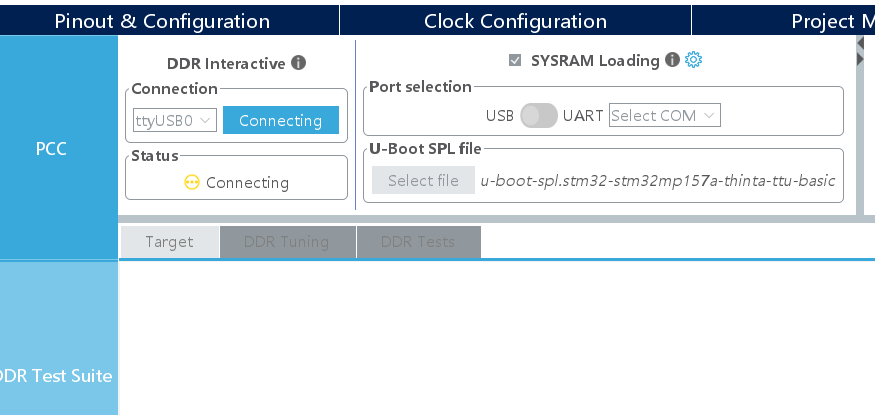

My PC environment is no problem. I have a MP157a-dk1 development board that can be connected to DDR tuning.

If select the U-Boot SPL file I compiled to connect to the MP157a-dk1, the connection status is always been "connecting". So I guess there have some problem with the dts parameter.

Is the log obtained during downloading sufficient to judge that there is no problem with Uart and usb?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-08-04 06:01 AM

Hi @YWu.2 ,

First, to confirm LPDDR is correctly powered, could you please provide traces of LPDDR supplies (both 1.2V and 1.8V) ?

Then, what source of TF-A did you use? Github?

Thanks

Milan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-08-05 04:38 AM

Note that If you use STM32MP15-ecosystem-v2.0.0 release, you need to use at least CubeProgrammer v2.5.0.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-08-07 12:29 AM

Thanks @PatrickF and @mleo

The problem that DDR Tuing cannot be tested has been resolved. The reason is that the voltage of ldo3 of pmic is incorrect, it should be 1.8v for lpddr3.

Now encounter new problems. The debug port returns an error "Clock 87 can't be enabled" during download.

Please refer to the attachment log.7z for the specific log. Please help analyze the possible causes.

- STM32CubeProgrammer v2.16.0 released in STM32CubeProgrammer (MPUs)

- Can't flash my eMMC on STM32MP157 in STM32 MPUs Boards and hardware tools

- OTP Bits Cannnot read in STM32 MPUs products

- Yocto project - bitbake fails when using stm32mp13-disco machine in STM32 MPUs Embedded software

- STM32MP157F-EV1 Starter Package remote console hangs at initial login in STM32 MPUs Boards and hardware tools