- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- Timer in cascade mode for PWM

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Timer in cascade mode for PWM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-09 02:31 AM

I would like to control RC servos with PWM. Problem is that "Normal" PWM would waste most of the precision on the PPM period (20ms) leaving 5% of 16 or 32 bit timer for duty cycle. (1-2ms)

I was reading about cascading timers and that is probably the way to solve my problem, but I cant wrap my head around how exactly will slave timer reload and start each PPM period.

My idea was to use Timer1 for PPM period. Set the prescale and limit to make 50Hz signal. Set it as a repeated counter with up-count. Assign TRGO for Timer1.

User Timer2 as a slave in one pulse mode. Enable TRGI and set prescale and limit that will suit the precision of the duty cycle.

And this is where I dont understand how to set Timer2 to re-load limit on the reset of the Timer1 and start.

In the datasheet it says that slave can be reset, triggered .. But can it be both ? I need slave to reset and trigger on the limit reset of the master.

Also, if I want to use few PWM channels from Timer2 to control multiple servos, would procedure be the same ? All of the channels will of course have same upper limit and different CCRx values for their duty cycle ?

- Labels:

-

TIM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-09 03:09 AM

In one pulse mode the timer runs to the limit, reloads the counter and stops, then it can be triggered again to repeat the cycle. Just ensure that the period of the master is always longer than the period of the slave.

Set timer 2 SMS in SMCR to trigger mode (0b110), and set the OPM in CR1, but do not start it. Now it waits for the trigger signal from the master. When the trigger signal arrives, the slave starts counting (CEN is set to 1 by the trigger), and outputs whatever PWM pulse is programmed in CCMR/CCER/CCR. When the limit is reached, it reloads the counter (to 0 or ARR depending on the direction) and stops counting, CEN is cleared automatically because OPM is set. So its state is identical to the state before the previous trigger, and it can be triggered again.

Note that you should ensure that the output level remains inactive when the slave is waiting for the trigger. E.g. in PWM mode 1 upcounting, CNT is 0 while waiting for the trigger, so if CCR > 0 then the output is active. Use either PWM mode 2, or downcounting, or invert the output in CCER.

See the description of one pulse mode in the reference manual for more details.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-09 06:23 AM

Which STM32?

What is PPM period?

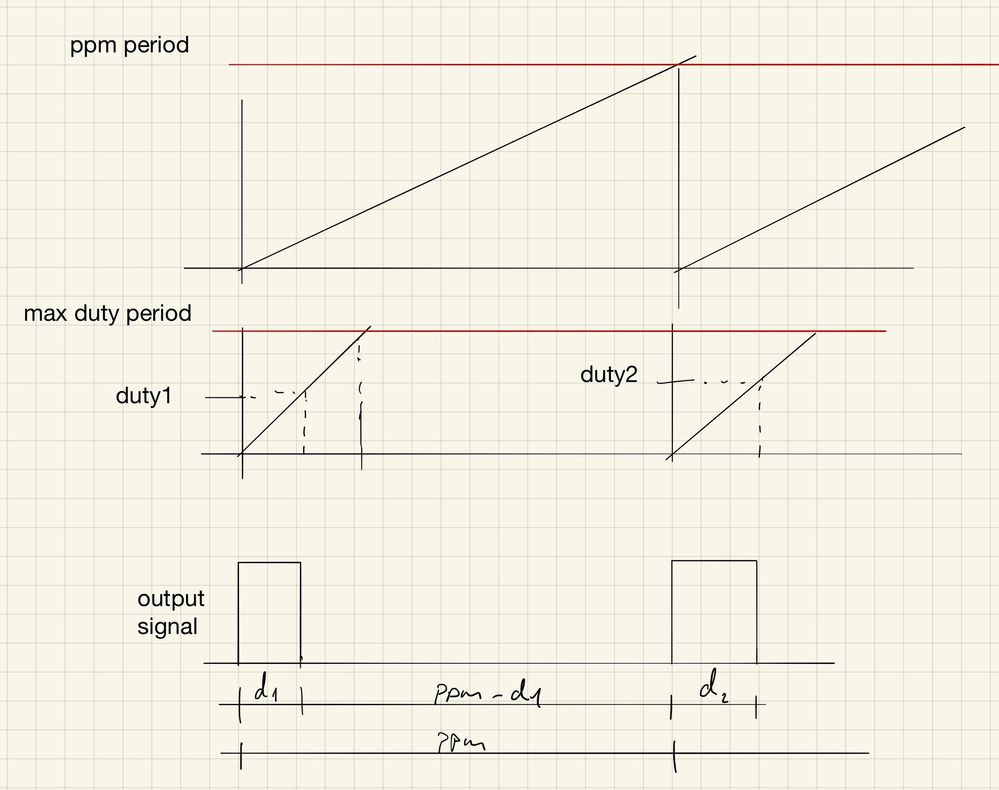

Can you draw a timing diagram to show exactly what do you want to achieve?

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-10 06:47 AM

It is STM32F407.

PPM period is like a carrier frequency. receiver is expecting to see raising edge every period for duty cycle duration. In the case of RC servo it is 20ms period and duty cycle duration if between around 1ms to 2ms. It could be little bit lower and higher limits, but mostly around those values.

Timing diagram attached.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-10 04:06 PM

> Problem is that "Normal" PWM would waste most of the precision on the PPM period (20ms) leaving 5% of 16 or 32 bit timer for duty cycle. (1-2ms)

Think more about it... 5% of 2^16 is 3277 steps or 11,7-bit resolution, which is more than enough for RC servos. And 32-bit timer starts to limit resolution only at 50 Hz * 2^32 = 215 GHz timer frequency. As that is impossible, the time resolution is practically limited only by timer clock period. At 168 MHz that 1 ms is 168'000 steps or 17,4-bit resolution. To me it seems that you are trying to solve non-existent problem here. 🙂

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-11 01:24 PM

You are probably right that I am overthinking this one 😂

But It is still good to know the other/better way of solving the problem.

- CubeMX STM32L4 code generation question in STM32 MCUs products

- STM32l496: Clocking timer using LSCO in STM32 MCUs products

- Delay of interfacing timer is rather inconsistent in STM32 MCUs products

- Timer Single Channel ADC + DMA does not seem to activate HAL_ADC_ConvCpltCallback in STM32CubeMX (MCUs)

- RTC or timer? in STM32 MCUs Embedded software