- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- STM32H745/755 cores frequency after reset is not t...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32H745/755 cores frequency after reset is not the same?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-16 06:57 AM

Hi guys, I read reference manual for STM32H745/755, where is mentioned that the both CPUs are after reset running on the same clock frequency, because they shared the same clock source and the prescalers are after reset in default state (no division of clock signal). I did stupid test in main loop with blinking LEDs driven separately (each on one core), but they are blinking with different period. I didnt set up anything else, interrupts are not allowed but I cant find the reason of different LEDs blinking period.

Thanks a lot for advices!

Solved! Go to Solution.

- Labels:

-

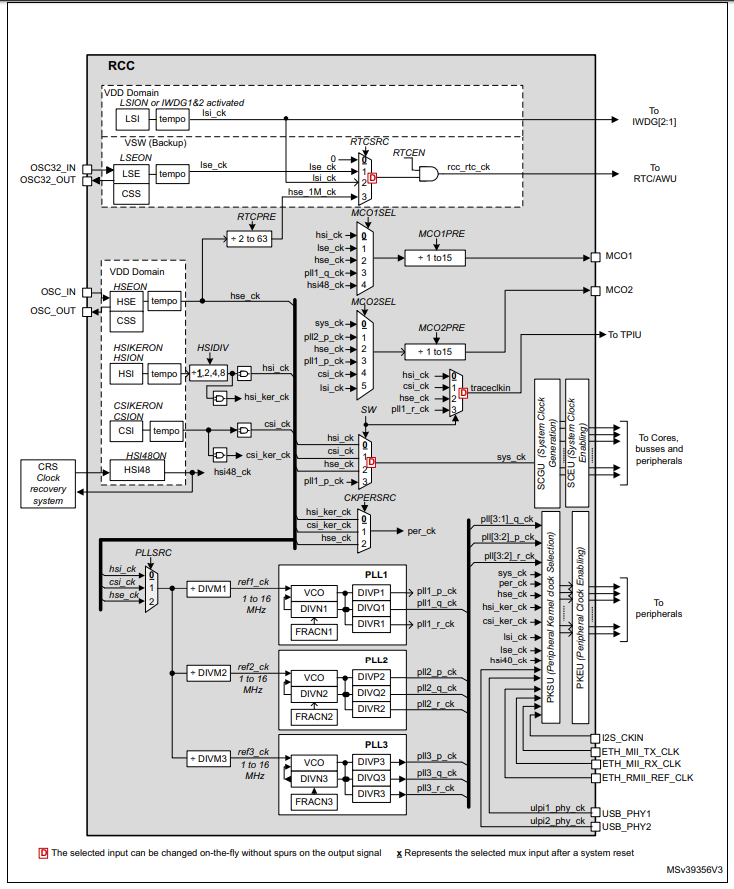

RCC

-

STM32H7 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-16 07:51 AM

The more advanced pipeline and branch predictor in the M7 core can make a big difference.

Moreover the M7 core has a direct 64 bit path to the flash memory, while the M4 core goes through a 32-to-64 bit gateway with caching disabled. So the M7 can benefit from its 64 bit prefetch unit (which is I think always active), while the M4 must make separate accesses for each 32 bit word in the flash.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-16 07:09 AM

They have different cores, so the execution time of some instructions are different.

They are not connected in the same way to the system bus, and have different caches, so the time they need to read their program from the flash is not the same. See Figure 1. System architecture for STM32H745/55/47/57xx devices in the reference manual.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-16 07:12 AM

Hi, thanks for reply, the difference in period is really big, maybe two times faster, I guess this is not caused by different execution time and Im not using caches for M7.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-16 07:51 AM

The more advanced pipeline and branch predictor in the M7 core can make a big difference.

Moreover the M7 core has a direct 64 bit path to the flash memory, while the M4 core goes through a 32-to-64 bit gateway with caching disabled. So the M7 can benefit from its 64 bit prefetch unit (which is I think always active), while the M4 must make separate accesses for each 32 bit word in the flash.

- STM32CubeProgrammer Error: No STM32 target found! in STM32 MCUs products

- Strange results with STLink Utility vs Programmer SWD in STM32CubeProgrammer (MCUs)

- MotionMC running algo but no output bias data calculated (all to default) in STM32 MCUs Embedded software

- STM32G071 ADC sequencer in not fully configurable mode and ADC channels set run-time changing in STM32 MCUs products

- UART cosfiguration directly with registers, NUCLEO-H563ZI board in STM32CubeIDE (MCUs)