- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- DAC output differs between Channel 1 & 2 on Nucleo...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

DAC output differs between Channel 1 & 2 on Nucleo-F446RE

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-09 10:07 AM

Hi 🙂

I found something quite strange, it seems that:

1) On DAC Channel 1 - the output buffer does not work (a 10kOhm load brings the voltage down), but it's output is inverted (as expected)

2) On DAC Channel 2 - the output buffer does work (maintains voltage with a 10kOhm load), but it's output is not inverted

My test setup:

- NucleoF446RE -> PA4/A2 pin -> oscilloscope + 10k resistor (in parallel)

- NucleoF446RE -> PA5/D13 pin -> oscilloscope + 10k resistor (in parallel)

- The code runs a simple one-time 500Hz sine wave with samples @32kHz with DMA. I also tested without DMA with a simple HAL_DAC_SetValue() and the result was exactly the same (but not as "visual" as with a sine wave).

The results:

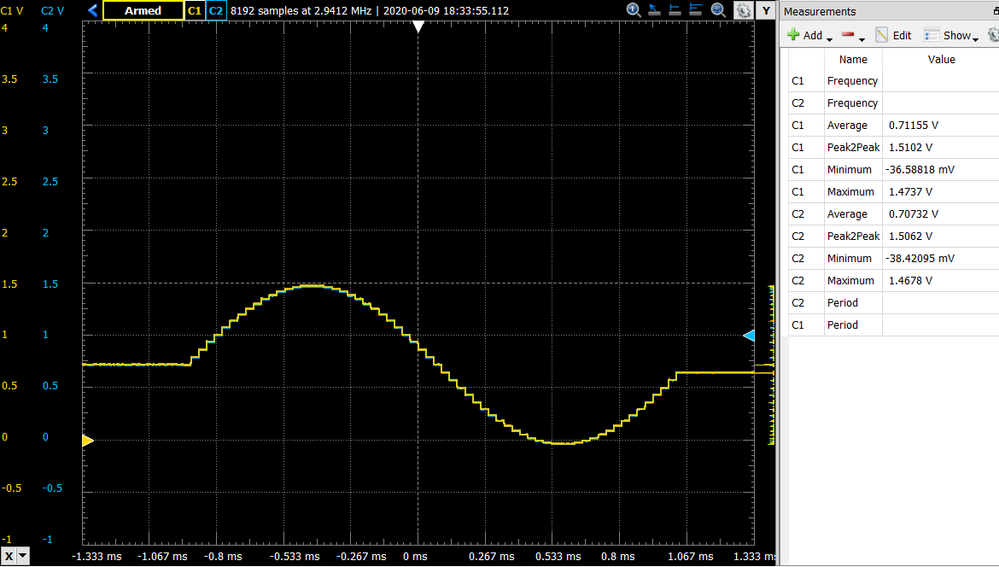

With Output buffer OFF on both channels, the sine wave is not inverted, and the voltage is sinked to max 1.5V - this is as expected.

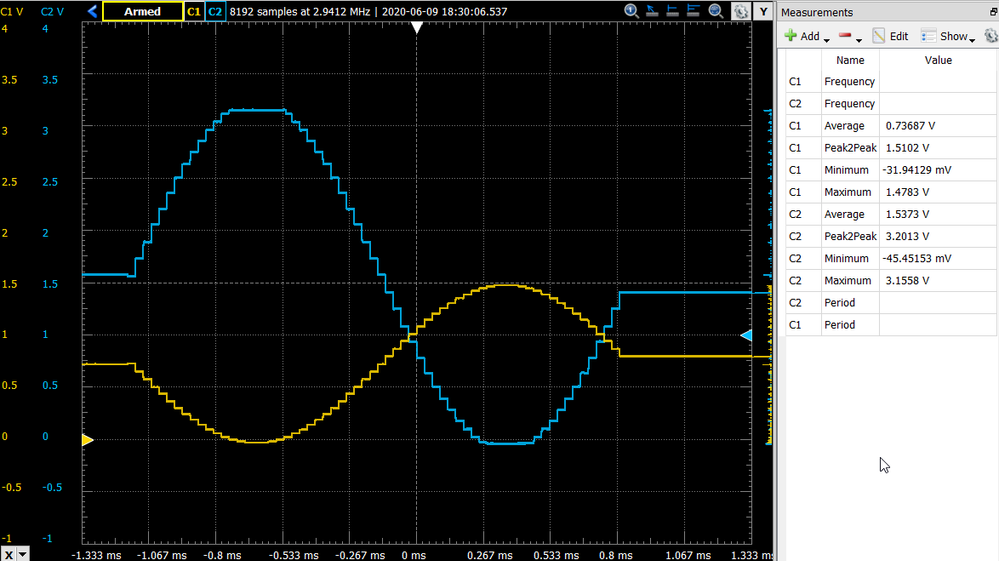

With the output buffer ON on both channels, you can see that Channel 1 (yellow) is inverted but its output is still sinked, and that Channel 2 (blue) is not inverted but its output is maintained with the load.

Note 1: I desoldered the SB21 to disconnect the LED 2 from the output of the Channel 2 - but even before I did the results were almost the same (it just added a load and a small cut at the top of the waveform).

Note 2: I also double checked the value of the DAC->CR register with the debugger, it shows:

- Binary:110000000001010011000000000101 with buffer ON (bit 1 and 17 not set)

- Binary:110000000001110011000000000111 with buffer OFF (bit 1 and 17 set)

I went through the datasheet but it does not say anything about differences between the DAC's. I guess I am doing something wrong somewhere?

Thank you!! :D

- Labels:

-

DAC

-

STM32F4 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-09 02:02 PM

Why would inverting be normal? It's not.

Reminds me of https://community.st.com/s/question/0D50X00009XkZsS/my-dac-outputs-inverted-values-0000-33v-and-4095-0v

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-09 11:42 PM

Thanks Jan for your reply - you are on every post ha ha! :D

Very interesting that post - that's exactly my issue, so I guess I just destroyed the buffer then...

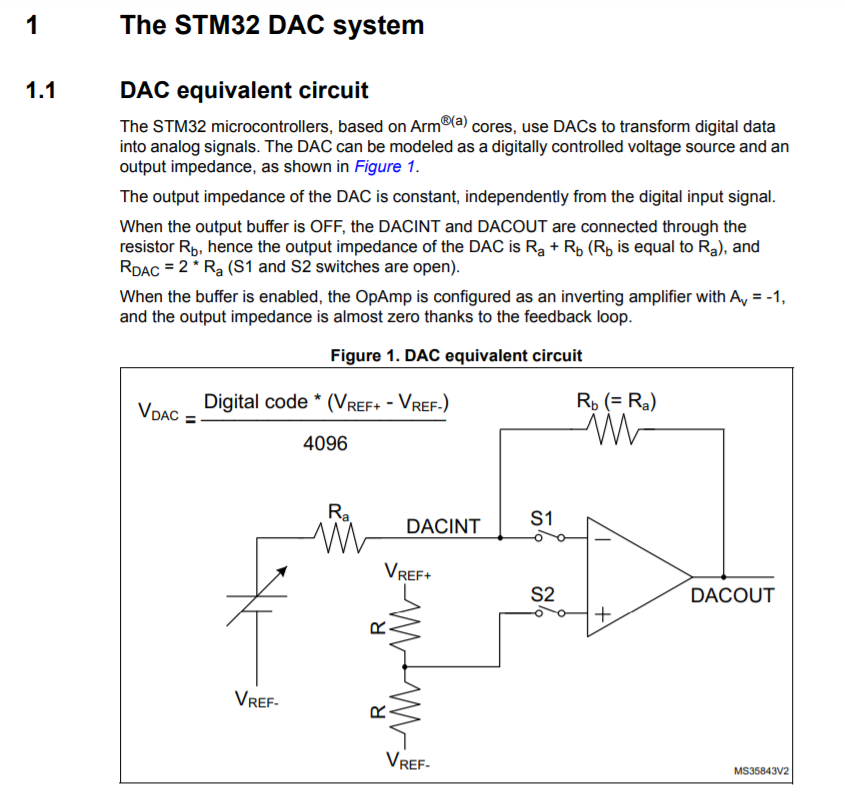

And yes I would expect the buffer to invert the output, since it is configured as an inverting opamp with G=-1 ?

See from https://www.st.com/resource/en/application_note/dm00129215-extending-the-dac-performance-of-stm32-microcontrollers-stmicroelectronics.pdf @page 5:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-10 01:35 AM

> Very interesting that post - that's exactly my issue, so I guess I just destroyed the buffer then...

I don't know, I just posted a link. Maybe you should try on a different piece of hardware the same software.

> And yes I would expect the buffer to invert the output, since it is configured as an inverting opamp with G=-1 ?

Interesting. Why wouldn't the RM mention that?

I don't remember whether I ever used the DAC with buffer.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-11 09:25 AM

Well it does match exactly the results I am getting. Thanks anyways.

And I guess by "RM" you mean the datasheet? If so that is true I double-checked and it is not written anywhere, only on that other ST document...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-11 01:12 PM

STM32 uses a set of reference materials, some more general for the family, other specific to the particular model:

PM = Programing Manual, here PM0214 (describes the ARM processor/core)

RM = Reference Manual, here RM0390 (describes a family's buildup and peripherals from programming/functional point of view)

DS = Datasheet, here DS10693 (describes particular model, giving overview and model-specific set of parameters)

ES = Errata Sheet, here ES0298 (model-specific errata)

Then there is supplementary material: AN (application notes), TN (technical notes), UM (user manual, usually for software) and maybe some other which are mostly promotional/marketing.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-12 03:50 AM

Nice to know! Thank you Jan!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-18 02:02 PM

Just FYI - I tested it on my Disco-L1 board and it works as expected: no inversion and the DAC can handle a light load, same on both channels.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-18 03:17 PM

Thanks for coming back with this info.

JW

- Trigger from Timer does not trigger injected conversion on ADC in STM32 MCUs products

- CubeIDE update CubeMX 6.10.0 to 6.11.0 STM32H723 ADC channel TEMPSENSOR VBAT VREFINT missing in STM32CubeIDE (MCUs)

- STM32F412 Multiple PWM Control Inquiry in STM32 MCUs products

- F411 ADC1 VBAT Reading Too High in STM32 MCUs products

- LPBAM I2C data buffer using NUCLEO-U575ZI-Q in STM32 MCUs products