- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- Having problem to understand DMA

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Having problem to understand DMA

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-05-27 05:44 PM - edited 2023-11-20 09:32 AM

I am trying to learn DMA properly by reading from STM32F407 reference manual . But I am confused at some points. First is about FIFO mode:

- Lets say I am receiving data from UART over DMA and I am using DMA FIFO mode with threshold 1/2(that is 8 byte). And destination and source size is 1 byte. What should I do to get data from FIFO when my number of data to receive is less than 8. For example how to get that datas from the FIFO when I received 5 bytes in my FIFO and not expecting more. Due to threshold level(8byte) is it keeps that datas or it will send them with looking to number of data register is equal 0.

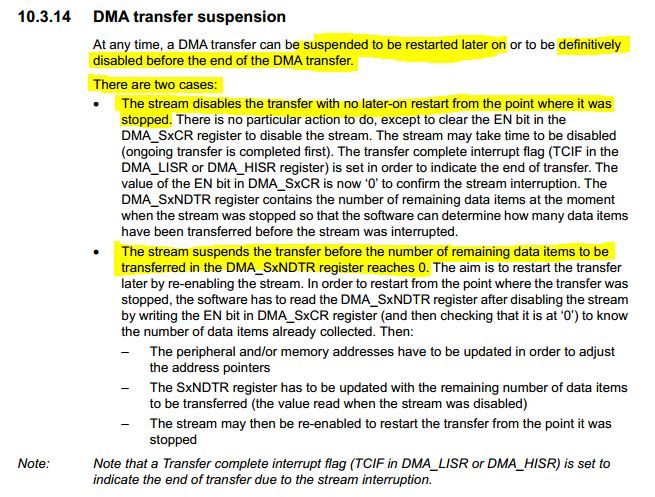

-Second thing where I confused is statements in the below:,

When these two cases occurs? For example higher priority DMA request comes while lower on operation creates one?

And how can I understand one of them occurred?

and last: Am I missing something or these two cases are same, one says suspend and other says disables but what they caused and the solution looked same to me.

What the f*ck kind of suspension is that I should intervene to make it work again. It's f**king disabling, and ****** me off. This document making me crazy sometimes.

Solved! Go to Solution.

- Labels:

-

DMA

-

STM32F4 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-05-27 07:16 PM

The first case happens when you clear the EN bit. So don't.

The second case also happens when you clear the EN bit. So don't.

These two cases are initiated by your code. They don't happen spontaneously. If you don't want them to happen, just don't touch the EN bit.

If you want a non-even multiple of bytes, the simplest solution is to just use direct mode. No reason to use FIFO with UART since it's so slow.

To flush the FIFO, reset the EN bit. Per the reference manual:

FIFO flush

The FIFO can be flushed when the stream is disabled by resetting the EN bit in the

DMA_SxCR register and when the stream is configured to manage peripheral-to-memory or

memory-to-memory transfers: If some data are still present in the FIFO when the stream is

disabled, the DMA controller continues transferring the remaining data to the destination

(even though stream is effectively disabled). When this flush is completed, the transfer

complete status bit (TCIFx) in the DMA_LISR or DMA_HISR register is set.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-05-27 05:50 PM

Still I can't understand why I should re-start it after "suspension". Shouldn't it done by hardware like nested interrupt routines.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-05-27 07:16 PM

The first case happens when you clear the EN bit. So don't.

The second case also happens when you clear the EN bit. So don't.

These two cases are initiated by your code. They don't happen spontaneously. If you don't want them to happen, just don't touch the EN bit.

If you want a non-even multiple of bytes, the simplest solution is to just use direct mode. No reason to use FIFO with UART since it's so slow.

To flush the FIFO, reset the EN bit. Per the reference manual:

FIFO flush

The FIFO can be flushed when the stream is disabled by resetting the EN bit in the

DMA_SxCR register and when the stream is configured to manage peripheral-to-memory or

memory-to-memory transfers: If some data are still present in the FIFO when the stream is

disabled, the DMA controller continues transferring the remaining data to the destination

(even though stream is effectively disabled). When this flush is completed, the transfer

complete status bit (TCIFx) in the DMA_LISR or DMA_HISR register is set.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-05-27 07:33 PM

Thank you so much. I thought these cases occur like interrupts by hardware. Apologize for bad language.

- Erase Flash Memory with FreeRTOS in STM32 MCUs Embedded software

- HAL.tick() stops debug in STM32 MCUs TouchGFX and GUI

- Use SD Card/ FATFS in STM32CubeIDE (MCUs)

- External Powering of NUCLEO-L031K6 HSE able to run? in STM32 MCUs Boards and hardware tools

- error: launching debug has encountered a problem in STM32CubeIDE (MCUs)