- STMicroelectronics Community

- STM32 MCUs Software development tools

- STM32CubeMX (MCUs)

- I have an issue with ADC and Vrefint

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

I have an issue with ADC and Vrefint

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-05-25 01:30 PM

Hi,

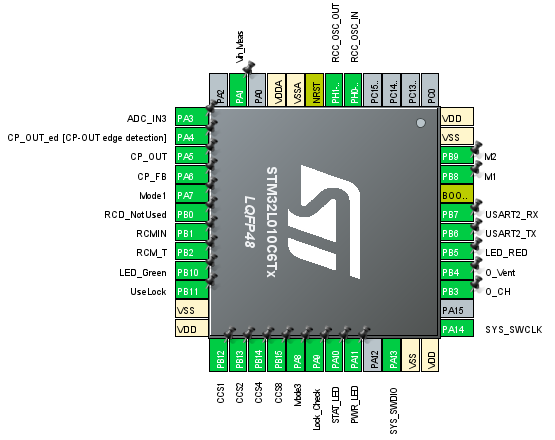

I working with an STM32L010 controller. I have a confusing issue with one of ADC channel.

Here is the configuration:

I using ADC channels 1, 3, 6 and Vrefint.

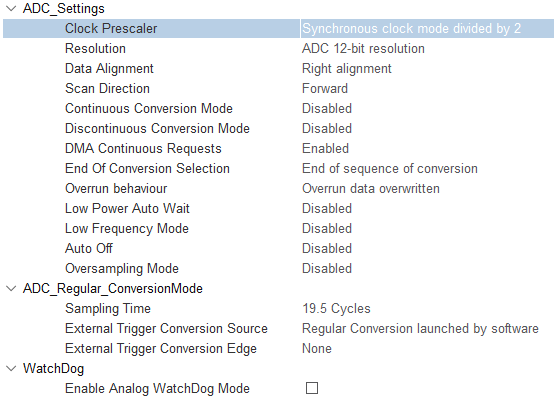

Here is the ADC configuration:

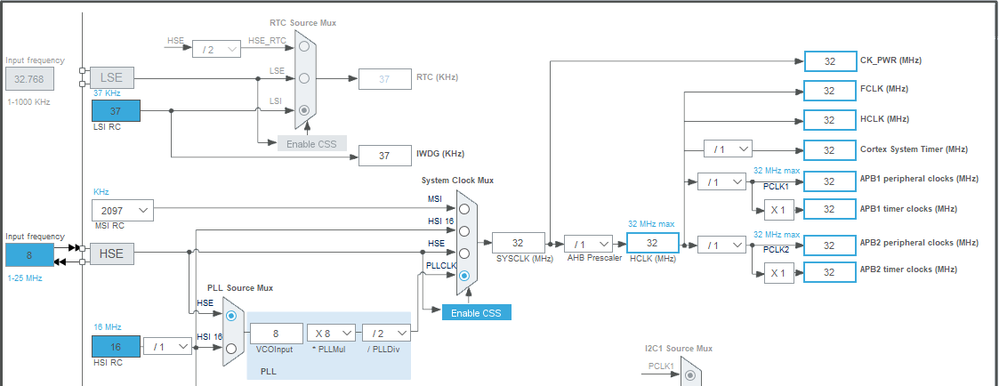

I forgot the clock configuration:

My problem is while the voltage on CH3 increasing from 0 to about 2V the calculated VDD will started to increasing to 3.9V until the CH3 reach 2.4V. In above the VDD falling down to 3.3V. As I see Vrefint value changing. Like it would have a negative characteristic. I using formula from refmanual to convert raw values to mV. On VDD(a) pin I can see about 20mV changes during I increasing voltage on CH3. Could it cause this kind of ADC behavior?

Thank you!

Attila

- Labels:

-

ADC

-

STM32CubeMX

-

STM32L0 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-05-25 02:57 PM

You did not tell us the ADC clock frequency/APB frequency, but I bet 19.5 cycles sampling time violates the min 5us typ. (read recommended ) 10us ADC sampling time when reading the internal reference voltage value given in the datasheet.

JW

- X-CUBE-EEPROM function EE_Init returns EE_OK when flash program fails instead of EE_WRITE_ERROR in Other tools (MCUs)

- Issue with OCD in STM32CubeIDE (MCUs)

- Reinitialization of UART and ADC in STM32CubeProgrammer (MCUs)

- Getting the linker file issue on STM32CubeIDE - Undefined Reference in STM32CubeIDE (MCUs)

- STM32L432 UART receive IRQ handler unable to created by Cube in STM32CubeMX (MCUs)