- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs TouchGFX and GUI

- DCMI with DMA interface to AXI_SRAM results in TRA...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

DCMI with DMA interface to AXI_SRAM results in TRANSFER ERROR

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-05-14 03:09 AM

Hello

My setup contains an STM32H743 with a camera attached via DCMI interface.

I am trying to acquire single snapshot, but unfortunately experiencing errors.

I declared the following variable on my SRAM

#define BUFF_SIZE (160*120)

ALIGN_32BYTES(uint8_t frame_buff[BUFF_SIZE]);the variable is allocated in the AXI_SRAM region (0x240....)

i also defined the MPU

MPU_InitStruct.Enable = MPU_REGION_ENABLE;

MPU_InitStruct.Number = MPU_REGION_NUMBER0;

MPU_InitStruct.BaseAddress = D1_AXISRAM_BASE; // (0x24000000)

MPU_InitStruct.Size = MPU_REGION_SIZE_512KB;

MPU_InitStruct.SubRegionDisable = 0x0;

MPU_InitStruct.TypeExtField = MPU_TEX_LEVEL0;

MPU_InitStruct.AccessPermission = MPU_REGION_FULL_ACCESS;

MPU_InitStruct.DisableExec = MPU_INSTRUCTION_ACCESS_ENABLE;

MPU_InitStruct.IsShareable = MPU_ACCESS_NOT_SHAREABLE;

MPU_InitStruct.IsCacheable = MPU_ACCESS_CACHEABLE;

MPU_InitStruct.IsBufferable = MPU_ACCESS_NOT_BUFFERABLE;and the DCMI's DMA intialized with

/* DCMI Init */

hdma_dcmi.Instance = DMA2_Stream1;

hdma_dcmi.Init.Request = DMA_REQUEST_DCMI;

hdma_dcmi.Init.Direction = DMA_PERIPH_TO_MEMORY;

hdma_dcmi.Init.PeriphInc = DMA_PINC_DISABLE;

hdma_dcmi.Init.MemInc = DMA_MINC_ENABLE;

hdma_dcmi.Init.PeriphDataAlignment = DMA_PDATAALIGN_WORD;

hdma_dcmi.Init.MemDataAlignment = DMA_MDATAALIGN_WORD;

hdma_dcmi.Init.Mode = DMA_NORMAL;

hdma_dcmi.Init.Priority = DMA_PRIORITY_HIGH;

hdma_dcmi.Init.FIFOMode = DMA_FIFOMODE_ENABLE;

hdma_dcmi.Init.FIFOThreshold = DMA_FIFO_THRESHOLD_FULL;

hdma_dcmi.Init.MemBurst = DMA_MBURST_INC4;

hdma_dcmi.Init.PeriphBurst = DMA_PBURST_SINGLE;

if (HAL_DMA_Init(&hdma_dcmi) != HAL_OK)

{

Error_Handler();

}

__HAL_LINKDMA(dcmiHandle,DMA_Handle,hdma_dcmi);

/* DCMI interrupt Init */

HAL_NVIC_SetPriority(DCMI_IRQn, 15, 0);

HAL_NVIC_EnableIRQ(DCMI_IRQn);then, starting the function

HAL_DCMI_Start_DMA(&hdcmi, DCMI_MODE_SNAPSHOT, (uint32_t)frame_buff, BUFF_SIZE);I found out that my `frame_buff` is empty, and after debugging a while, found out that I keep getting a DMA IRQ which results with the error code

HAL_DMA_ERROR_TEPlease, help me find out the reason for the problem with the data transfer.

Sincerely

Dan

Solved! Go to Solution.

- Labels:

-

DCMI

-

DMA

-

STM32H7 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-05-24 02:03 PM

DMA2_S1CR is suspiciously set to byte transfer on both ports. You did not show us the FIFO control register for stream 1.

Can't this be consequence of the infamous "DMA needs to be enabled first" bug of the older CubeMX versions?

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-05-14 04:51 AM

Please post the contents of the DMA, DMAMUX and DCMI registers before and after starting DMA.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-05-14 02:32 PM

Hello

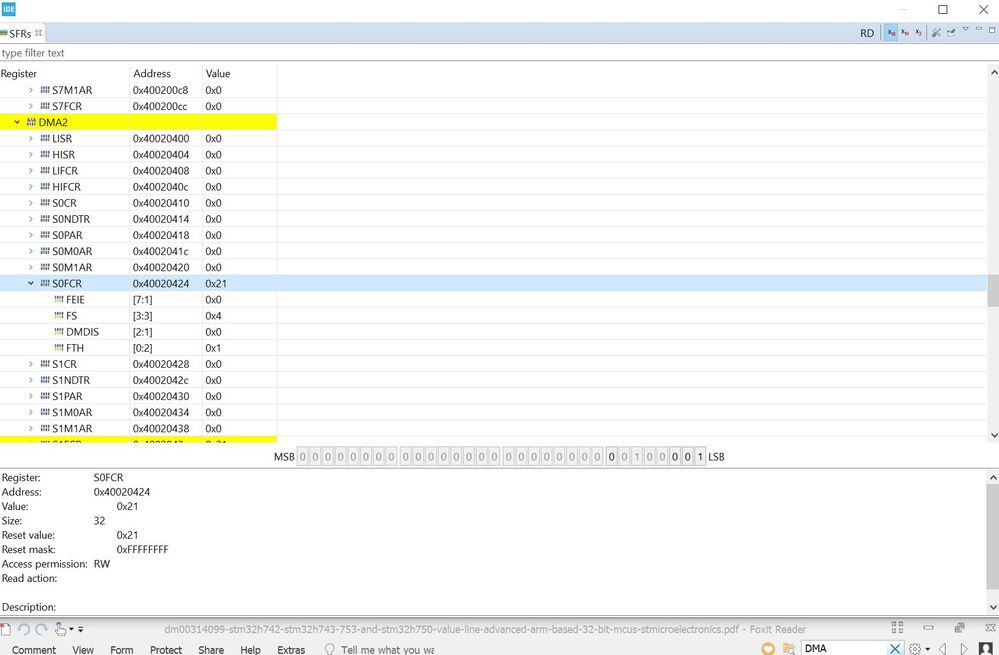

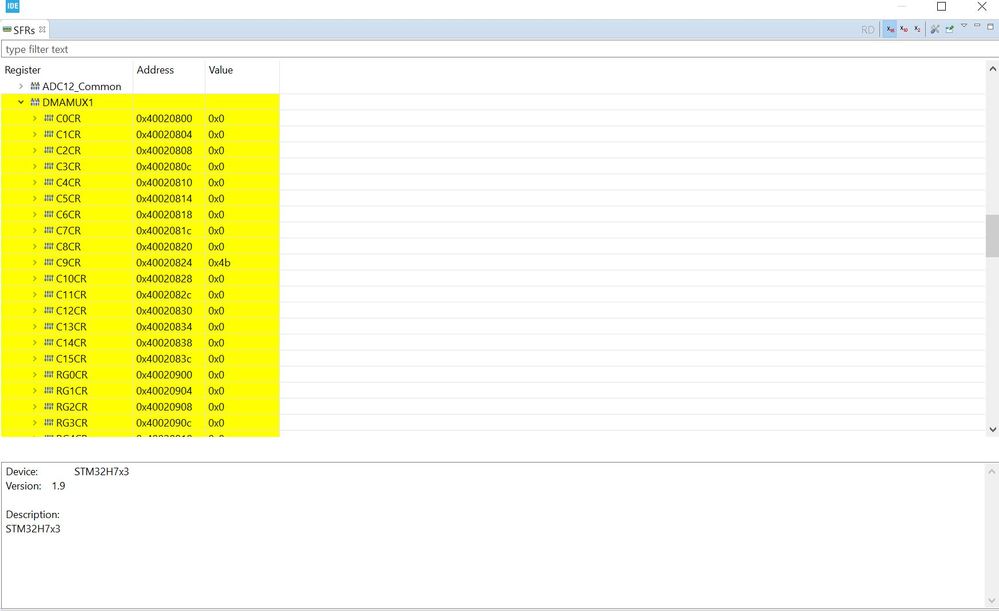

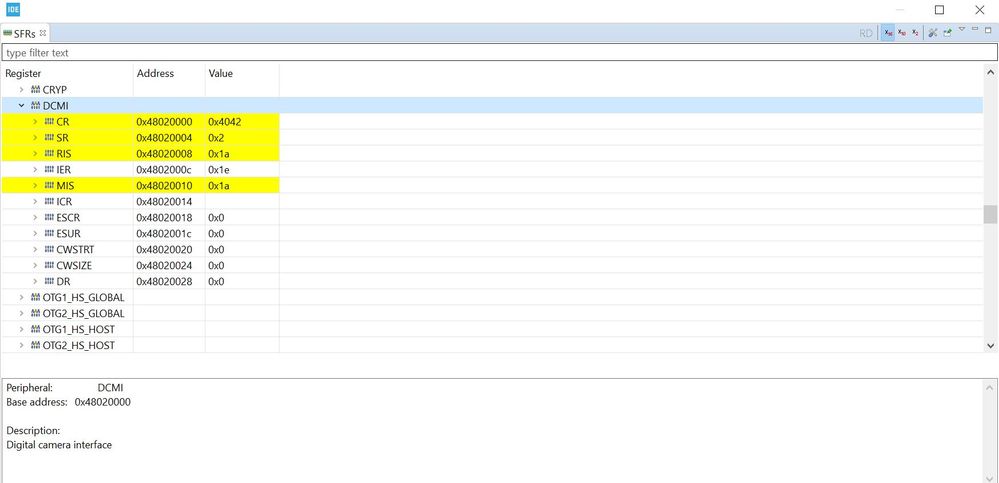

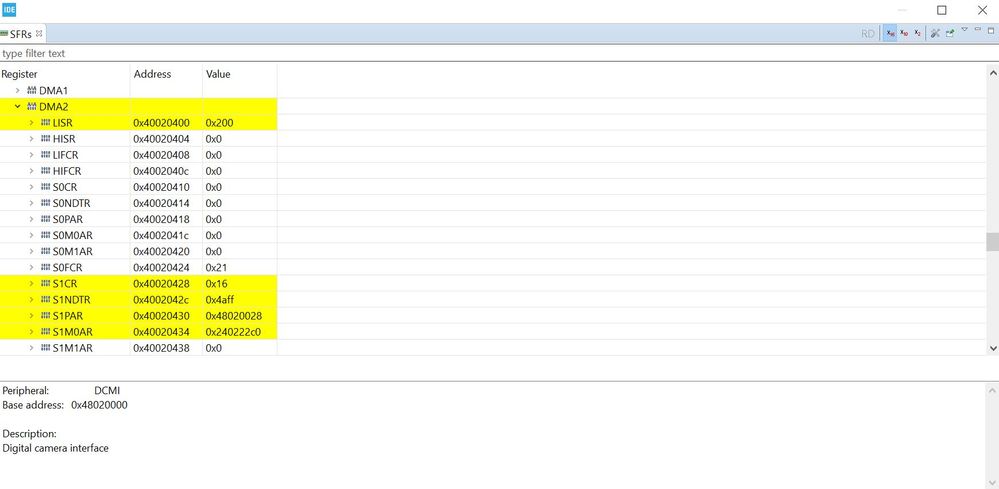

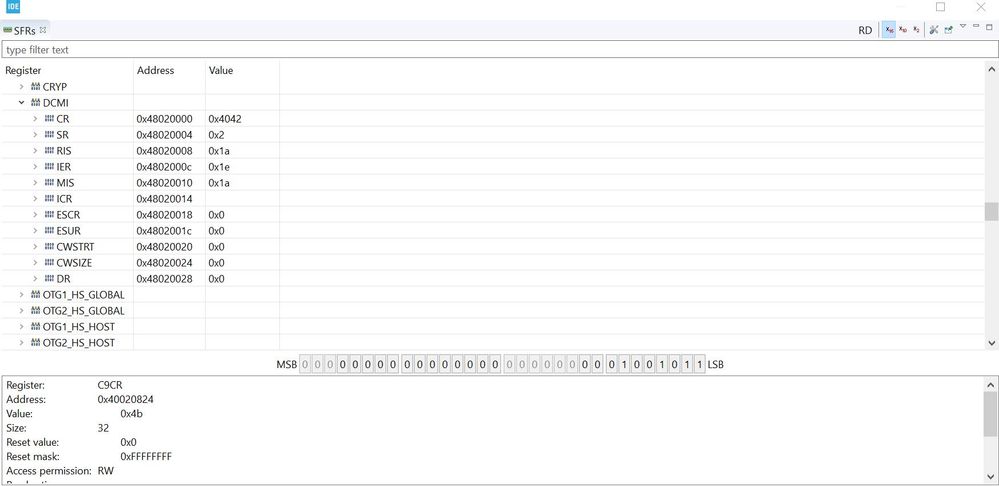

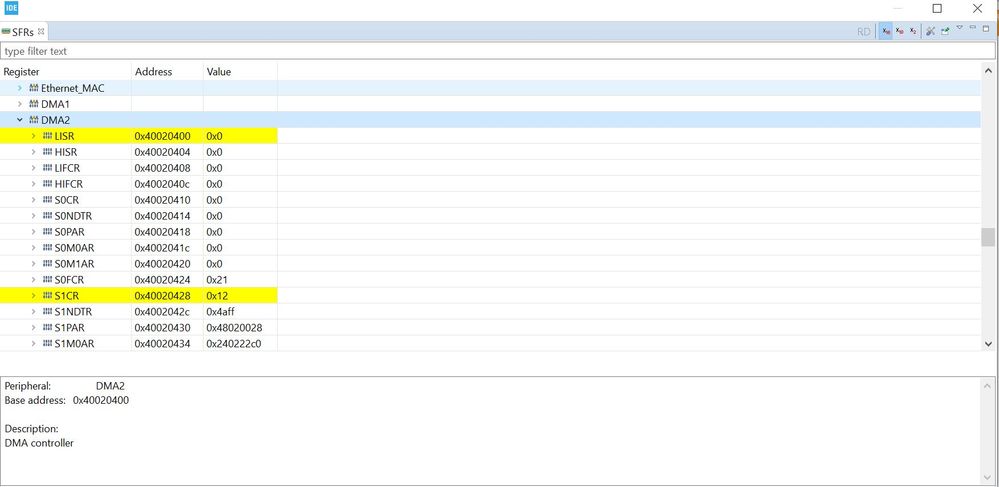

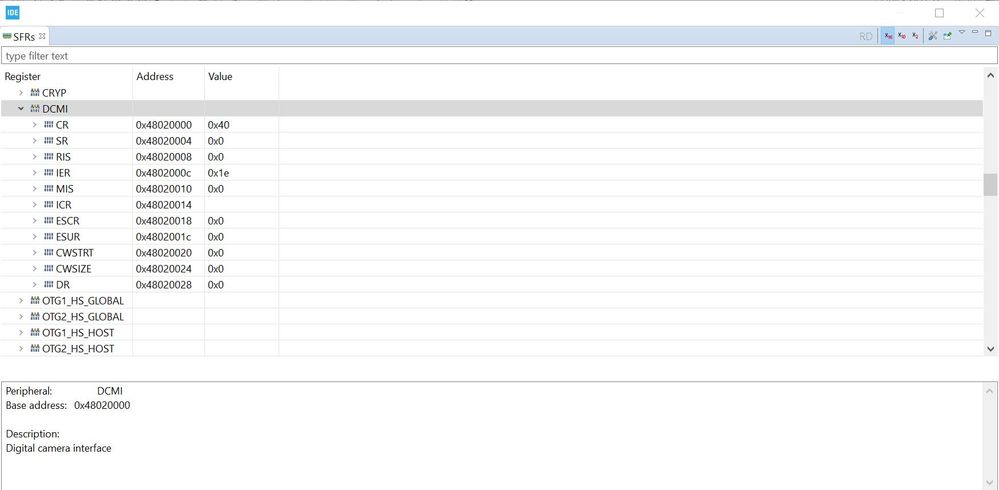

Thanks for your response. I am attaching following register values (also via zipped folder).

My compiler allocated the `frame_buff` at `0x240222c0`, which is observed also in the DMA registers.

Please notice the register values -

before request:

after request:

snapshot while in DMAError:

I noticed I get the `HAL_DCMI_VsyncEventCallback` + `HAL_DCMI_LineEventCallback` + `DCMI_IRQHandler` irq's but still, no data appending to the `frame_buff`.

Any idea what can result the problem?

Sincerely

Dan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-05-24 09:29 AM

Hi,

1)

did you try change destination for HAL_DCMI_Start_DMA?

I have problem with AXI_SRAM and SDRAM, but RAM1/2/3 works for me.

ALIGN_32BYTES(uint8_t buffer1[BUFFER_SIZE]) __attribute__((section(".RAM_D1"))); /*AXI_SRAM*/

ALIGN_32BYTES(uint8_t buffer2[BUFFER_SIZE]) __attribute__((section(".RAM_D2"))); /*SRAM1, SRAM2, SRAM3*/2)

what size of image do you want download and which format?

#define BUFF_SIZE (160*120)3)

do you have correct configuration for DCMI? PCK/VS/HS Polarity?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-05-24 02:03 PM

DMA2_S1CR is suspiciously set to byte transfer on both ports. You did not show us the FIFO control register for stream 1.

Can't this be consequence of the infamous "DMA needs to be enabled first" bug of the older CubeMX versions?

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-14 11:16 AM

Initiating the DMA before the DCMI (initialization sequence) solved the issue.

Thanks

- STM32H QSPI LL Driver in STM32 MCUs products

- STM32H745BI SPI port does not start in STM32 MCUs products

- SPI reception timeouts due to SPI_FLAG_RXP bit on STM32U575 in STM32 MCUs products

- STM32U575RITxQ SPI 3 fails at 1024 bytes or more in STM32 MCUs products

- STM32H5 SPI DMA LL Transfer Timing Issue in STM32 MCUs products