- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Embedded software

- STM32 Ethernet PTP implementation Issue (Hard Faul...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32 Ethernet PTP implementation Issue (Hard Fault)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-26 09:48 AM

Hello ,

I am trying to implement PTP (IEEE1588) on stm32f107 I have used this code for reference

"https://github.com/mpthompson/stm32_f4_ptpd" and ported it to stm32f107

Now, Everything works fine if Time stamp register bit 0 is set to "0" ,i.e..

I can see the sync and announce packets in wireshark and the program is running with 0 timestamps , below attached is the debug2 for reference.

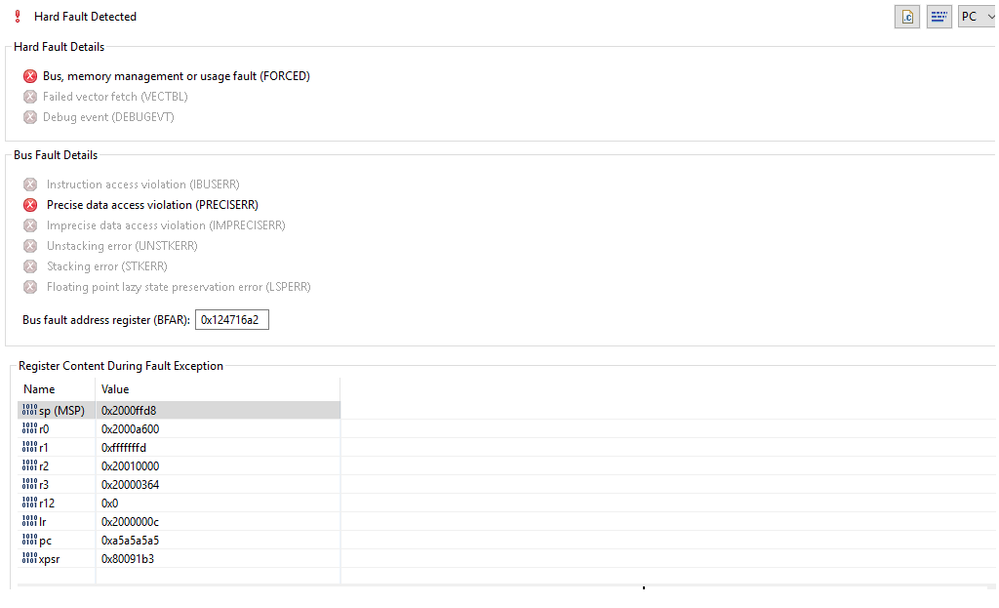

if Time stamp register bit 0 is set to "1" program halts with hardfault. with below debug 1 and attached is the image of what fault analyzer has to say.

Thanks For helping ...

Debug 1

(D 0.001348318) event POWER UP

(D 0.002258042) leaving state PTP_INITIALIZING

(D 0.003519519) entering state PTP_INITIALIZING

(D 0.004792008) manufacturerIdentity: PTPd;2.0.1

(D 0.006093251) netShutdown

Assertion "igmp_leavegroup: attempt to leave non-multicast address" failed at line 551 in ../Middlewares/Third_Party/LwIP/src/core/ipv4/igmp.c

(D 0.010608396) netInit

(D 0.011315183) initData

(V) initData: EUI48toEUI64

(D 0.012704188) initTimer

(D 0.013452584) initClock

(d 0.014147498) adjFreq 0

(d 0.014854946) bmc: m1

(D 0.015507389) leaving state PTP_INITIALIZING

(D 0.016767384) entering state PTP_LISTENING

(d 0.017966648) timerStart: set timer 3 to 3000

Problem: Success

Debug 2

D 0.000000000) event POWER UP

(D 0.000000000) leaving state PTP_INITIALIZING

(D 0.000000000) entering state PTP_INITIALIZING

(D 0.000000000) manufacturerIdentity: PTPd;2.0.1

(D 0.000000000) netShutdown

Assertion "igmp_leavegroup: attempt to leave non-multicast address" failed at li ne 551 in ../Middlewares/Third_Party/LwIP/src/core/ipv4/igmp.c

(D 0.000000000) netInit

(D 0.000000000) initData

(V) initData: EUI48toEUI64

(D 0.000000000) initTimer

(D 0.000000000) initClock

(d 0.000000000) adjFreq 0

(d 0.000000000) bmc: m1

(D 0.000000000) leaving state PTP_INITIALIZING

(D 0.000000000) entering state PTP_LISTENING

(d 0.000000000) timerStart: set timer 3 to 3000

(d 0.000000000) timerExpired: timer 3 expired

(d 0.000000000) event ANNOUNCE_RECEIPT_TIMEOUT_EXPIRES for state PTP_LISTENING

(d 0.000000000) bmc: m1

(d 0.000000000) recommending state PTP_MASTER

(D 0.000000000) leaving state PTP_LISTENING

(D 0.000000000) initClock

(d 0.000000000) adjFreq 0

(d 0.000000000) timerStop: stop timer 3

(D 0.000000000) entering state PTP_MASTER

(d 0.000000000) timerStart: set timer 2 to 1000

(D 0.000000000) SYNC INTERVAL TIMER : 1000

(d 0.000000000) timerStart: set timer 4 to 1000

(d 0.000000000) timerExpired: timer 2 expired

(d 0.000000000) event SYNC_INTERVAL_TIMEOUT_EXPIRES for state PTP_MASTER

(d 0.000000000) netSend: 0 sec 0 nsec

(d 0.000000000) issueSync

(d 0.000000000) timerExpired: timer 4 expired

(d 0.000000000) event ANNOUNCE_INTERVAL_TIMEOUT_EXPIRES for state PTP_MASTER

(d 0.000000000) netSend

(d 0.000000000) issueAnnounce

(d 0.000000000) timerExpired: timer 2 expired

(d 0.000000000) event SYNC_INTERVAL_TIMEOUT_EXPIRES for state PTP_MASTER

(d 0.000000000) netSend: 0 sec 0 nsec

(d 0.000000000) issueSync

(d 0.000000000) timerExpired: timer 4 expired

(d 0.000000000) event ANNOUNCE_INTERVAL_TIMEOUT_EXPIRES for state PTP_MASTER

(d 0.000000000) netSend

(d 0.000000000) issueAnnounce

(d 0.000000000) timerExpired: timer 2 expired

(d 0.000000000) event SYNC_INTERVAL_TIMEOUT_EXPIRES for state PTP_MASTER

(d 0.000000000) netSend: 0 sec 0 nsec

(d 0.000000000) issueSync

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-26 11:11 AM

Got to look at the faulting code.

Presumably your code faulting, not the stuff on github.

Do you have the IRQHandler set up an named properly for your platform, check stm32f1xx_it.c

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-26 11:32 AM

Hello Clive,

ETH_PTPTSCR is the register of which bit 0 is :

[image: image.png]

To my knowledge, it is not generating any interrupt and thus I don't

need IRQHandler

set up.

Please correct me if I am wrong.

Thanks & Regards,

*JAIRAJ SOLANKI*

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-26 11:36 AM

Hello Clive,

I am using stm32cubeIDE generated code with FreeRTOS(CMSIS V2) and LWIP.

Third line here is what is causing hardfault.

static void ETH_PTPStart(uint32_t UpdateMethod)

{

/* Check the parameters */

assert_param(IS_ETH_PTP_UPDATE(UpdateMethod));

/* Mask the Time stamp trigger interrupt by setting bit 9 in the MACIMR register. */

__HAL_ETH_MAC_DISABLE_IT(&heth, ETH_MAC_IT_TST);

/* Program Time stamp register bit 0 to enable time stamping. */

ETH_PTPTimeStampCmd(ENABLE); // if Uncommented hardfault occurs

//heth.Instance->PTPTSCR |= ETH_PTPTSCR_TSE ;

/* Program the Subsecond increment register based on the PTP clock frequency. */

ETH_SetPTPSubSecondIncrement(ADJ_FREQ_BASE_INCREMENT); /* to achieve 20 ns accuracy, the value is ~ 43 */

if (UpdateMethod == ETH_PTP_FineUpdate)

{

/* If you are using the Fine correction method, program the Time stamp addend register

* and set Time stamp control register bit 5 (addend register update). */

ETH_SetPTPTimeStampAddend(ADJ_FREQ_BASE_ADDEND);

ETH_EnablePTPTimeStampAddend();

/* Poll the Time stamp control register until bit 5 is cleared. */

while(ETH_GetPTPFlagStatus(ETH_PTP_FLAG_TSARU) == SET);

}

/* To select the Fine correction method (if required),

* program Time stamp control register bit 1. */

ETH_PTPUpdateMethodConfig(UpdateMethod);

/* Program the Time stamp high update and Time stamp low update registers

* with the appropriate time value. */

ETH_SetPTPTimeStampUpdate(ETH_PTP_PositiveTime, 0, 0);

/* Set Time stamp control register bit 2 (Time stamp init). */

ETH_InitializePTPTimeStamp();

/* The enhanced descriptor format is enabled and the descriptor size is

* increased to 32 bytes (8 DWORDS). This is required when time stamping

* is activated above. */

//ETH_EnhancedDescriptorCmd(ENABLE);

/* The Time stamp counter starts operation as soon as it is initialized

* with the value written in the Time stamp update register. */

}

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-26 01:41 PM

The PC/LR values in your prior post don't look valid/helpful.

Hard to diagnose with info presented. Might want to check the stack sizes, or try without the RTOS.

You need a proper Hard Fault Handler, and you need to look at the offending assembler instructions and processor registers.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-26 01:45 PM

See routines here that can provide more actionable data

You then need to disassemble the failing code, or make a determination if the failure flags on more random locations.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-31 04:35 AM

Hello,

Looks like ethernet driver is the problem.

Is there a working HAL_ETH driver for PTP applications for STM32f107 ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-04-01 05:22 AM

> To my knowledge, it is not generating any interrupt and thus I don't need IRQHandler set up.

Look carefully at ETH_MACIMR register's reset state and bit description. Read more on this specific problem here:

https://community.st.com/s/question/0D50X0000AIdSc0SQF/unwanted-interrupts-for-ethernetmac-mmc

And overall on all Ethernet related problems here:

P.S. Receiving with polling is a really poor design.

- Facing Hard fault when implementing RTOS on NUCLEO-H563 board in STM32CubeIDE (MCUs)

- [Resolved] USART Tx pin sinks rx pin. HAL UART bug? in STM32 MCUs products

- ADC with DMA and LwIP TCP: Interrupt Conflicts in STM32 MCUs Boards and hardware tools

- Getting Hard Fault Exception at -40c while using STM32F0412VET in STM32 MCUs products

- Ethernetif.c in STM32f4 cube FW_F4 V1.28 in STM32 MCUs Embedded software